# Power Drive Protection Interrupt on the TMS320C24x

Hareesh Janakiraman

Digital Signal Processing Solutions

#### ABSTRACT

The Power Drive Protection Interrupt (PDPINT) pin is a safety feature that is built into all TMS320C24x<sup>™</sup> DSPs. This feature protects the electrical drive from damage due to any electrical, mechanical or thermal abnormalities. When this pin is driven low externally, all the PWM outputs are put in a high impedance state, thereby protecting the electrical drive from further damage. A proper understanding of the functioning and limitations of the PDPINT module is necessary to realize the benefits of this feature.

|   | Contents 1 Design Problem1                       |     |  |  |  |

|---|--------------------------------------------------|-----|--|--|--|

| 1 | Design Problem                                   | . 1 |  |  |  |

| 2 | Introduction                                     | . 1 |  |  |  |

| 3 | Principle of Operation                           | . 1 |  |  |  |

|   | State of PDPINT During Reset                     |     |  |  |  |

| 5 | PDPINT Behavior in TMS320C24x Silicon            | 2   |  |  |  |

|   | Program to Check the PDPINT & PWM1 OF TMS320C24x |     |  |  |  |

|   | List of Figures                                  |     |  |  |  |

#### List of Figures

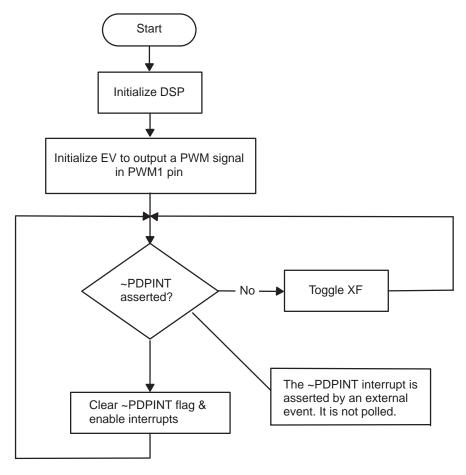

| Figure 1. Flowchart for PDPINT Validating Program |  |

|---------------------------------------------------|--|

|---------------------------------------------------|--|

### 1 Design Problem

How do I use the PDPINT pin in my design?

### 2 Introduction

The Power Drive Protection Interrupt (PDPINT) pin is a safety feature that is built into all TMS320C24x devices. This feature protects the electrical drive from damage due to any electrical, mechanical or thermal abnormalities. When this pin is driven low externally, all the PWM outputs are put in a high impedance state, thereby protecting the electrical drive from further damage. A proper understanding of the functioning and limitations of the PDPINT module is necessary to realize the benefits of this feature.

### 3 **Principle of Operation**

The PDPINT is typically connected to a current/voltage sensor or a temperature sensor to check for abnormalities in the system. Whenever the PDPINT interrupt is asserted (by an external active-low signal), the FCOMPOE bit in COMCON register changes to zero. This action puts the PWM outputs in a high impedance state. To enable the PWM outputs again, this bit must be changed to one. The PWM outputs can also be forced into a high impedance state by the user writing a zero to the FCOMPOE bit. Therefore, there are two ways to put the PWM outputs into high impedance. PDPINT has a clock independent path. This means that the PWM channels are put in the high impedance state the moment PDPINT is taken low and remains in this state as long as PDPINT is maintained low.

TMS320C24x is a trademark of Texas Instruments.

## 4 State of **PDPINT** During Reset

It is important to maintain PDPINT in high state during a power-on reset or a warm reset. i.e., the DSP should not be powered on or reset with PDPINT low. If this happens, subsequent PDPINT interrupts are not recognized. That is, even if the PDPINT pin is taken high after the device has come up and subsequently driven low, the interrupt is not recognized. In this circumstance, clearing the PDPINT interrupt flag will not help either.

It must be emphasized that the action of putting the PWM outputs in high impedance when PDPINT is active always takes place. For example, even if PDPINT is low during power-up, the PWM outputs will be still be driven into high impedance since PDPINT has a clock independent path. However, subsequent valid PDPINT interrupts will not be recognized by the core.

## 5 PDPINT Behavior in TMS320C24x Silicon

PDPINT is level sensitive in TMS320F243/F241 (Revision 2.1) silicon. Therefore multiple interrupts will be asserted if PDPINT is held low on a continuos basis. This is not the case with TMS320C242 silicon, whose PDPINT pin is (falling) edge sensitive. The example program at the end of this application note aids in understanding the edge sensitive (or level sensitive) nature of the PDPINT pin.

Figure 1. Flowchart for PDPINT Validating Program

## 6 Program to Check the PDPINT & PWM1 OF TMS320C24x

This program illustrates the behavior of PDPINT pin in 'C24x DSP. It produces an output in PWM1 Channel and aids in observing the effect of PDPINT on PWM1.PDPINT need not be enabled at the peripheral level, since it is done automatically at reset. Program normally keeps toggling the XF bit. If PDPINT is level sensitive and is asserted (driven and held low), XF toggling frequency will reduce due to the overhead in servicing the interrupt. If PDPINT is edge sensitive and is asserted (driven and held low), it will not alter the XF toggling frequency, since the interrupt will be recognized only once. However, in both cases when PDPINT is asserted, the PWM output should be put in a high impedance state, which can be verified by pulling the output high/low and monitoring the state of the pin by an oscilloscope.

```

.title " pdpint"

.include 24x.h ; 24x.h contains all the register definitions

;-----

; Vector address declarations

;______

.sect "vectors"

RSVECT B

INT1 B

; Reset Vector

START

В

GISR1

; Interrupt Level 1

INT2

B GISR2

; Interrupt Level 2

TNT3

B GISR3

; Interrupt Level 3

B GISR4

TNT4

; Interrupt Level 4

B GISR5

; Interrupt Level 5

INT5 B GISR5

INT6 B GISR6

RESERVED B PHANTOM

SW_INT8 B PHANTOM

SW_INT9 B PHANTOM

SW_INT10 B PHANTOM

SW_INT11 B PHANTOM

SW_INT12 B PHANTOM

SW_INT13 B PHANTOM

INT5

; Interrupt Level 6

; Reserved

; Neserved

; User S/W Interrupt

; User S/W Interrupt

; User S/W Interrupt

; User S/W Interrupt

; User S/W Interrupt

SW_INT13BPHANTOMSW_INT14BPHANTOMSW_INT15BPHANTOMSW_INT16BPHANTOMTRAPBPHANTOM

; User S/W Interrupt

; User S/W Interrupt

; User S/W Interrupt

; User S/W Interrupt

; Trap vector

B NMI

; Non-maskable Interrupt

NMI

;-----

; M A C R O - Definitions

_____

:----

KICK_DOG

; Watchdog reset macro

.macro

LDP #00E0h

; DP-->7000h-707Fh

SPLK #05555h, WDKEY

SPLK #0AAAAh, WDKEY

#0h ; DP-->0000h-007Fh

LDP

.endm

.text

START:

SETC INTM

; Disable interrupts

SPLK #0000h,IMR

; Mask all core interrupts

LACC IFR

; Read Interrupt flags

SACL IFR

; Clear all interrupt flags

LDP #0E0h

```

|                                                | SPLK #006Fh, WDCR ; Disable WD if VCCP=5V<br>KICK_DOG                                                                                                                                                                                                                                                  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | SPLK #0h,60h; Set wait state generator for:OUT 60h,WSGR; Program Space, 0 wait states                                                                                                                                                                                                                  |

|                                                | LDP #0E1h ; Set dual purpose pins for<br>SPLK #0FFFFh,OCRA ; PWM function<br>LDP #0h                                                                                                                                                                                                                   |

|                                                | SPLK #0001h,IMR ; Enable INT1 (for ~PDPINT)                                                                                                                                                                                                                                                            |

|                                                | LDP #EVIMRA >> 7 ; Clear all flags in EV (if set)<br>LACL EVIFRA ;<br>SACL EVIFRA ;                                                                                                                                                                                                                    |

|                                                | CLRC INTM ; Enable interrupts globally                                                                                                                                                                                                                                                                 |

|                                                | LDP #T1CON >>7 ; Generate a PWM signal in PWM1 pin<br>SPLK #0500, T1PR<br>SPLK #0250, CMPR1                                                                                                                                                                                                            |

|                                                | SPLK       #10000010000000b, COMCON         SPLK       #00000000000000b, ACTR         SPLK       #10010000010b, T1CON         LDP       #0h                                                                                                                                                            |

| LOOP2                                          | <pre>SETC XF ; Program normally keeps looping here<br/>CALL DELAY ; in LOOP2, unless interrupted by<br/>CLRC XF ; ~PDPINT. If PDPINT interrupt is<br/>CALL DELAY ; continuously asserted, then the<br/>B LOOP2 ; frequency at which XF is toggled will<br/>; be reduced, due to the ISR overhead</pre> |

| DELAY<br>LOOP                                  | LAR AR0,#0FFFFh; The DELAY loop merely provides a delay<br>RPT #10h ; for XF toggling.<br>NOP<br>BANZ LOOP<br>RET                                                                                                                                                                                      |

| GISR1:                                         | LDP #PIVR >>7 ; ISR for PDPINT. Merely clears the<br>LACL PIVR ; PDPINT flag<br>LDP #EVIMRA >> 7<br>LACL EVIFRA<br>SACL EVIFRA<br>CLRC INTM<br>LDP #0h<br>RET                                                                                                                                          |

| GISR2:<br>GISR3:<br>GISR4:<br>GISR5:<br>GISR6: | RET<br>RET<br>RET<br>RET                                                                                                                                                                                                                                                                               |

| PHANTOM                                        | KICK_DOG ;Resets WD counter<br>B PHANTOM                                                                                                                                                                                                                                                               |

|                                                | .END                                                                                                                                                                                                                                                                                                   |

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated