# **CoolMOS<sup>TM</sup> Introduction** and **Datasheet understanding**

Ryan Zhou Ryan.zhou@infineon.com Power management & Supply Discretes Infineon Technologies China

Never stop thinking

## Introducing CoolMOS<sup>™</sup>

**Datasheet Understanding**

# Introducing CoolMOS<sup>™</sup>

Datasheet Understanding

# CoolMOS<sup>™</sup> Series & History

**S5 series**: the first series of CoolMOS<sup>™</sup>, market entry in 1998 slow switching, close to conventional MOSFET, Vth 4.5 V, gfs low, Rg high design-in in high power SMPS only

**C3 series**: the third series of CoolMOS<sup>™</sup>, market entry in 2001 the "working horse" of the portfolio, fast switching, symmetrical rise/fall time @10 V Vgs, Vth 3 V, gfs high, Rg very low design-in into all CoolMOS<sup>™</sup> segments

**CFD series**: the fourth series of CoolMOS<sup>™</sup>, market entry in 2004, fast body diode, Qrr 1/10th of C3 series, Vth 4 V, gfs high, Rg low pecific for phase-shift ZVS and DC/AC power applications

**CP series**: the fifth series of CoolMOS<sup>™</sup>, market entry in 2005, ultra low Rdson, ultra low gate charge, very fast switching Vth 3 V, gfs very high, internal Rg very low

**C6/E6 series**: the sixth series of CoolMOS<sup>™</sup>, launched in 2009 and 2010 respectively as the sixth CoolMOS<sup>™</sup> technology is planned to be the successor of C3

CFD2 series: the new technology CoolMOS<sup>™</sup> of the successor of CFD, lower Qrr and trr, will come at the begin of 2011

# Roadmap of HV MOSFET

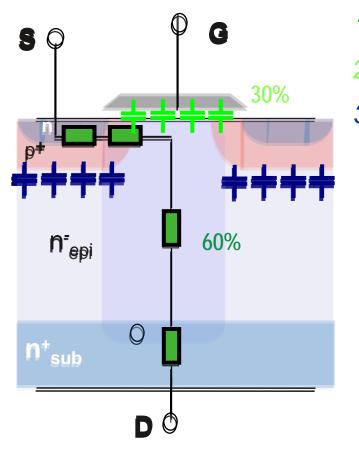

# Losses come from

- 1. Rdson: 60% conduction loss

- 2. Delay in on/off (Qg..):30% switching loss

- 3. (Dis)Charge Cds Cap.: 10% C<sub>oss</sub> loss

# To make it better:

- 1. Better conductivity →Lower Rdson

- 2. Faster switching → lower Qg

- 3. Lower capacitances →Lower Coss,etc

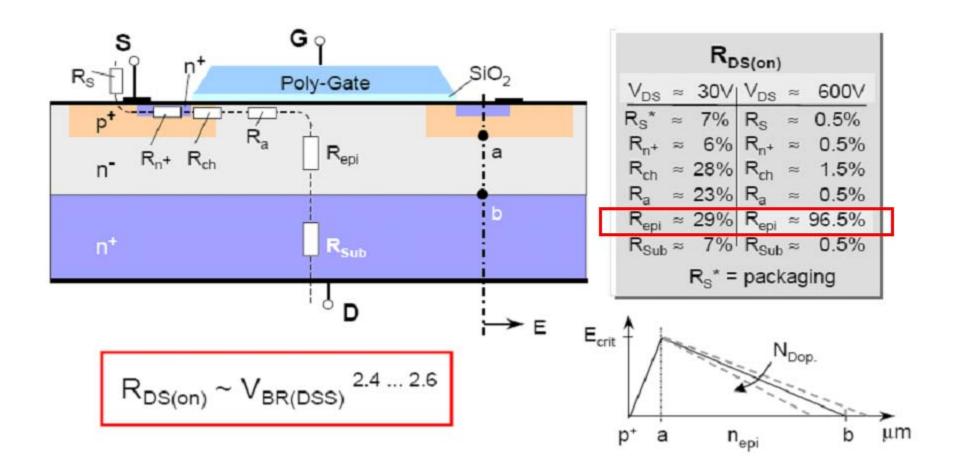

# Resistance – Rdson, distribution of MOSFET

# 96.5% of R<sub>DS(on)</sub> for high voltage standard MOSFET determined by the epitaxial resistance

12-Feb-11

Copyright © Infineon Technologies 2006. All rights reserved.

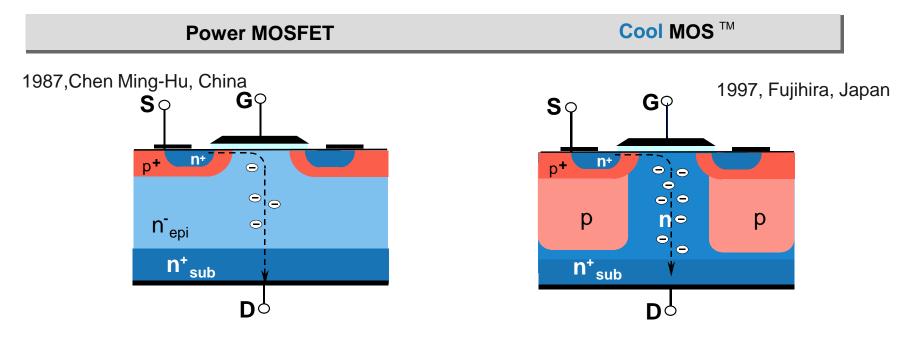

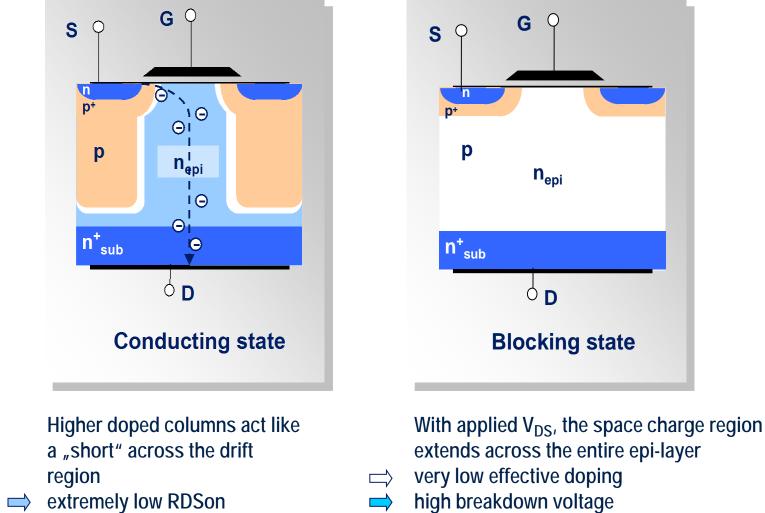

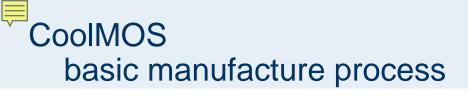

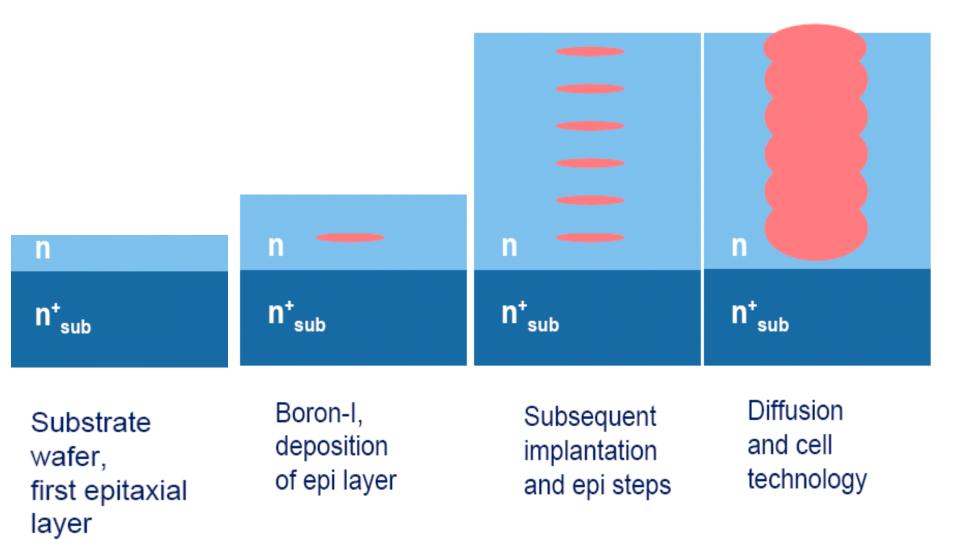

# **Super Junction Theorem**

By controlling the <u>degree of doping</u> and the <u>thickness of</u> <u>these layers</u>, according to the SJ theory, this structure operates as a pn junction with low on-resistance and high breakdown voltage.

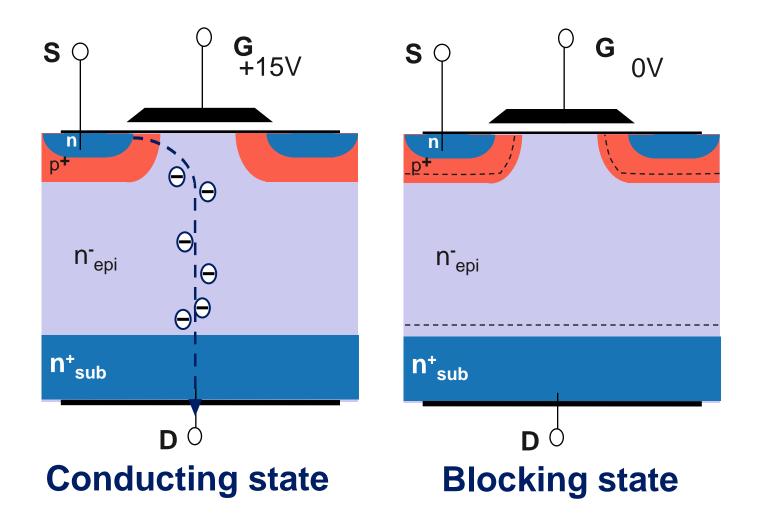

# Standard MOSFET operating principle

# **CoolMOS** operating principle

high breakdown voltage

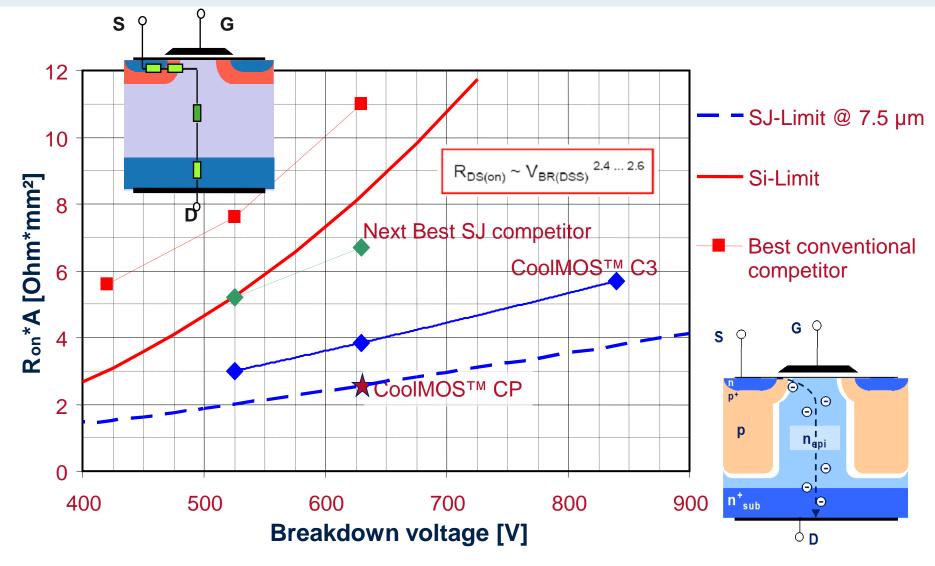

# CoolMOS : Lowest area-specific Rds(on)

Conducting state

12-Feb-11

Introducing CoolMOST

## **Datasheet Understanding**

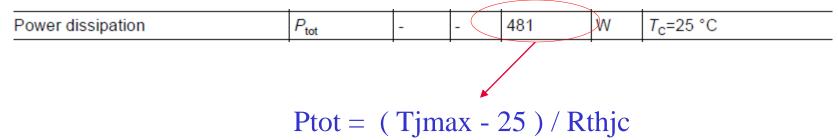

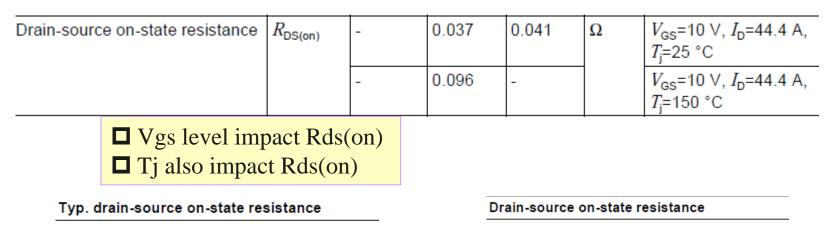

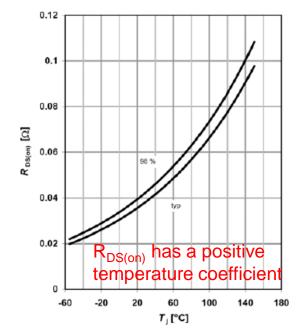

# Current is calculated base on Tjmax, Rdson@Tjmax, Rth(jc)!

| Parameter                  | Symbol         | Values |      |      | Unit | Note / Test Condition  |  |

|----------------------------|----------------|--------|------|------|------|------------------------|--|

|                            |                | Min.   | Тур. | Max. | ]    |                        |  |

| Continuous drain current1) | I <sub>D</sub> | -      | -    | 77.5 | А    | T <sub>c</sub> = 25 ℃  |  |

|                            |                |        |      | 49   |      | T <sub>c</sub> = 100°C |  |

$$P_{tot} = R_{on(@Tjmax)} * I^{2}$$

$$P_{tot} * R_{thJC} = T_{jmax} - T_{c}$$

$$I = (T_{jmax} - T_{c})/R_{on(@Tjmax)/}R_{thJC}$$

That's why we just put Rds(on) not Id into P/N naming: IPW60R041C6

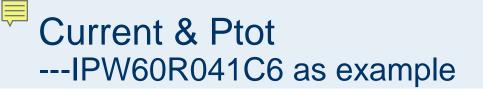

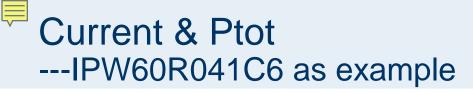

# Ptot calculated as well:

# Junction temperature

Never exceed Tj max (150 / 175 deg C) at operation, otherwise, will cause MOSFET failure.

|                                   | 1                                 |         |    |

|-----------------------------------|-----------------------------------|---------|----|

| Operating and storage temperature | Τ <sub>j</sub> , Τ <sub>stg</sub> | -55 150 | °C |

Copyright © Infineon Technologies 2006. All rights reserved.

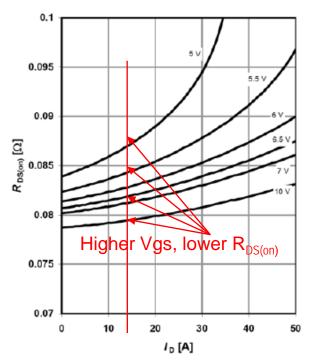

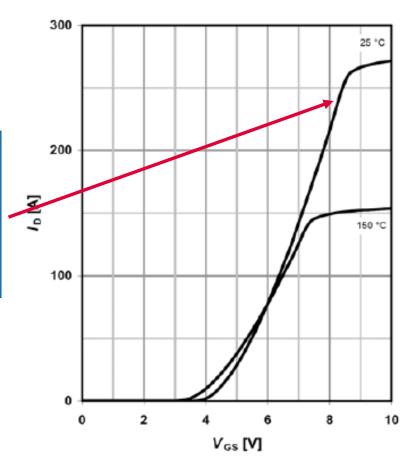

# **Transfer characteristics**

This value is the max current capability of chip inside, which is much larger than nominal current Ids (77.5A for IPW60R041C6)

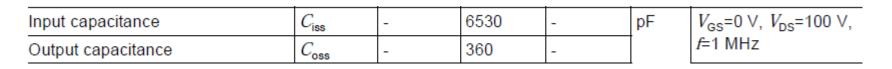

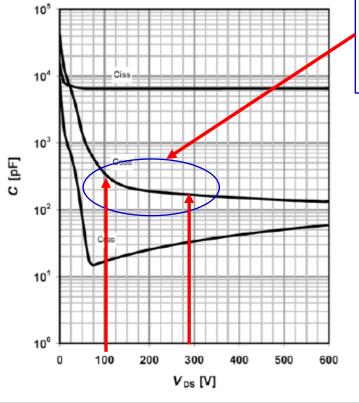

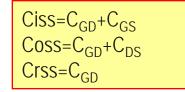

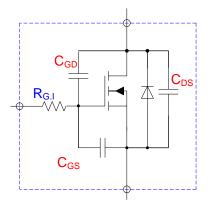

# **Capacitive parameters**

Capacitance is not fixed ! Vary with Vds ! Not recommend for calculation

C=f( $V_{DS}$ );  $V_{GS}$ =0 V; f=1 MHz

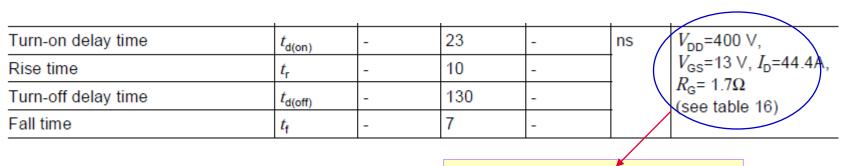

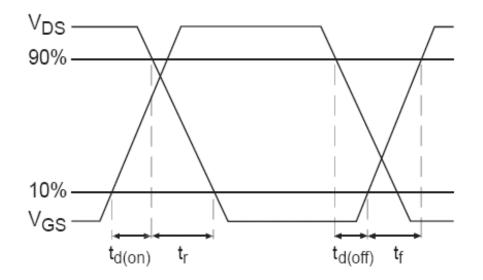

# Switching time td(on) / tr / td(off) / tf

Only recommended value at giving condition

### Switching time definition

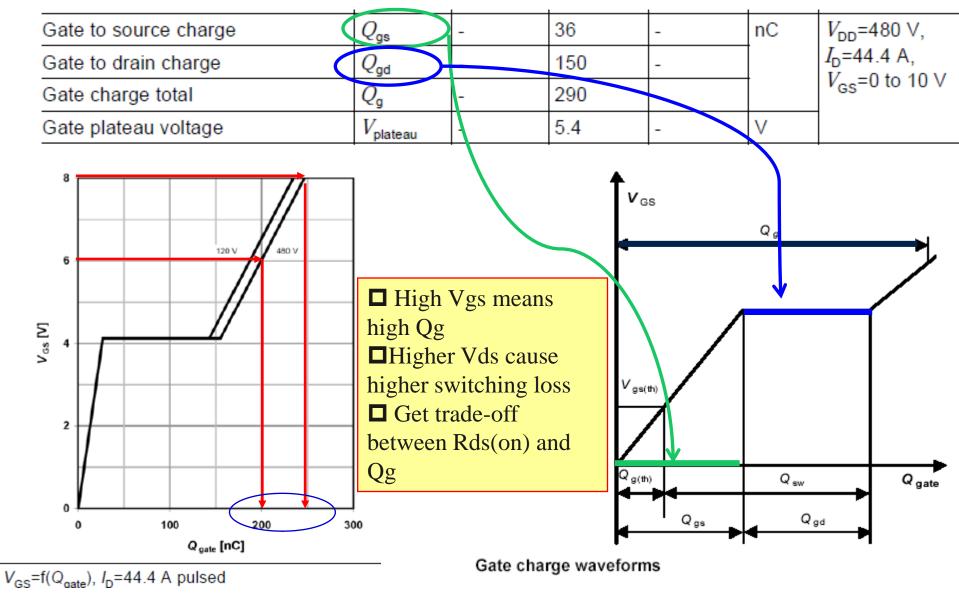

# Gate charge & plateau voltage

<sup>12-</sup>Feb-11

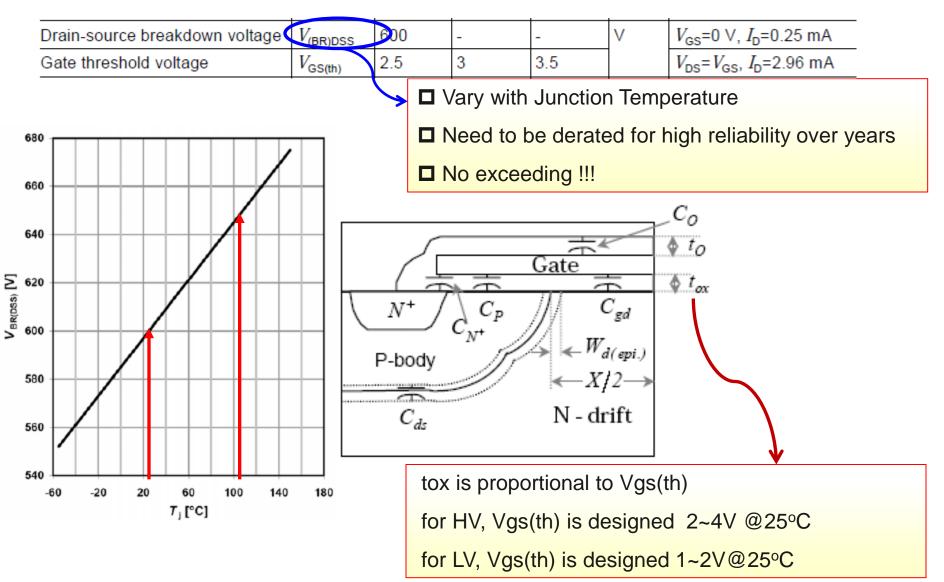

# Breakdown voltage and Gate threshold voltage

infineon

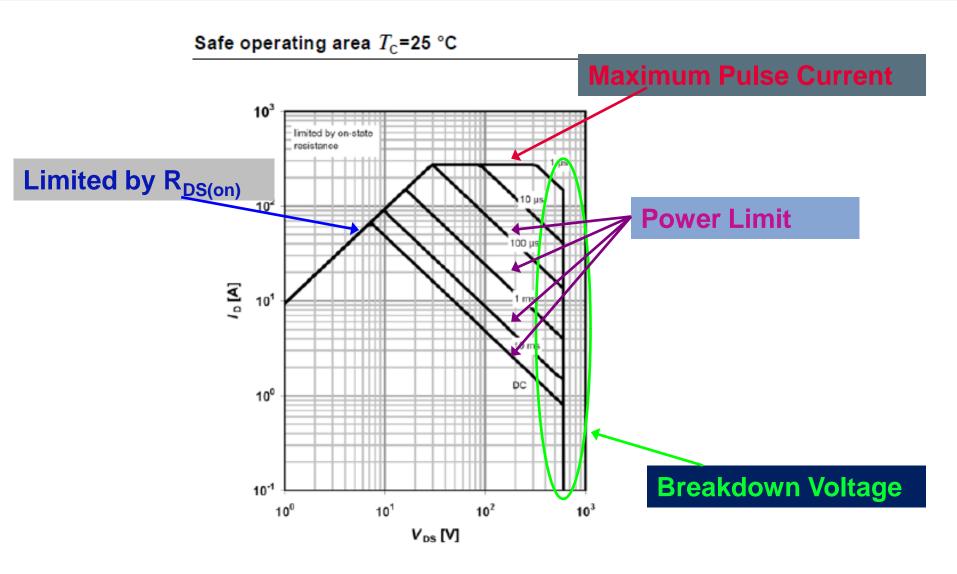

# **MOSFET SOA**

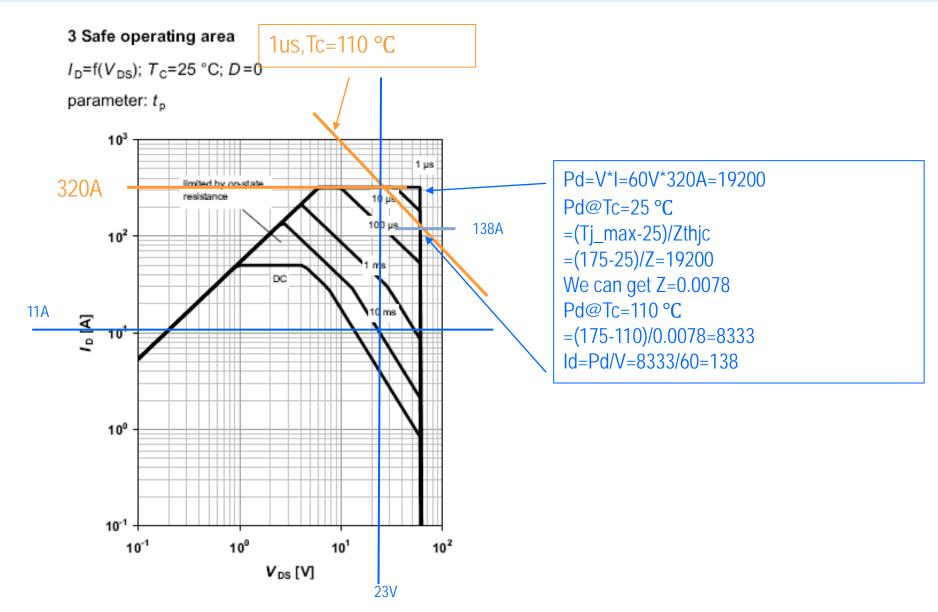

# How to Convert 25 °C to 110 °C SOA

Ę

Page 23

| Thermal resistance, junction - case       | R <sub>thJC</sub>   | - | - | 0.26 | °C/W |        |

|-------------------------------------------|---------------------|---|---|------|------|--------|

| Thermal resistance, junction -<br>ambient | $R_{\mathrm{thJA}}$ | - | - | 62   |      | leaded |

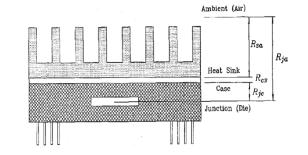

$\square$  Practically,  $R_{thJC}$  is not the key concern in the application.

```

\Box The system thermal is limited by R<sub>thJA</sub>:

```

```

R_{thJA} = R_{thJC} + R_{thCS} + R_{thSA}

```

```

Obviously, R<sub>thJA</sub>>>R<sub>thJC</sub>

```

**\Box** Thermal rise:  $\triangle T = P_{loss} * R_{thJA}$

```

Effort should concentrated on how to reduce R<sub>thJA</sub>!

```

Copyright © Infineon Technologies 2006. All rights reserved.

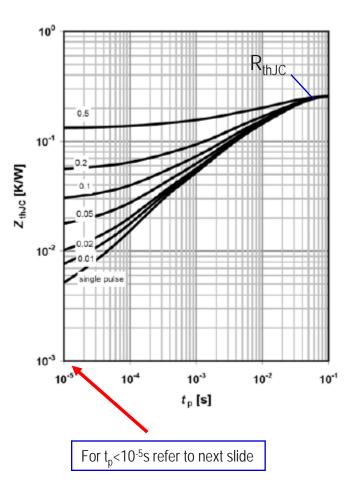

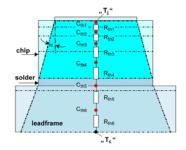

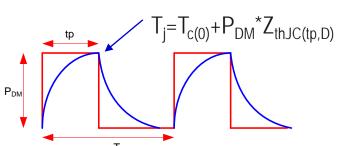

# Thermal impedance

Use Z<sub>thJC</sub> to calculate the instantaneous Tj

With longer tp, Z<sub>thJC</sub> turn to R<sub>thJC</sub>

Can be used directly for rectangular power curve

# **Transient thermal impedance**

### 4 Max. transient thermal impedance

$Z_{thJC}=f(t_p)$

parameter: D=t<sub>p</sub>/T

$Z_{thJC}$  is given for pulse widths of as low as tp=10uS.If the  $Z_{thJC}$  for a shorter pulse width is required, it can be calculated from equation below:

$$\frac{R_{th(tp1)}}{R_{th(tp2)}} = \sqrt{\frac{tp1}{tp2}}$$

Example

For tp=100ns D=0.1

$$Z_{thJC}$$

=?

Since tp=10us D=0.1  $Z_{thJC}$ =0.12 (K/W)

Thus

$$Z_{\text{thJC (at tp=100ns)}} = \sqrt{\frac{100n}{10u}} \cdot 0.12 = 0.012(K/W)$$

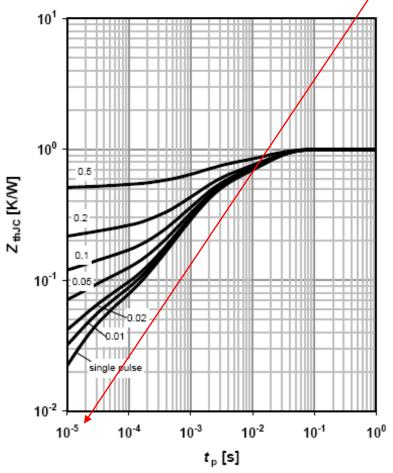

# dv/dt

Recommended value, which consideration of not trigger error turn on at gate side. **Not a maxim rating** as breakdown voltage. It's decided by actual application.

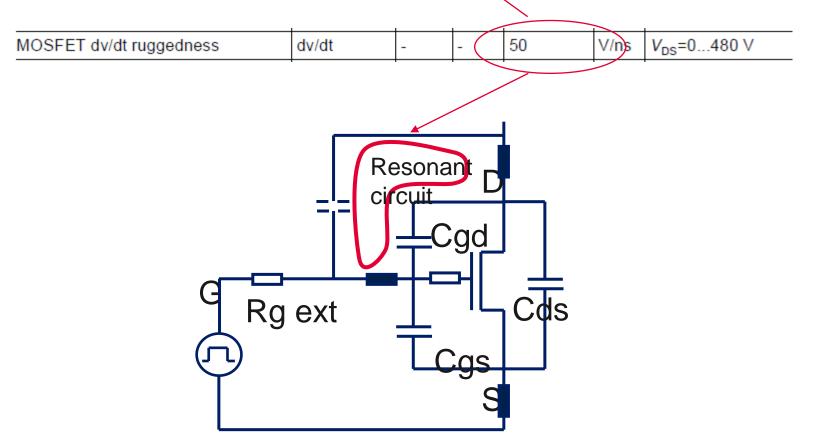

# Body diode

| Continuous diode forward current                                                                                                                                                                                          | I <sub>S</sub>       | - |     | 67.2 | А    | <i>T</i> <sub>c</sub> =25 °C                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---|-----|------|------|--------------------------------------------------------------------------------------|

| Diode pulse current <sup>2)</sup>                                                                                                                                                                                         | I <sub>S,pulse</sub> | - |     | 272  | А    | <i>T</i> <sub>c</sub> =25 °C                                                         |

| Reverse diode dv/dt <sup>3)</sup>                                                                                                                                                                                         | dv/dt                | - | -// | 15   | V/ns | $V_{\text{DS}}$ =0400 V, $I_{\text{SD}} \le I_{\text{D}}$ ,<br>$T_{\text{j}}$ =25 °C |

| Maximum diode commutation speed <sup>3)</sup>                                                                                                                                                                             | di <sub>f</sub> /dt  | - | -   | 300  | A/µs | (see table 18)                                                                       |

| <ol> <li>Limited by T<sub>j,max</sub>. Maximum duty cycle D=0.75</li> <li>Pulse width t<sub>p</sub> limited by T<sub>j,max</sub></li> <li>Identical low side and high side switch with identical R<sub>G</sub></li> </ol> |                      |   |     |      |      |                                                                                      |

Same as Id & Idpulse, sometimes derating applied.

Limited by commutation capability of body diode

# **Reverse diode characteristics**

|                               |                        |   | ••• |   |    |                                                      |

|-------------------------------|------------------------|---|-----|---|----|------------------------------------------------------|

| Diode forward voltage         | $V_{SD}$               | - | 0.9 | - | V  | V <sub>GS</sub> =0 ∨, <i>I</i> <sub>F</sub> =44.4 A, |

|                               |                        |   |     |   |    | <i>T</i> <sub>j</sub> =25 °C                         |

| Reverse recovery time         | <i>t</i> <sub>rr</sub> | - | 950 | - |    | V <sub>R</sub> =400 ∨, I <sub>F</sub> =44.4 A,       |

| Reverse recovery charge       | Q <sub>rr</sub>        | - | 32  | - | μC | d <i>i</i> <sub>F</sub> /d <i>t</i> =100 A/µs        |

| Peak reverse recovery current | Irrm                   | - | 62  | - | Α  | (see table 18)                                       |

# **Reverse diode characteristics**

# What is the Avalanche Breakdown?

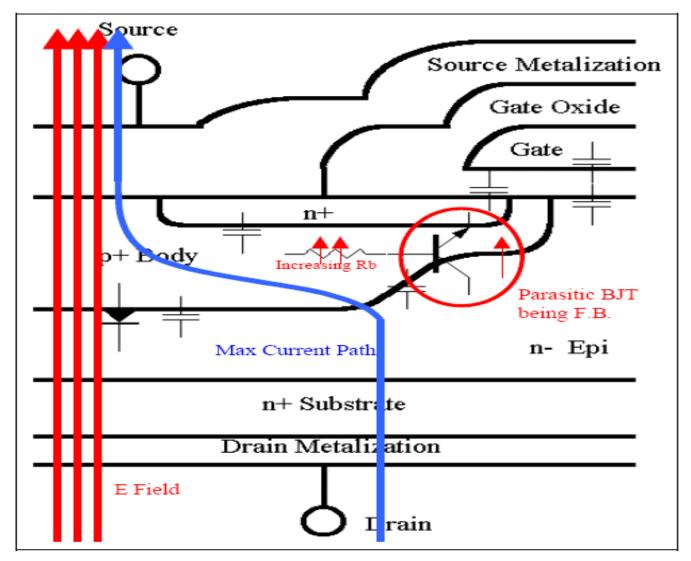

# Power MOSFET cross section under Avalanche

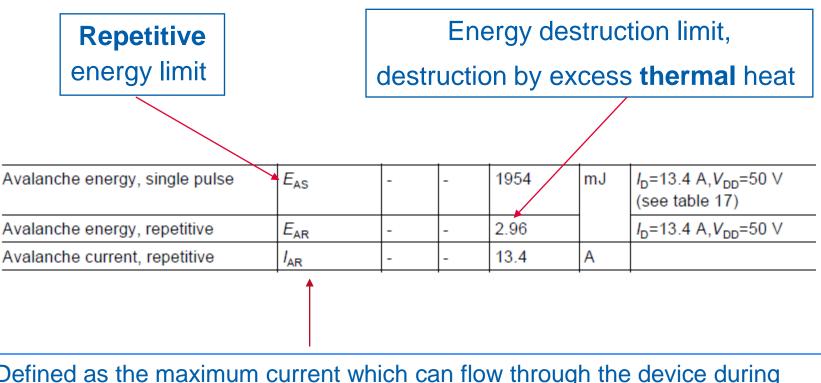

# How do we specify avalanche?

Defined as the maximum current which can flow through the device during avalanche operation **without BJT latching**.

All the avalanche operations (single / repetitive) should be below this value!

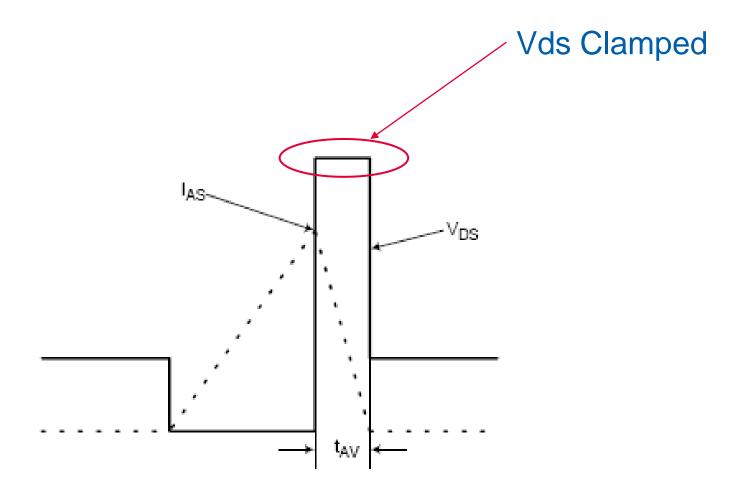

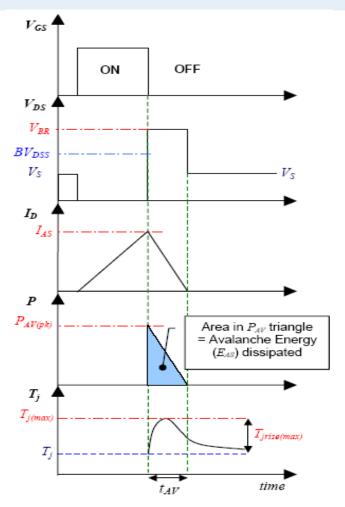

# Avalanche waveform

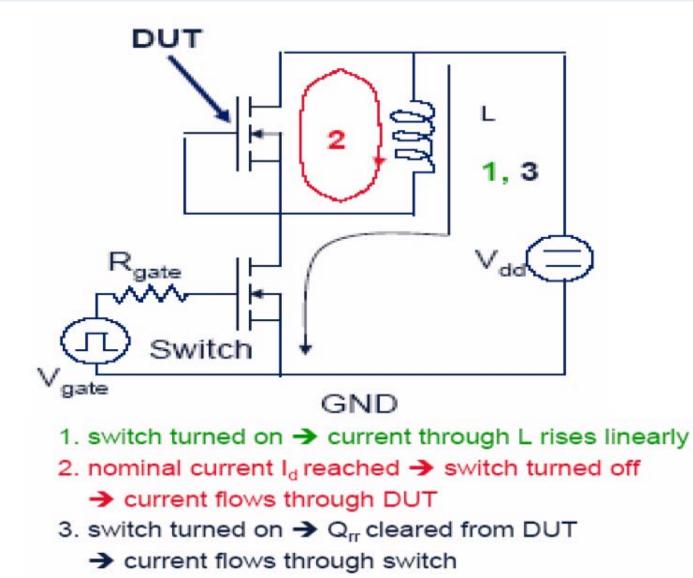

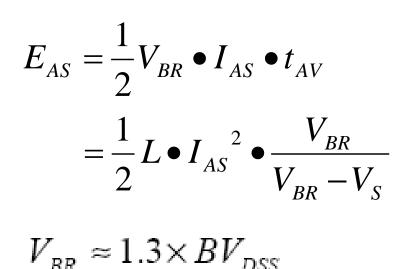

# Single avalanche

L: Magnetic component which provide the avalanche energy

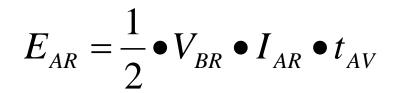

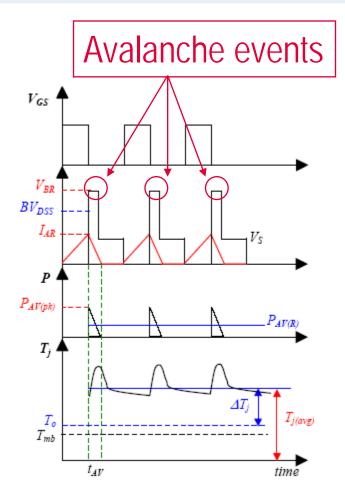

# **Repetitive avalanche**

# We commit. We innovate. We partner. We create value.

Never stop thinking