# 基于 TMS320F2812 级联式多电平变频器 控制系统的设计

丁衡龙,欧阳红林,丁伟

(湖南大学 电气与信息工程学院,湖南 长沙 410082)

摘要:级联式多电平变频器因其众多的优点,在高压变频调速领域有着广泛的应用。提出了一种基于 DSP 芯片 TMS320F2812,结合 FPGA 的新型控制系统的软硬件设计。硬件电路包括底层驱动电路、通讯模块等,软件部分给出了主程序及底层控制程序的流程图。在此设计基础上构建了实验平台。实验结果表明采用该种设计的多电平变频器的性能是十分优越的。

关键词:级联式多电平变频器;数字信号处理器;软硬件设计

中图分类号:TM921

文献标识码:A

## Design of Control System Used for Cells Cascaded Multilevel Converter Base on TMS320F2812

DING Heng-long, OUYANG Hong-lin, DING Wei

(College of Electrical and Information Engineering, Hunan University, Changsha 410082, Hunan, China)

Abstract: Cells cascade multilevel converters has extensive application in the high voltage variable frequency modulated speed system for its numerous advantages. The hardware/software design of the control system was put forward based on DSP TMS320F2812 combining FPGA. The hardware includes low level driver circuit and the communication module, the software includes the flow chart of the main programe and the low level control programe. The experimental platform was build based on the design. The results, show that the cells cascade multilevel converter adopting this method has excellent characteristics.

Key words: cells cascade multilevel converter; digital signal processor(DSP); hardware/software design

## 1 引言

与传统的二电平变频器相比,多电平变频器 具有3个主要优点:1)由于功率器件串联使用,单 个器件耐压降低,可以安全地提升整个系统输出 功率;2)单个器件耐压降低使输出 dv/dt 减小;3) 多个电平的输出合成的正弦波中谐波成分减 少[1]。级联式多电平变频器采用若干低压 PWM 功率单元相串联的方式来实现直接高压输出,对 电网谐波污染较小,电流谐波含量较低,输入功率 因数较高,并且不必采用输入谐波滤波器和功率 因数变换器,在高压大功率领域应用较为广泛<sup>[2]</sup>。 本文在介绍级联式多电平变频器拓扑结构的基础 上,提出了一种基于 DSP 芯片 TMS320F2812 的 控制系统的设计方案,由于涉及到 18 个功率单元 的 36 路 SPWM 控制信号的产生,目前还没有哪个型号的控制器能够同时生成如此数量的控制信号,所以该系统采用了 DSP 与 FPGA 相结合的控制方式。其中 DSP 主控制器完成数据的采集、人机交互、通讯控制、SPWM 信号的计算及保护等工作,而 FPGA 用来产生 36 路 SPWM 控制信号。整个控制系统设计包括硬件和软件的设计,并得到了实验结果。

## 2 级联式多电平变频器

级联式多电平逆变器拓扑的每一相都采用多个低压小功率的逆变单元,将它们串联以得到高压输出,每个逆变单元都相互独立且采用独立的低压直流电源供电,因此开关器件上的电压应力很小,模块化程度高,易于扩展和控制,可靠性好。

基金项目:湖南省科学技术厅科技计划(06CK3005)

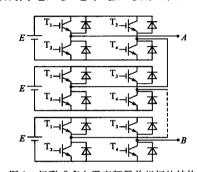

其典型结构是采用 H 桥逆变器作为逆变单元串联而成,拓扑结构如图 1 所示[3],每个单相 H 桥逆变器就是一个单相全桥逆变器,它不存在直流电容分压的均压问题。级联式多电平逆变器的主开关器件的耐压,被限定在向它所在基本功率单元供电的独立直流电源电压上,多个由独立直流电源供电的基本功率单元的交流输出侧串联叠加,就可以得到高压多电平电压输出。多电平逆变器的合成原理就是将载波三角波经过移相,并采用 SPWM 控制的 H 桥逆变单元直接串联叠加,而合成高电压多电平电压波形的。

图 1 级联式多电平变频器单相拓扑结构 Fig. 1 The single-phase topological structure of the cells cascade multilevel converters

# 3 控制系统硬件设计

#### 3.1 DSP 控制器

在该变频器的控制系统中,DSP采用 TI 公 司最新的 TMS320F2812 作为核心控制器。 TMS320F2812 是美国德州仪器公司最新研制的 数字信号处理器,面向自动控制、工业自动化、最 优网络的第一款有片内 FLASH,工作频率达到 150 MHz的 32 位 DSP 芯片。TMS320F2812 最 高主频 150 MHz,保证了处理信号的快速性和实 时性,高速的信号可以提供实时的位置信息,保证 控制信号响应的快速性。TMS320F2812 采用经 典的哈佛总线结构,利用多总线在存储器、外围模 块和 CPU 之间转移数据。程序读总线有 22 根地 址线和 32 根数据线,数据读写数据线都是 32 位, 这种多总线结构使得它可以在一个周期内并行完 成取指令、读数据和写数据,同时它也采用了指令 流水线技术,使得信号的处理速度明显提高。单 个的 TMS320F2812 芯片有 18K RAM, 128K FLASH,16 通道的 PWM,16 通道 12 位 ADC,3 个定时器,通讯接口有 CAN, McBSP, SPI, 2 个 SCI,充分保证了通讯的方便<sup>[4]</sup>。

DSP 接口电路有三相电流的模拟信号输入

接口、开关量输入/输出接口电路、同 FPGA 的数据传输接口电路、通讯模块的接口电路、扩展的程序和数据接口电路等。

## 3.2 FPGA 控制电路

FPGA 芯片采用可编程芯片制造商 Altera 公司的 FPGA 芯片,其可靠性高,国内应用范围广,供应及时,开发工具多,如 MaxPlus II、Quartus II 都是其著名的集成开发软件。

在芯片选型和实现方案方面选用扫描法方案,其原理是在由 RAM 保存所有通道的触发时间,在每个时间分辨期内,读出每个 HSO 通道的触发时间,与当前时间比较,触发相应的通道。使用 FPGA 的嵌入式 RAM,所有通道使用同一个计时器和比较器,最大限度实现了硬件资源的共享,缺点是由于需要对每个通道扫描,时间分辨率较低,经过仔细的设计,能达到 2 μs 的时间分辨率,经过论证,可以满足变频器的设计要求。经过对资源需求进行分析论证和市场供货情况,选用了EMP10K20TC144,该芯片应用比较成熟,价格适中,供应可靠,另外,其后续的可替代芯片也很多,经过严格的时序分析设计,其触发时间分辨率可以达到 2 μs,完全满足高压变频器的设计要求。

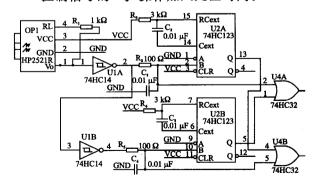

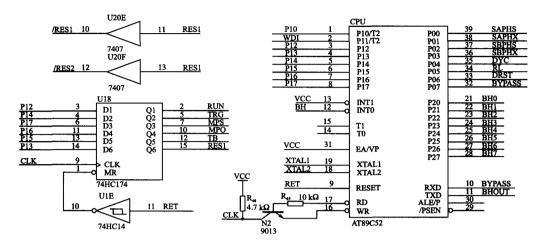

#### 3.3 底层驱动电路

驱动控制板通过光纤接口接受 SPWM 控制信号,并进行反相后生成两路控制信号,如图 2 所示。图 2 中 HP2521R 为光纤接口,其输出信号经 74HC14 反相后得到两路对称的 SPWM 控制信号。74HC123 可以产生一高电平的脉冲信号,脉冲的宽度通过调整电阻  $R_3$ ,  $R_4$  和电容  $C_2$ ,  $C_3$  的大小进行调整。该脉冲通过 74HC32 与 SPWM 控制信号的"与"操作加入死区时间。

图 2 SPWM 信号输入调整电路

Fig. 2 The input tuning circuit of the SPWM signals

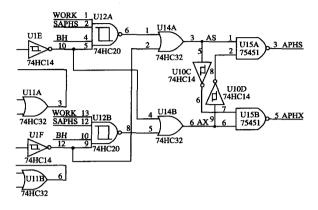

为了对功率器件进行有效的保护,比较对同 一桥臂的两路控制信号进行互锁,如图 3 所示。 其中信号"WORK"来自与底层控制板上的控制器89C52,用来开通 SPWM 控制信号;信号"SAPHS", "SAPHX"为功率器件的保护信号,"BH"为所有保护信号的"与"。最后生成的两路 SPWM 控制信号通过74HC14进行互锁,以保证输出信号

图 3 SPWM 信号输出互锁电路

Fig. 3 The output interlock circuit of the SPWM signals

"APHS"和"APHX"不会同时出现高电平。

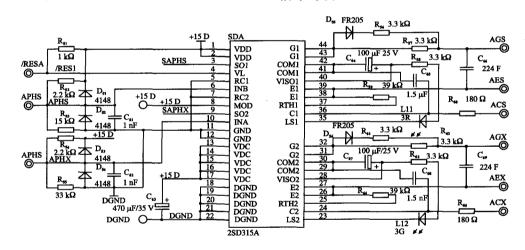

IGBT 的驱动模块选择 2SD315A,该模块可 驱动 1 700 V,1 200 A 以下的 IGBT,该 IGBT 驱 动模块的隔离性能好,保护功能强,抗干扰能力 强,使用简单。其电路连接图如图 4 所示,信号 "/RESA"为该模块的复位信号输入端,该信号由 驱动板上的控制器 89C52 控制;信号"APHS"和 "APHX"为同一桥臂上下 2 个 IGBT 的控制信 号;输出端共有2组6个信号端,"AGS"、"AES"、 "ACS"分别接上桥臂 IGBT 的门极、发射极和集 电极, "AGX"、"AEX"、"ACX"分别接下桥臂 IG-BT 的门极、发射极和集电极。当 IGBT 发生过流 保护时,其集电极与发射极的电压将升高,则 2SD315A 模块内部产生保护信号,对应管脚的保 护信号输出的电平将该路控制信号封锁,同时信 号"BH"也变为低电平将该功率模块的所有控制 信号封锁。

图 4 IGBT 驱动模块

Fig. 4 The drive module of IGBT

为了对每个功率模块进行监控,在每个功率模块的驱动板上均设有单片机 AT89C52 控制器,以方便进行集中控制,如图 5 所示。其中输入信号"DRST"是上位 DSP 控制器经光纤传送过来的控制信号,用来启动该功率单元;信号"BY-PASS"为 DSP 传送过来的旁路信号,表明给功率模块需要旁路输出;驱动模块 2SD315A 输出的 4 路过流保护信号也通过 P0 口送入单片机;P1 口的输出信号经 74HC14 后发送控制信号,用来控制主电路的旁路经晶闸管、充电晶闸管、放电晶闸管等;P2 口通过对发光二极管的控制,显示该功率模块的工作状态。

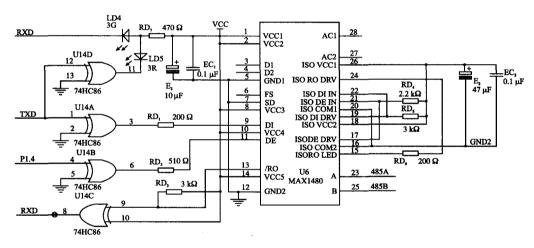

### 3.4 通讯模块

通讯模块采用了基于 MAX1480 在 RS485 通讯模式,如图 6 所示。其中"P1.4"为控制信号,该信号通过与"地"信号的"异或"操作控制 MAX1480 的使能管脚"DE"。当"P1.4"为高电平时,"DE"也为高电平,使能 MAX1480 工作,"A"和"B"的状态有"DI"控制;否则脚"A"和"B"处于高阻抗状态。"TXD"为控制器的发送信号,当"TXD"为高电平时,"DI"为高电平,则"A"为高电平,"B"为低电平;否则"A"为低电平,"B"为高电平。当"DI"为低电平时,MAX1480 处于接受状态。当"A"比"B"高 200 mV 时,"/RO"为低电

平,通过一个异或门时得信号"RXD"变为高电平,这样就可以与外部传送过来的信号保持一

致。同时,通过两个发光二极管指示电路的工作状态。

图 5 AT89C52 电路

Fig. 5 The AT89C52 circuit

图 6 通讯模块

Fig. 6 The communication module

# 4 控制软件设计

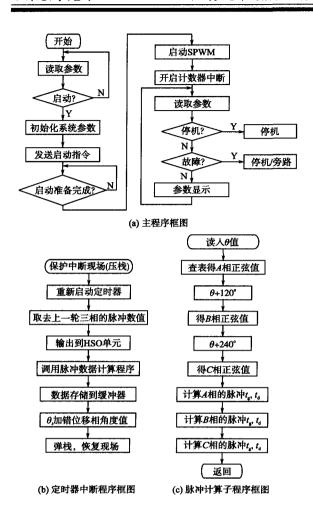

控制系统涉及到数据采集、算法实现、通讯等 多种功能,合理安排控制程序的结构是非常重要 的。整个控制程序可以划分为: DSP 主程序、FP-GA 控制程序和底层 89C51 控制程序等几部分。

## 4.1 DSP 主程序

该部分程序,主要完成变频器系统的启动与停止控制、系统参数的初始化、通讯、系统的监控与保护等功能,其程序流程图如图 7a 所示。在系统上电后,DSP 控制器首先通过对键盘的读取,获得系统的运行频率、启动时间、停止时间等参数。然后等待收到系统启动指令后,程序才进入

下一步运行。主程序在完成正弦调制波的频率、三角载波的频率和调制比的初始化后,给每个功率单元的控制器 AT89C52 发出启动准备指令,然后等待所有功率单元控制器的答复。在确认所有功率单元完成启动准备工作后,启动 SPWM 计算程序,开启计数器中断,程序进入循环工作状态,等待中断的发生。同时读取电压、电流和功率单元的状态,进行实时显示。

在计数器中断程序中,DSP 控制器完成 SP-WM 算法的数值计算,针对不同的功率单元,计算其控制信号的导通时刻和关断时刻,送给 FP-GA。同时,正弦调制波的初始相位增加,其流程图如图 7b、图 7c 所示。

图 7 DSP 主程序流程图

Fig. 7 The DSP main program flowchart

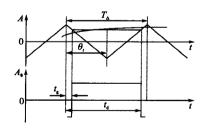

在 SPWM 的计算过程中,由于三角波和正弦 波的相交点的求解是一组超越方程,SPWM 的实时计算采用规则采样法,其原理如图 8 所示。

图 8 对称规则采样法原理图

Fig. 8 The schematic diagram of the sampling method of the symmetry principle

以每个三角载波的波谷时刻所对应的正弦波值作一条水平直线,该直线与三角载波的交点即为 SPWM 的导通时刻和关断时刻。图 8 中  $\theta_i$  是三角波中点采样时刻的角度值, $T_s$  是三角波的周期,M 是调制比,则有:

$$\begin{cases} t_{\rm g} = \frac{T_{\rm s}}{4} (1 - M \sin \theta_{\rm i}) \\ t_{\rm d} = \frac{T_{\rm s}}{4} (3 + M \sin \theta_{\rm i}) \end{cases}$$

(1)

假设该组时间为功率单元左桥臂的上桥臂功率器件的 SPWM 控制信号,采用同相控制算法时左右桥臂的正弦调制波的相位相反,所以右上桥臂功率器件的 SPWM 控制信号可以表示为

$$\begin{cases} t_{\rm g} = \frac{T_{\rm s}}{4} (1 + M \sin \theta_{\rm i}) \\ t_{\rm d} = \frac{T_{\rm s}}{4} (3 - M \sin \theta_{\rm i}) \end{cases}$$

(2)

由于 B 相和 C 相仅与 A 相的正弦调制波的相位不同,但是对于的三角载波完全相同,所以通过改变正弦调制波的角度就可以分别计算出其不同功率单元的导通和关断时间。

#### 4.2 FPGA 控制程序

在 FPGA 内部设置了一个 16 位的计数器进行循环计数,且该计数器每位代表的实际时间同DSP 控制器内部的计数器完全相同。另外 FP-GA 内部还设有多个寄存器,记录每个上桥臂功率器件的导通和关断时间。FPGA 从 DSP 获得导通和关断时间后,将该时间加上当时的计数器的数值后,存入相应的寄存器。FPGA 内部的比较模块将计数器的当前计数值不断与寄存器的值进行比较,实现对应管脚高低电平状态的控制,产生所有功率单元桥臂功率器件的 SPWM 控制信号。

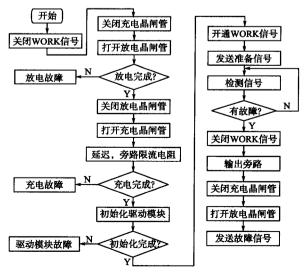

#### 4.3 底层控制程序

底层控制程序流程图如图 9 所示,该部分核心控制器为89C52,一方面从上位控制器中接受

图 9 底层控制程序流程图

Fig. 9 The bottom control program flowchart

指令,来启动、旁路或关闭相应的功率单元;另一方面,通过对直流母线电压和驱动模块保护信号的监视,实现对功率模块的保护功能。当发生故障时,能够及时的完成旁路、切除故障功能,并通过光纤发送给上位控制器。

## 5 实验结果

为了验证所设计系统实际性能,在完成所有功率单元的独立调试后,即可进行系统的整体调试。

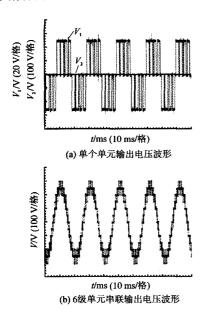

## 5.1 功率单元输出波形

不同数目功率单元串联时的输出电压波形如图 10 所示,其中输出电压的基本频率为 50 Hz,变频器空载运行。随着串联功率单元数目的增加,输出电压的等级数目也逐渐增多,输出电压波形也越来越好。当 6 级功率单元全部投入运行时,相电压波形非常接近正弦波,可以看出级联式多电平变频器的输出电压波形要明显好于传统的两电平变频器。

图 10 功率单元输出相电压 50 Hz 波形 Fig. 10 The output waveform of the power unit with 50 Hz

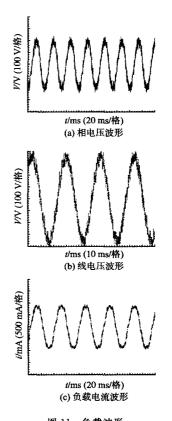

#### 5.2 负载波形

当该高压变频器以异步电动机作为负载时, 其输出的电压和电流波形如图 11 所示。其中图 11a 为电动机输入端的相电压波形,图 11b 为电 动机的线电压波形,图 11c 为变频器的输出电流 波形。由于电动机为阻感负载,其自身的滤波作 用消除了输出电压中的高次谐波,使得电流的波 形较好,谐波含量较低,接近于正弦波。

图 11 负载波形 Fig. 11 The load waveform

## 6 结论

本文设计了级联式多电平变频器控制系统,包括基于 TMS320F2812 和 FPGA 的主控制系统、基于 2SD315A 和 89C52 的功率模块的驱动与保护电路以及软件控制系统。给出了基于该设计的变频调速系统的实验结果,并进行了分析,实验波形说明所设计的级联式多电平变频器的综合性能优良。

#### 参考文献

- [1] Meynard T A, Foch H. Multi-level Conversion: High Voltage Choppers and Voltage-source Inverter [J]. in Proc. IEEE Power Electron. Spec. Conf., 1992,1,397-403.

- [2] 薄保中,刘卫国,罗兵,等. 多电平变频器 PWM 控制方法的 研究[J]. 电气传动,2005,35(2):41-45.

- [3] 葛照强,黄守道.基于载波移相控制的单元串联多电平变频器的分析研究[J].电气传动,2006,36(10):22-25.

- [4] 苏奎峰, 吕强, 耿庆峰, 等. TMS320F2812 原理与开发 [M]. 北京:电子工业出版社, 2005.

收稿日期:2008-08-06 修改稿日期:2009-04-07