## 一种吊放声纳大容量数据存储系统设计方法

陶林伟, 王英民, 王 成, 牛奕龙, 苟艳妮

(西北工业大学航海学院 西安 710072)

摘要:为了获得海洋声数据及水下目标回波数据,从而更好的研究及改进吊放声纳系统。利用高速信号处理芯片 TMS320VC5509A 的特性加上大容量 NAND FLASH 存储芯片,针对吊放声纳系统的特点,设计了一套实用的高集成度吊放声纳数据记录系统。以提高系统集成度、稳定性作为关键点,从系统结构、硬件设计、存储结构、软件设计等几个方面阐述了设计思路及实现方法。经实际使用证明,整个系统结构简洁,设计合理可靠,使用方便,具有很好的扩展性。

关键词: 吊放声纳;TMS320VC5509A;FLASH存储芯片

中图法分类号: TP391

文献标识码:A

文章编号: 1000-3630(2008)-03-0450-05

# An approach to designing mass data storage system of dipping sonar

TAO Lin-wei, WANG Ying-min, WANG Cheng, NIU Yi-long, GOU Yan-ni (College of Marine Engineering, Northwestern Polytechnical University, Xi'an 710072, China)

**Abstract:** In order to obtain ocean acoustic data and underwater target echo data to better study and improve dipping sonar system, a practical and high integrated data record system using high speed digital signal processing chip TMS320VC5509A and mass capacity flash memory chip is developed. Aimed at enhancing system integration and increasing system stability, the design and implement method is illustrated in system structure, hardware design, memory structure, software design etc. The practical applications have verified that the system is concise in structure, rational in design, convenient to use, and has good expansibility.

Key words: dipping sonar; TMS320VC5509A; FLASH

## 1 引 言

反潜直升机尤其是舰载反潜直升机的主要反潜探测设备是吊放声纳<sup>[1]</sup>。主要用于对潜艇的搜索、跟踪、测向、测距、测速及目标识别。利用直升机机动灵活,能较快飞至潜艇出现海域的特点,可在短时间内搜索大面积海域,探潜攻潜。随着近几年潜艇性能的不断提高,特别是出于探测在浅水区活动的安静潜艇的需要,各国海军十分重视吊放声纳的发展。

吊放声纳按工作环境可以简单的分为水上、水

收稿日期:2007-05-20:修回日期:2007-09-20

作者简介: 陶林伟(1978-), 男, 陕西西安人, 博士研究生, 研究方向为 武器系统与运用工程。

通讯作者:陶林伟, E-mail:tlwlyn@163.com

下两个部分。水下部分工作时吊放在海平面以下固定深度,在主动工作方式,发射声脉冲,然后接收目标回波信号;在被动工作方式,仅接收环境及目标噪声。然后将接收的声音信号进行数字化,通过电缆将数据传输给水上部分,进行下一步处理。

伴随吊放声纳研究,人们对目标回波及水下环境噪声很感兴趣。从这些数据可以分析特定海域的海洋声特性、噪声特性及目标特性等等很多有用信息,还可以针对信号特点研究更有效的处理方法等等。这就需要一套能够将大量声数据长时间存储的设备。

本文针对吊放声纳的特点,以记录水下部分传输的数字原始声信号为目的,利用高速信号处理芯片和 大容量存储器设计了一套完整的数据存储系统。

#### 2 系统结构设计

针对目前的吊放声纳技术,对水下声信号采样并存储时,基本要求是:在约 10kHz 采样率,即100μs 的采样周期内完成对  $n(n=16~32~ \pi)$  路声信号的采集和存储。

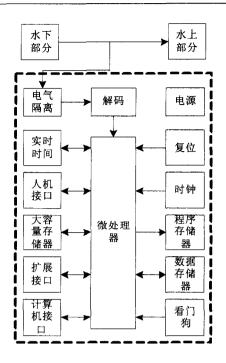

根据吊放声纳的特点,结合当今电路设计的趋势,系统采用微处理器加外围电路的总体框架,即由微处理器统一管理、控制所有外设来协调工作,完成设计功能。

作为采集系统,对原系统做到最小干扰是很重 要的。系统设计了光电隔离,在电气上和原系统隔 离。由于实际中不同吊放声纳使用不同的水下水上 数据传输协议, 所以需要专门的协议解码电路,并 且解码电路可以根据不同的情况加以修改。系统与 计算机的通讯是必要的,只有将数据从存储系统正 确的传输到计算机内部、这个系统才有实用价值。 对存储系统来说,记录实时时间是十分必要并且有 很大的实用价值。它为对存储数据的后期处理,综 合其它非声信息进行全面处理提供统一的时间刻 度。大容量存储器最需要关注的指标是存储器的存 取速度,它直接决定了系统是否可以实时的完成任 务。人机接口同样必不可少,它提供给操作员操作 接口,并反映系统的工作状态,给系统的调试及使 用带来极大的方便。保留接口为系统的升级或增加 功能做好硬件准备, 使系统成为一个开放的系统, 具有更大的灵活性,更多的应用价值。

一个完整微处理器系统还应包括:程序存储器;数据存储器;看门狗;复位;时钟信号;电源等。 根据分析,系统结构设计如图 1。

## 3 硬件设计实现

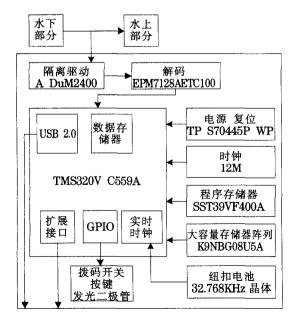

系统微处理器的芯片选择是最为关键的。要从速度、接口、存储器、开发环境、指令等等很多方面考虑。在充分查阅各类处理器资料后,本系统采用TI公司的16位定点处理器TMS320VC5509A<sup>[2]</sup>。它的时钟最高速度可达200M,指令周期5ns,在采样周期内可执行20000条指令。除了高速度外,选择此芯片最主要原因是它的内部外设特别适合此系统。它具有128k内部RAM;看门狗;8个通用IO;USB2.0接口;实时时间。可以看出,此芯片将系统一大部分功能都集成到内部,大大提高了系统的集成

图 1 系统结构 Fig.1 System structure

度。同时此芯片还提供其它外设,包括:异步静态 RAM、异步 EPROM、同步 DRAM 接口;主机接口;3 个多通道缓冲串口;2 个 MMC 接口;I2C 接口;4 通 道 10 位精度的模数转换器。

光电隔离电路采用 ADI 公司的数字隔离芯片 ADuM2400,每片 4 通道隔离,3~5V 工作电压,最高数 据率 90Mbps,隔离电压 25kV。选择隔离芯片关键指标是数据率,必须能够不失真对信号进行隔离传输。

解码模块使用一块复杂可编成逻辑电路(CPLD)。 针对不同吊放声纳不同的数据传输协议,在片内设计相应的解码逻辑,最后将数据统一转换为并行 16位数据,并产生对微处理器的中断信号。这样设计的好处是微处理器操作与具体信号协议无关。CPLD芯片选用 ALTERA 公司的 EPM7128AETC100。

实时时间直接使用微处理器的内部实时时间模块。由于实时时间需要不间断工作,所以使用纽扣电池给其专门供电。同时,外部连接一个32.768kHz晶体作为时钟的振荡源。实时时间还可以选择MAXIM公司的实时时间芯片,如DS1557。它的特点是将时间管理、电池和晶体完全集成在一起,同时还集成其它一些功能,如RAM、复位、看门狗,使用十分方便。本系统选择使用微处理器的实时时间,是追求更高的集成、系统简单、稳定性等。

人机接口使用微处理器的八个通用 IO 完成。 人机接口设计为两个拨码开关,三个按键,三个指示 灯。两个拨码开关用来选择自动存储(系统自动采集 存储)、手工存储(由按键控制采集存储)、转存数据(将数据传输到计算机)等三种模式。三个键设计为启动、停止、擦除。当选择为手工存储或转存数据时,启动键使操作进行,停止键则停止操作,擦除键直接控制微处理擦除大容量存储器。三个指示灯分别为采集存储灯、转存灯、擦除灯,用来指示系统的工作状态。

与计算机通讯接口使用微处理器上的 USB2.0 接口。USB 技术现在已经十分成熟,它使用方便、传输速度快,是最佳的传输方案。

大容量存储器的选择是最为关键的。采用 SAMSUNG 公司的 K9NBG08U5A<sup>[3]</sup>芯片,容量 4G× 8 位,3.3V 工作电压,8 位并行接口,100k 次擦写次数,10 年的数据存储期。选用此芯片主要依据是此芯片的容量和快速的存取速度。根据此芯片的容量,系统需要六片组成一个存储阵列以满足系统记录时间长度。这六片存储器均连接在微处理器的总线上,分配不同的地址。芯片最坏情况下的写入单个字节时间最长 480ns。

扩展接口使用微处理的串行接口及其它接口。数据存储器和看门狗也使用微处理器内部的相应外设。电源使用 TI 公司针对此芯片推出的 TPS70445-PWP,同时具有复位功能。程序存储器选用 FLASH存储器。微处理器的时钟使用有源晶振,选择 12M晶振,经过微处理器内部的 PLL 锁相环倍频,内部时钟可以非常高。

经过硬件选型,系统硬件结构如图 2。可见,系统 集成度十分高,相应的提高了系统稳定性,降低功耗。

图 2 硬件结构图 Fig.2 Hardware structure

硬件设计好以后,分析系统是否可以实时完成功能。对整个采集记录过程来说,最费时的是对大容量存储器的写人。根据资料,对任意地址的单字节写人操作最长需要 480ns。在采样周期内,写入声数据需要约 16μs。远远小于采样周期 100μs。

#### 4 存储方式设计

在选定了大容量存储芯片后,面临如何规划及 使用存储空间,怎样组织数据及存储数据最合理,哪 种存储方式最方便还原数据,如何处理意外断电数 据存储正确性等等问题。

这些问题可以归结为针对大容量存储芯片的存储特点设计一个最佳的数据结构。

K9NBG08U5A 是 NAND FLASH 芯片,它具有FLASH 芯片的共同特点。即芯片每一地址空间只能写人一次,掉电后数据不消失。若要修改数据,则必须对某一块存储空间进行整体擦除。擦除后,这一块数据全为 0xFF。

K9NBG08U5A 芯片内部以页为最小组织单位,每2048 字节为一页,每64 个页为一个块,每8192个块为一片,1 片即为1G×8 位。K9NBG08U5A 内部共有4 片。芯片对于读、写、擦除每次涉及的最小单位是不一样的。对于读写,每次可以为一个字节,但如果以页来进行读写操作,是最高效率的。对擦除是每次最少擦除一个块。据此,系统设计存储数据结构如下:

定义声数据结构如下[4](c语言描述): typedef struct tag\_SOUND

short int soundData[16];// 声数据}SOUND;

可知,每个声数据结构有32个字节。 定义时间结构如下:

typedef struct tag\_TIME

byte year; // 年

byte month; // 月

byte day; // 日

byte hours; // 小时

byte minutes; // 分钟

byte second; // 秒

}TIME;

时间结构长度6个字节。

#### 设计存储数据结构如下:

### $typedef\ struct\ tag\_FRAMEDATA$

int size; // 结构长度

byte ver; // 结构版本

byte erased; // 是否空

byte finish; // 是否存储完毕

TIME time; // 实时时间

SOUND sound[4095]; // 声数据

byte reserved[19]; // 保留

#### FRAMEDATA:

此结构设计长度与块的长度相同。共记录声数据 4095 次,记录实时时间一次。若采样率为 10k,则一个结构数据记录 409.5ms 时间数据。

size 表示此结构的长度,此信息在计算机恢复数据时有很重要的作用。ver 指明此结构的版本号,若结构发生变化,版本号随之增加,这是计算机读取不同版本数据的关键技术。erased 表明此块空间是否空。若值为 0xFF,则表明为空。微处理器在向一个新块写人数据时,先检查此字节,若为 0xFF,则先改写此值,表明此块已经被占用,然后再写人数据。finish 是用来标志此块数据是否完全正确写人。正常情况下,微处理器对此块写人完成后,修改finish 为非 0xFF。若微处理器在写入数据时,突然断电或其它情况导致写入操作非法中断,那么finish 将保持 0xFF。计算机在处理的时候,就可以根据 finish 判断数据的正确性。sound 是声数据数组。time 记录这一块数据的起始时刻。reserved 是保留空间。

根据数据结构的设计,可以计算系统的最大存储时间。每个数据结构记录 409.5ms 数据,从芯片内部容量可知,单芯片记录时间长度可达 3.7 小时。整个存储器阵列记录长度可达 22.36 小时,已经可以满足实际使用的需求。

## 5 软件设计

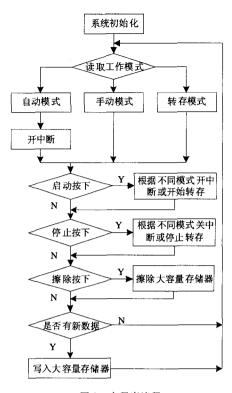

软件设计分为两大部分,主程序和中断程序。基本的设计思路是在微处理器内部 RAM 中创建一个FIFO 结构。中断程序将接收到的声数据放到 FIFO 人口即返回。由主程序查询 FIFO 的输出口,若有数据,则根据当前存储的状态,写人大容量存储器。

主程序先调用初始化程序对系统进行初始化, 然后反复查询人机接口和 FIFO 输出口的状态。流

图 3 主程序流程 Fig.3 Main program flow chart

程简单描述如图 3。

在写人大容量存储器一步中,还有很多复杂的判断操作,比如若是存储数据结构的开头,还要读取时间,填写 size、ver、erased、time 等等参数;在对一个数据结构完全写人后,还要修改 finish 参数等等大量的细节操作。在实际开发时,需要针对不同情况,进行仔细的分析,尽量考虑所有的可能性。同时,写人数据到大容量存储器时,尽量每次写入一批数据,这样将大大提高写入效率。

## 6 结 论

本文从吊放声纳的特点入手,设计了一套实用的吊放声纳数据采集存储系统。并从系统结构、硬件结构、存储数据结构、软件结构等几个方面入手,阐述了设计思路和实现方法。系统采用了高速 DSP 加外围器件,并充分利用 DSP 的内部资源,极大地提高了系统集成度,从而使系统的稳定性、可靠性大大提高。用户可以根据不同的需求,在本系统基础上设计新的系统。可以采用更多现代技术,如使用IDE 接口,存储海量数据,如 SONY 公司的 SIR-3000 系列数据采集记录系统使用 IDE 接口,可以存储 200G 的海量数据<sup>[5]</sup>;使用远程总线技术,实现远程采集,如赵宇等提出的基于 ADS1210 的分布式高

精度数据采集系统<sup>[6]</sup>;对于高速采集系统,可以使用 SDRAM,将数据存储到高速 SDRAM,然后批量的 转存到 IDE 或 FLASH,如贾雅琼设计的汽车运行 状况图像监测系统设计<sup>[7]</sup>;在多路高速系统中,可以 使用 FPGA 完成大量的逻辑功能,从而减轻微处理器的压力,完成采集任务,如杨林楠等设计的基于 FPGA高速多路数据采集系统<sup>[8]</sup>。

#### 参考文献

- [1] 蓉竹. 机载声纳浮标和吊放声纳[J]. 现代军事. 2006. 63. RONG Zhu. Airplane carry sonobouy and dipping sonar [J]. Modern Military. 2006. 63

- [2] Texas Instruments. TMS320VC5509A fixed-point digital signal processor data manual[DB/OL]. 2006. www.ti.com.

- [3] Samsung Electronics. K9XXG08UXA[DB/OL]. 2006. www. samsung.com.cn

- [4] 朱站立, 刘天时. 数据结构[M]. 西安交通大学出版社. 2006.

西安.

- ZHU Zhanli, LIU Tianshi. Data structure[M]. XI'AN Jiao-Tong University Publisher. 2006. XI'AN.

- [5] SONY Manufacturing systems corporation. High speed data recorder general catalog SIR-3000 series [DB/OL]. May, 2007. HTTP://www.sonysms.co.jp

- [6] 赵宇,金玉涛,张玉英. 基于 ADS1210 的分布式高精度数据采集系统[J]. 微计算机信息,2007,23(3-2):298-299. ZHAO Yu, JIN Yutao, ZHANG Yuying. The design of high precision data acquisition system distributed based on ADS1210[J]. Control & Automation, 2007,23(3-2):298-299.

- [7] 贾雅琼. 汽车运行状况图像监测系统的设计[J]. 今日电子, 2007, **167**: 93-94.

- JIA Yaqiong. The automobile run condition image monitor system design[J]. Electronic Products, 2007, 167: 93-94.

- [8] 杨林楠,李红刚,张丽莲. 基于 FPGA 的高速多路数据采集系统的设计[J]. 计算机工程,2007,(4):246-248. YANG Linnan, LI Honggang, ZHANG Lilian. Design of high speed multichannel data gathering system based on FPGA [J]. Computer Engineering, 2007, (4):246-248.