文章编号:1002-8684(2006)11-0029-04

# 基于 THS1206 的 水下多路数据采集系统设计与实现

·系统设计·

赵延安, 张效民

(西北工业大学 航海学院, 陕西 西安 710072)

【摘 要】水下声信号是水下探测系统实现对水中目标远程探测识别的主要信息之一,有效获取水下声信号是一个十分重要的问题。探测系统数据采集部分的速度、精度及功耗直接影响整个系统的性能。针对水下探测系统对数据采集部分的要求,利用微功耗器件 THS1206 与 TMS320VC5509A 设计的水下数据采集系统速度快、功耗低、精度高,可同时采集多路水下信号,满足探测识别系统对于数据采集部分的要求。对整个数据采集系统,给出了系统软硬件设计的关键接口原理框图和流程图。整个采集系统经过实际测试,达到了设计要求。

【关键词】THS1206;数据采集;TMS320VC5509A

【中图分类号】TB56

【文献标识码】B

Design and Realization of Underwater Multi-channel Data Acquisition Based on THS1206 A/D Converter ZHAO Yan-an, ZHANG Xiao-min

(College of Marine, Northwest Polytechnical University, Xi'an 710072, China)

[Abstracts] The underwater acoustic signal is the main information for the underwater detection and identification system, so it is very important to get the acoustic signal efficiently. However, the data acquisition system must match many factors such as acquisition speed, accuracy, power. To satisfy these requirements, ultra-power devices THS1206 and TMS320VC5509A are used to design the underwater acoustic data acquisition system. The key points of the whole system are described. It is demonstrated that the whole system matches the factors which the data acquisition system expects.

[Key words] THS1206; data acquisition; TMS320VC5509A

## 1 引言

对于水下定位系统,系统的实时性是一项重要指标。而影响系统实时性的一个重要因素就是构建高速率的数据采集系统。笔者将利用 12位的 A/D THS-1206 构建一个多路高速率的采样系统。该系统利用 TMS320VC5509A 作为系统的控制和处理单元。

## 2 THS1206 简介

#### 2.1 主要特点

THS1206 是针对雷达、图像处理、通信等领域而推出的一款采用多级流水线结构的 12 位高速 A/D 转换器。其主要特点如下:

(1)可 4 路单端同时输入,或者 2 路差分输入,或两种形式共同存在;(2) 内部集成了 16 字的 FIFO;(3)高转换速率,最高转换速率可达 6 MS/s;(4)低功耗,在5 V 供电时为 216 mW,有待机模式可供选择;(5)精度

高,差分非线性误差为±1 LSB,积分非线性误差为±1.5 LSB;(6)自动扫描 2,3,4 路输入,多路同时采样和保持等;(7)高信号与噪声加失真之和比(SINAD):当 f=2 MHz 时为 68 dB;(8)采用单 5 V 供电,可选取内部基准电压(1.5 V 和 3.5 V)或外部基准电压。

### 2.2 内部结构及引脚功能

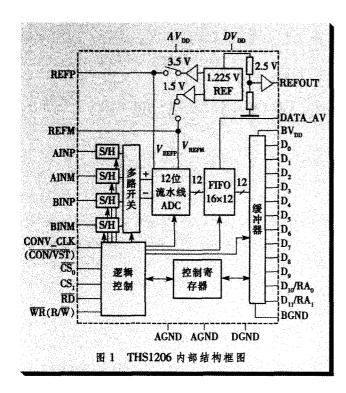

THS1206的内部结构框图如图 1 所示,它由采样保持器、逻辑控制单元、控制寄存器、12 位流水线 ADC和 FIFO、缓冲器等组成。

THS1206 有 4 路采样保持器,可同时对 4 路信号进行采样保持,并按顺序依次对各通道的采样保持值进行转换。THS1206 单个通道的最高采样频率可达6 MS/s。同时采样多个通道的模拟信号时,每个通道的采样频率 f 为

## BH5 BB arks and Circuit

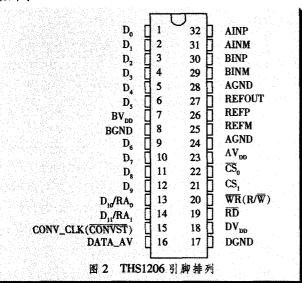

THS1206 的引脚图如图 2 所示, 其各引脚的定义如下:

AINP,AINM,BINP,BINM:模拟输入通道,这 4 个 引脚既可用作 4 个单独的非极性模拟输入信号,也可作为差分输入通道 A 和 B 的正负模拟信号输入端;  $AV_{DD}$ ,AGND:ADC 模拟电压和模拟地; $BV_{DD}$ ,BGND: FIFO 的数字电压和数字地; $DV_{DD}$ ,DGND:ADC 数字电压和数字地; $CONV\_CLK(\overline{CONVST})$ :启动转换信号输入端; $\overline{CSO}$ ,CS<sub>1</sub>:片选信号,低电平有效;DATA\_AV:AD转换结束信号,数据输出有效; $D_{DO}$ - $D_{DO}$ : 十位双向数据线; $D_{DO}$ / $R_{AO}$ :既可作为数据线  $D_{DO}$ ,也可作为内部控制寄

存器的地址线  $RA_0$ ;  $D_1/RA_1$ :既可作为数据线  $D_1$ 1,也可作为内部控制寄存器的地址线  $RA_1$ ; REFOUT: 2.5 V 参考电压输出; REFIN: 共模输入参考电压,作为 AD 转换的标准参考电压,可直接将此引脚接至 REFOUT 引脚以输入 2.5 V 标准电压; REFP, REFM: 外部输入参考电压的正负极接入; RD, RW(R/W): 读写控制信号。

#### 2.3 控制寄存器

THS1206 通过内部两个 10 位控制寄存器( $CR_0$ ,  $CR_1$ )来控制 ADC 的具体运行状态。控制寄存器的定义 如表 1 所示。

表 1 控制寄存器定义

| BIT                | BIT,              | BIT.              | BIT,            | BIT <sub>6</sub>  | BIT,              |

|--------------------|-------------------|-------------------|-----------------|-------------------|-------------------|

| CR <sub>0</sub>    | TEST <sub>1</sub> | TEST <sub>0</sub> | SCAN            | DIFF <sub>1</sub> | DIFF <sub>0</sub> |

| CR <sub>1</sub>    | RBACK             | OFFSET            | BIN/2S          | R/₩               | DATA_P            |

| BIT.               | BIT,              | BI                | T <sub>2</sub>  | BIT,              | BIT <sub>0</sub>  |

| SHSEL <sub>1</sub> | CHSEL             | , PD              |                 | MODE              | VREF              |

| DATA_T             | TRIG              | TR                | IG <sub>o</sub> | OVFL/F            | RESET             |

#### 其主要参数说明如下:

(1)基准电压选择: 当 VREF=1 时, 采用外部基准, 否则,选择内部基准;(2)转换模式选择: 当MODE=1 时,ADC 为单次转换模式,否则为连续模式;(3)通道 选择:结合 CR<sub>0</sub>的第 5,6,7 位,CHSEL<sub>1</sub>,CHSEL<sub>0</sub>按照二 进制编码选择输入的通道号;(4)自动扫描选择:当有 多路输入时,ADC 一般都选择扫描方式。当 SCAN=0 时,ADC 启动自动扫描方式,否则,禁止自动扫描方 式;(5)复位控制:置 RESET=1,THS1206 复位;(6)触 发级别设置:TRIG1,TRIG0选择每次的触发级别,即 每次读取的数据量;(7)DATA\_AV 输出方式控制: 当DATA\_T=1时,DATA\_AV为边沿触发,否则为电平 触发;(8)DATA\_AV 极性控制: 当 DATA\_P=1 时, DATA\_AV 高电平有效,否则低电平有效;(9)读写控 制: 当 R/W=1 时, WR 为读写信号, RD 禁止输入,当 R/W=0 时, WR 为读信号, RD 为写信号; (10) 输出数据 格式控制: 当 BIN/2S=1 时,数据以补码形式输出,否则 以二进制格式输出。

# 3 数据采集系统实现

#### 3.1 系统硬件原理图

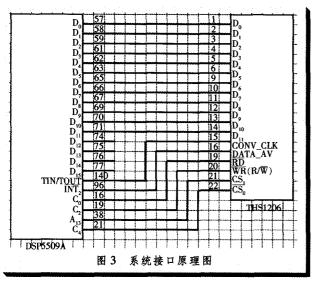

THS1206 可以很方便地与多种控制器或者 DSP 实现无缝连接。图 3 为 THS1206 与 TMS320VC5509A

的接口原理图。THS1206 通过 DSP 的 EMIF(外部存储器接口)模块,作为外部存储器连接至 DSP。用 DSP 的外部空间 0 的选通信号  $CE_0$  (即图 3 中  $C_4$ 信号)作为THS1206 的片选信号<sup>[1]</sup>,并且给 THS1206 分配地址 0x29000。THS1206 的 DATA\_AV 连接到 DSP 的外部中断 2 引脚,让 DSP 发生中断读取转换的数据。THS1206 的转换时钟由 DSP 提供。通过配置 DSP 的定时器控制寄存器可产生所需要的时钟频率。

#### 3.2 电平变换

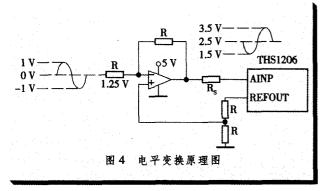

由于 THS1206 采用了 1.5 V 和 3.5 V 双基准电源,所以输入端信号的幅值必须要在 1.5~3.5 V 之间。若不满足,必须进行输入信号电平变换。笔者采用了文献[2]中所给出的一种电平变换形式。如图 4 所示,放大器的放大倍数为-1,通过对 THS1206 的 2.5 V 参考电压进行电阻分压得到同相端 1.25 V 电压。这样放大器输出的中心电平为2.5 V。若输入幅度为-1~1 V,则放大器输出为 1.5~3.5 V,满足 THS1206 输入信号幅度要求。

#### 3.3 软件设计

系统的软件设计主要需要考虑 THS1206 的配置及 DSP 如何有效读取所转换的数据。如上文所述,整

个系统采取中断的方式读取 ADC 的转换结果。但是在一些实时性要求较高的场合,每次转换结果通过中断方式读取时间开销是巨大的,同时也有可能会因为中断服务程序的执行而造成数据的丢失。为提高 A/D 数据输出能力,减小处理器的负担,THS1206 内部集成了一个 16 字的环形缓冲寄存器,可根据需要设置每次所读取的数据量。在软件设计时,要充分利用这一优点,最大限度提高数据的传输效率和减小处理器处理中断的负担。

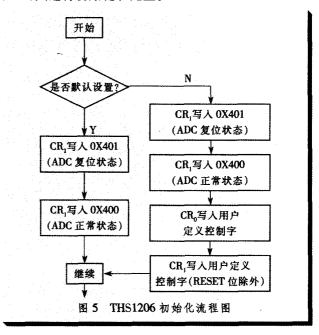

此外,THS1206 正确的初始化和配置是整个系统有效工作的前提条件。在程序设计时,可按图 5 的流程图<sup>[3]</sup>对其进行初始化和配置。

在设计的系统中,需要对 4 路信号采样,每路的采样速率为 25 kHz,所用 DSP 主频为 80 MHz,故设置 THS1206 工作在四通道连续扫描方式;FIFO 的触发级别为 12,即每得到 12 个采样数据,就向 DSP 发送一次中断请求信号。

对 THS1206 操作的部分程序如下:

初始化 THS1206 程序:

- \* (volatile int\*)AD\_ADDR=0x401; % AD\_ADDR 为THS1206 地址值

- \*(volatile int\*)AD\_ADDR=0x400;

- \*(volatile int\*)AD\_ADDR=0x098;

- \*(volatile int\*)AD\_ADDR=0x496;

产生 THS1206 转换时钟程序,设置 DSP 的定时器以产生期望时钟频率:

TIMER\_Config timerCfg0 = {

#### **器件与电路** Parks and Circuit

0x0c28, /\* Timer Control Register (TCR) \*/

0x04F, /\* Timer Period Register (PRD) \*/

0x0009\}; /\* Timer Prescalar Register(PRSC) \*/

hTimer0 = TIMER\_open (TIMER\_DEV0, TIMER\_

TABLE OF TIMER\_OPERIOR (TIMER\_DEV0)

OPEN\_RESET);

TIMER\_config(hTimer0, &timerCfg0);

interrupt void ADChange(void)

中断处理程序:

{ for (Ad\_Pointer=0; Ad\_Pointer<11; Ad\_Pointer++)

Ad\_Convert[Ad\_Pointer]=\*(volatile int\*)AD\_ADDR;

}%读取所转换的12个数据并存储。

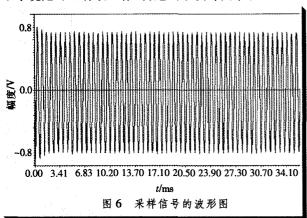

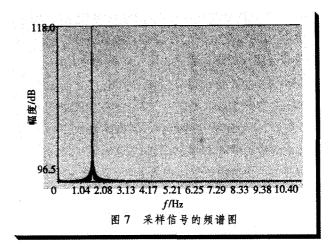

为了验证整个采集系统的性能,在实验室进行系统性能测试实验。实验用信号为一个频率为 1.5 kHz、中心电平为 2.5 V、峰-峰值为 1.6 V 的正弦信号,其采样信号的波形和谱图如图 6、图 7 所示。可以看出,整个系统是可以有效工作的,达到了设计要求。

# 4 结束语

笔者所设计的水下数据采集系统成功地应用在某水下探测识别系统中,其功耗、速度、精度都达到了整个系统的设计指标。该设计方法是可靠和有效的。

#### 参考文献

- [1] 汪春梅,孙洪波,任志刚. TM3205000 系列 DSP 系统设计与开发实例[M]. 北京:电子工业出版社,2004.

- [2] 党宏社,韩崇昭,王西圣. 基于 THS1206 的多路高速数据 采集的实现[J]. 仪表技术,2002(4):22-25.

- [3] 孙洪明,王朋海,黄万伟. 可编程多路 A/D 转换芯片THS1206 的原理及应用[J]. 国外电子元器件,2005(4):41-42.

#### 作者简介

赵延安,研究生,主要从事水下信号检测与处理等方面研究。 [责任编辑] 史丽丽 [收稿日期] 2006-09-01

(上接第28页)

# 4 软件设计

该系统软件设计是一关键,它用来解决波形参数设置,以及波形选择等问题。信号源有3种工作方式,单频连续波、单频脉冲信号和噪声信号,单频脉冲信号的低延时是由 $P_{1.4}$ 和 $P_{1.5}$ 两个端口控制,因而当把这两个端口置1,同时关掉定时器0,可产生单频连续波。当输出噪声时, $P_{1.4}$ 口置0, $P_{1.5}$ 口置1,保持滤波器正常工作。输出的每种波形都有4个参数可调,脉宽、周期、频率、幅值,根据输入键值可以设定相应的参数。脉宽调节由定时器0内部程序控制。

# 5 总结

该系统利用单片机强大灵活的逻辑控制功能、 CPLD 简化外围电路、精确分频和数字滤波设计方法 实现了水下低频信号源,根据试验要求,可产生单频连续信号、单频脉冲信号、噪声信号,并且每种波形具有4种参数可调,包括周期、脉宽、幅值、频率。该设计方法性能稳定可靠、功能扩展灵活、电路简单,已在试验中获得工程应用。

#### 参考文献

- [1] 孙涵芳,徐爱卿. MCS-51 系列单片机应用系统设计[M]. 北京:北京航空航天大学出版社,2002.

- [2] 黄正瑾,徐坚,章小丽. CPLD 系统设计技术入门与应用[M]. 北京:电子工业出版社,2003.

- [3] 楼顺天,李博菡. 基于 MATLAB 的系统分析与设计[M]. 西安:西安电子科技大学出版社,1998.

- [4] 熊俊俏,卢容德. 一种多功能数字合成信号源的软硬件设计[J]. 工业仪表与自动化装置,2002(2):26-28.

[责任编辑] 史丽丽

[收稿日期] 2006-07-19