Instrument Technique and Sensor

2008 No. 8

## 基于 TMS320DM6446 的多媒体视讯终端

白艳茹<sup>1,2</sup>,刘贺平<sup>2</sup>,朱珍民<sup>1</sup>,罗海勇<sup>1</sup>,先明春<sup>2</sup>,高玉之<sup>1</sup>

(1. 中国科学院计算技术研究所,北京 100080; 2. 北京科技大学信息工程学院,北京 100083)

摘要:系统选用基于达芬奇技术的多媒体数字芯片 TMS320DM6446 作为系统 CPU,并采用最新视频编码标准H. 264 压缩算法,实现基于 IP 网络的视讯终端系统。文中详细介绍了 TMS320DM6446 的硬件架构、系统的硬件构成和核心模块的实现,分析系统设计中的难点及关键技术。实验结果表明,该系统在不降低视频质量的前提下能够满足对 D1 分辨率的视频图像进行采集、实时编码和传输的要求,系统处理性能高,集成度强,交互性好,充分体现了高性能计算技术的特性。 关键词:TMS320DM6446;视频通讯;多媒体技术

中图分类号:TP277

文献标识码:A

文章编号:1002-1841(2008)08-0068-04

# Design of Multimedia Video Communication Terminal Based on TMS320DM6446

BAI Yan-ru<sup>1, 2</sup>, LIU He-ping<sup>2</sup>, ZHU Zhen-min<sup>1</sup>, LUO Hai-yong<sup>1</sup>, XIAN Ming-chun<sup>2</sup>, GAO Yu-zhi<sup>1</sup>

(1. Institute of Computing Technology Chinese Academy of Science, Beijing 100080, China;

2. School of Information Engineering, Beijing University of Science and Technology, Beijing 100083, China)

Abstract: This system realized the IP-based video network terminal system by choosing multimedia digital chip TMS320DM6446 as the CPU, and using the latest video coding standard H. 264 compression algorithm. The paper described in detail the hardware architecture of the TMS320DM6446, design of system hardware and core modules, analysis of system design and key technical difficulties. Experimental results showed that the system can meet the requirements that under D1 resolution video image capture, real-time encoding and transmission without lowering the quality of the video. The system has high performance, strong integration, nicer interactive, and fully reflect the high-performance technical features of multimedia technology.

Key words: TMS320DM6446; video communications; multimedia technology

#### 0 引言

视频会议系统成为多媒体技术应用的新热点。作为视频会议系统必不可少的终端部分,视讯终端也成为了一种重要的多媒体通信工具<sup>[1]</sup>。文中设计的视讯终端采用 TI 新一代多媒体数字处理芯片 TMS320DM6446 作为处理器,并给出具体的解决方案。

TMS320DM6446 为 32 位处理器,内部集成 TMS320C64x + DSP 和 ARM926EJ-S MPU 双核结构,综合 DSP 与 RISC 工艺的优点,其丰富的用户接口,高速处理性能,强大的操作系统支持以及低功耗等特点,将广泛适用于多媒体网络视频通讯系统。

#### 1 系统概述

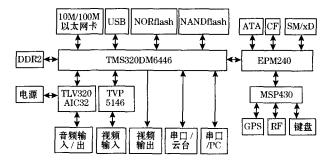

系统的工作过程如下:系统上电或复位后,从 Flash 加载程序,完成对芯片的初始化和外围硬件的配置等工作,之后便开始进行图像采集。DM6446 通过 I2C 接口对系统中的其他芯片进行控制,从摄像头采集到的模拟视频信号经过视频解码器转换为数字视频信号,送入 DM6446 的视频通道;同步采集到的模拟音频信号经过音频编解码器模/数转换后,送入 DM6446 的音频通道。DM6446 将接收到的数字视频信号和数字音频信号用H. 264 标准编码压缩,再通过网络将数据传输给 MCU 或其他

终端。系统主要由以下几个模块组成:核心处理器模块、视频输入解码模块、音频输入/输出模块、外部存储模块、网络发送控制模块及电源管理模块等。系统整体结构如图1所示。

图1 系统结构图

TMS320DM6446 除集成 ARM 和 DSP 内核外,还集成了视频处理子系统(VPS)以及丰富的外围接口。视频处理子系统包含了前端处理部分,并增加了视频影像协处理器(VICP)。在视频解码应用中,可用到 VPS 后端所集成的 OSD、4 个视频DAC、24 位数字 RGB 输出单元,而在视频解码中应用,可用到VPS 前端所集成的图像缩放工具、影像处理引擎、16 位数字输入单元。视讯终端采用此芯片进行视频处理可以达到 D1 高清晰图像分辨率,为用户提供 DVD 画质的实时双向通信,利用更简单的外围设计达到了更高的多媒体通信性能。

#### 2 系统子模块设计

#### 2.1 核心处理器模块及其地址分配

TMS320DM6446 内 DSP 核频率高达 600 Hz, ARM 核频率 高达 300 Hz, 每周期执行 8 条 32 位指令, 在软件上 DSP 和 ARM 是完全兼容的。

C64x + DSP 内核是 C6000 系列 DSP 中最高性能的定点 DSP,采用超长指令字 VLIW,8 个独立功能单元,其中 6 个算术 运算单元每周期支持 32 位、双 16 位、4 组 8 位算术运算,2 个乘 法器每周期支持 4 个 16 × 16 或 8 个 8 × 8 乘 法运算。 4752MIPS,内部具有 64 个 32 位的寄存器,取数/存数的数据通为 64 bit. C64x + 通过把 DSP 运算压缩在较少的周期里,加速通信和图像应用。在增强并行性的扩展中,四组 8 位两组 16 位指令允许每 s 进行约 90 亿次 8 位乘法累加周期 (MAC) 运算  $\mathbb{Z}^{[2]}$ 。

ARM926EJ - S 是 32 位 RISC 处理器内核,支持 32/16 bit 指令和 32/16/8 bit 数据,采用流水线操作,使用 CP15 协处理器和保护模块,各自的 16K 字节指令和 8K 字节数据高速缓冲存储器。

针对 DSP 内核具有高速的数据运算能力和 ARM 内核具有丰富的人机交互接口的特点,系统设计使 C64x + DSP 内核主要负责对采集到内部输入缓存的数字音/视频数据流进行处理及压缩,ARM926EJ - S 内核主要负责对外围接口的控制。用相互中断控制 ARM 核和 DSP 核之间的通讯。系统 ARM 和 DSP 共享 DDR2 和 AEMIF,用软件控制可以实现互相访问各自的片内存储器。硬件上 ARM 控制 DSP 的电源、时钟、复位和引导。

系统采用的 DM6446 处理器的地址空间分配如图 2 所示。 DM6446 有大量字节可寻址的地址空间,程序代码和数据可被存储在统一标准的 32 位地址空间的任何位置。在默认状态下,系统软件起始位置为 0x00000000,内部的寄存器从0x00000000 地址空间开始存储。根据需要一部分存储器由软件控制重新映射为 L2 高速缓存。图中的 CS2 - CS5 为电路使能空间,是 DM6446 的 AEMIF 的 4 个独立的可设定地址的区域。目前系统使用电路使能区 CS2,并将其分配给 FLASH,通过硬件控制 DM6446 的 BTSEL1、BTSEL0 管脚分别为 0、1 设定系统为 ARM EMIFA 启动方式,配置 u-boot 从 norflash 启动。 CS3 - 5 的电路使能区暂不使用,可以作为今后的扩展。

| 地址                               | DM6446 地址空间 | 系统地址分配     |

|----------------------------------|-------------|------------|

| $0 \mathbf{x} 0 0 0 0 0 0 0 0 0$ | ARM 指令 RAM  | ARM 指令 RAM |

| $0 \mathbf{x} 00040000$          | ARM 数据 RAM  | ARM 指令 RAM |

| $0 \times 02000000$              | AEMIF CS2   | FLASH/NAND |

| 0x04000000                       | AEMIF CS3   | DC         |

| 0x $0$ 6 $0$ 0 $0$ 000           | AEMIF CS4   | DC         |

| 0x08000000                       | AEMIF CS5   | DC         |

| 0x80000000                       | DDR         | DDR        |

图 2 系统地址空间分配

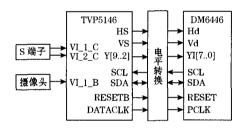

#### 2.2 视频接口设计

系统使用 TI 的视频 A/D 转换芯片 TVP5146 作为视频解码 模块的主要控制部分。TVP5146 的优点是场同步信号 VS、行同 步信号 HS、奇偶场信号 FID、时钟输出信号 DATACLK 等都由 引脚直接引出,省去了同步时钟电路的设计。如图 3 所示,摄 像头采集的视频信号在 TVP5146 内部经钳位、抗混叠滤波、 A/D转换、YUV 分离电路之后,实现模拟视频信号转换为数字 并行信号 BT. 656 码流格式,输入到压缩核心单元 DM6446 的 缓冲区。TVP5146 在本地时钟的控制下通过 EDMA 通道自动 向 DM6446 视频处理端口缓冲区单元发送数据, 当采集完一场 数据时产生 DMA 中断,并在 DMA 中断服务程序中根据实际需 要完成相应的视频处理,经过 H. 264 实时编码压缩后的视频数 据存储到外部 DDR2 中。在软件中设置参数使视频采集的数 据格式为 YUV4:2:0,分辨率为 D1 大小。由于采用 ITU - R BT. 656 码流格式,图像的水平同步、垂直同步、场同步等同步信 号已包含在 BT. 656 数字视频数据流的 EAV 和 SAV 时基信号 中,因此 TVP5146 与 DM6446 的视频接口只需视频采样时钟和 采样使能信号即可。此外,硬件电路还需要给 TVP5146 提供其 所需要的 14.318 18 MHz 时钟频率。系统通过 I<sup>2</sup>C 总线实现 DM6446 控制 TVP5146 的内部寄存器,对视频数据进行实时控 制和有效的传输[2]。

图 3 DM6446 与 TVP5146 接口原理图

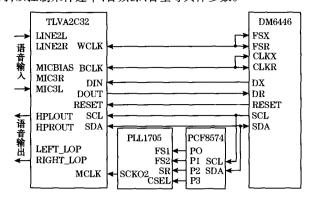

#### 2.3 音频输入/输出接口设计

系统采用立体声编解码器 TLV320AIC32 实现音频输入输 出的控制。TLV320AIC32 芯片是最新一款低功耗立体声编解 码芯片,多输入多输出,单端或差分设置可编程。在该系统中, 控制接口上用 I2C 总线连接 DM6446 与 TLV320AIC32, 音频数 据接口上 TLV320AIC32 采用 DSP 模式与 DM6446 连接,高位在 前(MSB-first),支持多种位宽,字时钟(WCLK)和位时钟 (BCLK)单独设置。语音芯片与 DM6446 之间的接口如图 4 所 示,MIC 为传声器输入,LINE(L/R)为电话线输入,DOUT和 DIN 分别接 ASP 的 DR 和 DX, 为串行数据输入和输出管脚。 BCLK 接 ASP 的 CLKX 和 CLKR, BCLK 是移位时钟, 每一个 BLCK 周期在音频总线上移进或移出一位音频数据,在 DSP 模 式下,BCLK 的下降沿开始传送数据,先发送左通道数据,接着 是右通道数据。WCLK 为字时钟,接 ASP 的 FSX 和 FSR, WCLK 代表着最大的采样频率,是一帧数据的开始,可以是脉冲信号, 也可以是方波信号,作为帧时钟信号,一帧代表一次完整的数 据通信。主时钟由系统的 I<sup>2</sup>C 总线传递参数到锁相环电路产 生,系统中音频采集电路的工作时钟为 11.289 6 MHz. 系统利 用软件控制 DM6446 通过 I2C 总线实现对音频采集电路的编 码,以控制采样速率、音频源、音量等具体参数。

图 4 DM6446 与 TLVAIC32 接口原理图

系统实现音频输入、输出控制流程如下: AIC32 的左、右 2 个 16 位音频声道从音频通道获取数字化数据,音频采集的数据格式为每路单声道,44.1 kHz 采样率,每个采样数据用 8 位量化,采集输出的数字音频数据通过 ASP 传给 DM6446 的输入缓冲区单元。当设定用于存放音频采样数据的缓存器满时产生 DMA 中断,并在 DMA 中断服务程序中根据实际设定情况处理音频数据。经过实时编码压缩后的音频数据存储到外部 DDR2 中,可以再经 ASP 返回 AIC32,经 HPL/ROUT 通过扬声器直接输出;也可通过 LOP/ROP 电话线输出。

#### 2.4 图像数据存储及传输控制模块

图像数据存储方面,系统采用 2 个 512 Mb 的 16 位 DDR2 用来存放系统运行时的代码以及临时图像数据。DDR2 通过 32 位宽数据总线与 DM6446 通讯,其定时和刷新都由 DM6446 内部的 DDR2 控制器控制。由图 2 可知 DDR2 起始地址空间为 0x80000000。FLASH 存储器具有可在系统电擦写,掉电后信息不丢失的功能,通常用来保存系统自启动代码以及系统程序代码。设计中利用 DM6446 的 NAND 接口扩展了 64 MB 的 Nand-flash,经 8 位数据总线与 DM6446 通讯,利用 DM6446 的异步 EMIF 扩展了 16 MB 的 Norflash,经 16 位数据总线与 DM6446 通讯。2 片 FLASH 都接在 AEMIF 的 CS2 空间,系统用来引导内核的 u-boot 放在 Norflash 中,起始地址空间为 0x020000000。

系统中存在大量控制信号,需要进行较多的逻辑组合和变换,为了避免分立器件带来的电路的繁琐,系统使用了1片 CPLD 完成逻辑处理和电平匹配任务,代替了额外逻辑控制电路的添加,提高了系统的稳定性。系统选用 CPLD 为 EPM240,此芯片特点为具有1.8 V 和3.3 V 两种电平端口,正好能满足系统某些信号电平转换的要求。按照系统各个功能模块划分, CPLD 实现按的功能有:

- (1)分别产生 ATA, CF, SM/xD 卡的选通信号;

- (2)将 ATA,CF,SM/xD 卡对应的读写使能、地址和复位信号由 1.8 V 转换为 3.3 V;

- (3) 实现对 ATA 和 DM6446 串口 1 的分时复用;

- (4)产生 MSP430 的中断信号;

- (5)产生 NANDFLASH 的控制信号 WAIT\_BUUSY;

- (6)产生 EMIF 缓存的控制信号 DIR 和 EN;

- (7)将系统的复位信号进行电平匹配。

实践证明,视讯终端采用 DM6446 + CPLD 的方式,减轻了 DM6446 的处理负荷,简化了系统硬件设计,降低了硬件调试难度,有效地提高了系统处理速度,且系统可扩展性和适应性也得到了加强。

#### 2.5 电源管理模块

系统采用 TPS54310PWP 开关电源芯片,输入电压为 5 V, 经 TPS54310PWP 转换出 3.3 V 和 1.8 V, 分别给 L/O 端口和 DSP 内核供电,另外再由一片 TPS54310PWP 产生 1 个 3.3 V 给视频编解码及其它芯片供电。设计时这 2 个 3.3 V 电源是分开设计的,以免电源噪声相互干扰。把 1.8 V 模块的电源输出有效引脚 PG 连接到 3.3 V 模块的允许电压输入引脚 EN. 这样,只有当 1.8 V 电压有效之后,3.3 V 电压才开始上电,这就保证了 DM6446 的内核电压先于 L/O 电压上电。

### 3 底层软件设计

系统在 U-boot 版本 U-boot-1. 1. 3 的基础上进行移植, U-boot-1. 1. 3 目录下主要文件有: board 文件包含与系统办卡相关的文件,如 DDR2、FLASH 驱动等; driver 文件下是通用设备驱动; include 文件包含系统头文件,尤其 configs 子目录下与系统相关的配置头文件是移植过程中要修改的文件; lib\_arm 目录包含与 ARM 体系结构相关的文件; net 文件包含与网络功能相关的文件目录,如 bootp, nfs, tftp 等。

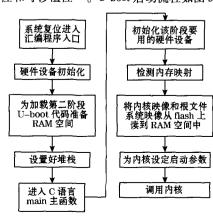

系统中 U-boot 的启动可以分为 2 个阶段。第一阶段是硬件设备初始化代码,用汇编语言实现,这部分代码包括对DM6446 的一些寄存器的初始化和将 U-boot 的第二阶段代码从Flash 拷贝到 DDR2 中. 除去第一阶段的代码,剩下的部分都是第二阶段的代码. 本系统中 U-boot 代码首先运行的是 u-boot-1. 1. 3/cpu/arm926ejs/start. S. 第二阶段的起始地址是在第一阶段代码中指定的,被复制到 DDR2 后,就从第一阶段跳到这个人口地址开始执行剩余部分代码。第二阶段主要是进行一些段设置、堆栈的初始化等工作,最后会跳转到 main 函数中,接受命令并进行命令处理。第二阶段是用 C 语言,以使代码具有更好的可读性和可移植性<sup>[3]</sup>。U-boot 启动流程如图 5 所示。

图 5 U-boot 启动流程分析图

移植过程中,在目录 u-hoot-1. 1. 3\cpu\arm926 ejs 下存放了与 CPU 相关的目录文件,u-boot-1. 1. 3\include\common. h 定义了一些基本函数,并包含了一些必要的头文件,需要了解这些文件的内容。在 u-hoot-1. 1. 3\hoard\路径下加入文件夹 davinci,添加支持本系统的文件,主要有 davinci. c,dm644x\_emac. c,flash. c,timer. c,platform. s,这些文件的主要工作是 DM6446和一些模块的硬件配置,包括系统 PLL 及 DDR2 的初始化、PSC的配置及使能 UARTO、AEMIF 等硬件模块。在 U-hoot-1. 1. 3\include\configs\目录下添加文件 davinci. h,定义芯片配置、存储器、I²C 以及 Flash 和 SDRAM 的大小等。根据系统所使用的NORFLASH型号,在 U-hoot-1. 1. 3\include\flash. h 中添加以下代码:

#define SPA MANUFACT 0x00120012

#define AMD\_ID\_GL256N\_2 0x22222222//S29GL256N 的第二个 ID #define AMD\_ID\_GL256N\_3 0x22012201 // S29GL256N 的第三个 ID

需要注意的是如果换用了不同型号的 Flash,那么就要根据用到的 Flash 型号修改 u-hoot-1.1.3/hoard/davinci/flash.c. 另外还要注意不同 Flash 的不同分区大小也会对 U-hoot 的启动造成影响。Flash 是分区使用的,每个分区的大小是 Flash 擦除块大小的整数倍。比如 AM29LV256 和 S29GL256 两款 Norflash,前者每个 sector 大小为 64 KB,后者每个 sector 大小为 128 KB,这样在进行 flash 擦除操作的时候如果定义每次擦除单元为 64 KB,则对于 S29GL256 来说就会因只擦除到区的一半而出现错误。此时就要根据情况修改 U-boot-1.1.3/common/Env\_flash.c 中的一段代码:

#ifndef CONFIG\_INFERNO

end\_addr = flash\_sect\_addr + len-1;//len = 0x10000

#else

end\_addr = flash\_sect\_addr + 0x20000-1;//以 128kB 分区时的最后一个区地址

#endif

在 Linux 控制台下,编译移植后的 U-Boot 源代码,命令如下:

#make davinci\_config

#rm tools/. depend

#make ARCH = arm CROSS\_COMPILE = arm-v5t-le-

生成的 U-Boot. bin 是二进制 bin 文件。通过 JTAG 口,在 CCS3.2 开发环境中 load 文件 flashwriter. out,然后运行,在弹出 的对话框中输入 U-boot. bin 所在路径和参数"0",把 U-boot. bin 下载到目标板的 flash 上。目标板复位后运行 U-boot,此时在 U-Boot 命令模式下可设置系统启动的环境变量,并在主机启动 tftp 服务器,用交叉网线连接主机和目标板,将准备好的 Linux 内核映像文件和文件系统映像文件分别下载到 DDR2 中正确的地址空间。如果一切运行正常,就可以在目标板上开始系统的调试。

#### 4 系统设计的难点及关键技术

设计方案中,处理器的主频高达 600 MHz, DDR2 的最高频率为 533 MHz, 这对信号完整性及电磁兼容性都有极大的要求。

视讯终端的设计中突出体现以下难点:

- (1)时序问题。工作频率的提高和信号上升/下降时间的缩短,首先会使设计系统的时序余量缩小甚至出现时序方面的问题。

- (2)传输线效应导致的信号振荡、过冲和下冲都会对设计 系统的故障容限、噪声容限及单调性造成很大的威胁。

- (3)信号沿的时间下降到1 ns 后,信号之间的串扰成为很重要的问题。

- (4) 当信号沿的时间接近 0.5 ns 时. 电源系统的稳定性和电磁干扰(EMI) 也十分关键。

视讯终端设计中采用的关键技术:

- (1)高速数字电路设计。为了提高产品的性能,电路板设计按 6 层板考虑,在元器件布局及布线过程中严格遵守高速电路设计原则,为确保系统功能的实现及整机性能指标达到检测标准.在 PCB 布线时需要特别注意申接电阻降低高速电信号反射的影响及保证同一组数据同步到达。由于信号在顶层、底层与中间层的传输阻抗和传输速率不一样,因此应尽量将接到同一器件的信号线分布在同一层上,并使导线长度相等。其中USB接口中 D+与 D-信号线必须保证为 90 Ω 差分线。网口RJ-45 接头的 3 脚和 6 脚,1 脚和 2 脚与 PHY 之间的连线应为差分线。

- (2)电源设计。电源是系统正常工作的基础. 一般来说,只要电源工作正常。都可以通过 JTAG 口将程序下载到 DM6446中,进而调试其他的模块。在设计中,应使用足够多的电源层和地层。对 AVDD、DVDD、AGND、DGND 分层设计,并将模拟地与数字地单点接地,这样可以避免模拟电路与数字电路相互影响<sup>[4]</sup>。

#### 5 结束语

TMS320DM6446 具有高速的处理能力以及丰富的多媒体人机交互接口,这就使其设计出的产品在图像质量、硬件成本、灵活性及产品更新等方面都优于专门的视频编解码芯片口。设计基于此芯片的多媒体视讯终端在实际使用中达到了设计中的要求,运行稳定,画面清晰,使用方便。文中提出的的设计方案对于同类型产品的设计具有一定的参考价值,是多媒体技术的良好运用。

#### 参考文献:

- [1] 唐川. 一种 H. 323 视频会议终端的主板的设计与实现[学位论文]. 成都:电子科技大学,2005.

- [2] 王建平,季学锋,穆道明. 基于 DSP 的多路音/视频采集处理系统设计. 国外电子元器件,2006(6).

- [3] 宋凯,甘岚,严丽平,等. U-Boot 在 S3C2410 上的移植分析. 华东交通大学学报,2005,22(5).

- [4] 熊炜. 基于 TMS320DM642 的多路视频采集处理板卡的硬件设计 与实现. 国外电子元器件,2006(6).

作者简介:白艳茹,硕士研究生,主要研究领域为嵌入式系统。

E-mail: baiyanru0821@163. com