# 串行数模转换器 TLC5620I 与 TMS320F2812 接口设计

杜磊,薛重德,任志国

(南京航空航天大学, 江苏 南京 210016)

摘要:由于TMS320F2812不具备模数转换功能,因此其应用范围有一定局限性。利用TMS320F2812 串行外设接口(SPI)模块和D/A 转换器件TLC5620I,可以解决此问题。 给出TLC5620I和TMS320F2812的接口设计,整个系统性能优越,硬件结构设计简单、经济、可靠。

关 键 词:数字信号处理器(DSP); 串行外设接口(SPI); TLC5620I; 数模转换器

中图分类号: TM930

文献标识码:A

文章编号:1674-6236(2009)11-0122-03

# Design of interface between serial digital-to-analog converter chip TLC5620I and TMS320F2812

DU Lei, XUE Zhong-de, REN Zhi-guo

(Nanjing University of Aeronautics and Astronautics, Nanjing 210016, China)

**Abstract:** The application of TMS320F2812 is limited because it has no digital-to-analog conversion function. This problem can be solved by use of the function of SPI and digital-to-analog converter chip TLC5620I. In this article, the interface design between TLC5620I and TMS320F2812 is presented, the performance of system is good. The hardware structure design is simple, economical and credible.

Key words: Digital Signal Processor (DSP); Serial Port Interface (SPI); TLC5620I; digital-to-analog converter

# 1 引言

近年来,数字信号处理器(DSP)的应用越来越广泛,其中TMS320F2812 作为目前数字控制领域中性能较高的 DSP 芯片,被广泛应用于电机控制、工业自动化、家用电器和消费电子等领域。由于 TMS320F2812 本身不具有 D/A 转换模块,因此在很多需要模拟量输出的控制场合受到限制。所以 D/A 转换芯片如何与 TMS320F2812 进行接口,成为数字信号处理系统需要解决的一个重要问题。这里介绍了四路 8 位电压输出数字 - 模拟转换器 TLC5620I,并给出 TLC5620I与TMS320F2812 串口接口的软、硬件设计实现方法。

## 2 TMS320F2812 的 SPI 工作原理

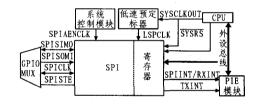

TMS320F2812 的 SPI 模块的 9 个寄存器用来控制 SPI 的操作,其中 SPICCR 设置 SPI 的软件复位、移位时钟极性字符长度;SPICTL 设置 SPI 的时钟相位、工作模式等;SPISTS 中包括溢出标志位、中断标志位等;SPIBRR 设置 SPI 波特率;SPIRXBUF 和 SPITXBUF 为数据接收和发送缓冲寄存器,SPIDAT用于发送/接收移位寄存器;SPIRXEMU 仅用于仿真;SPIPRI 控制中断优先级。该器件的 SPI 接口有一个 16 级的FIFO,用来减少 CPU 的开销。图 1 为 SPI 模块与 CPU 接口结构框图四。

由图 1 可知,SPI 模块数据传输由 40、41、34、35 引脚完

图 1 SPI 模块与 CPU 接口结构框图

成,其引脚功能见表1。

表1 引脚功能表

| 引脚名称           | 功能          |  |

|----------------|-------------|--|

| SPISIMO(第40引脚) | 从模式输入/主模式输出 |  |

| SPISOMI(第41引脚) | 从模式输出/主模式输入 |  |

| SPICLK(第34引脚)  | 串行时钟引脚      |  |

| SPISTE(第35引脚)  | 从模式发送使能     |  |

TMS320F2812 支持 125 种不同的波特率和 4 种不同的时钟模式。根据 SPI 的工作模式(从动或主控),引脚 SPICLK可分别接收一个外部的 SPI 时钟信号或由片内提供 SPI 时钟信号。

在该设计中, SPI 工作在主控模式, SPI 时钟由片内的 SPI 产生并由 SPICLK 引脚输出。TMS320F2812 波特率的设置是由系统的低速外设模块时钟频率 LSPCLK 和 SPI 主控制器中的 SPIBRR 寄存器的值决定的,其计算公式如下:

SPI 波特率=LSPCLK/(SPIBRR+1) SPIBRR=3~127

SPI 波特率=LSPCLK/4

SPIBRR=0,1,2

收稿日期:2009-05-25

稿件编号:200905067

作者简介:杜 磊(1984--),男,山东菏泽人,硕士研究生。研究方向:交流变频控制及机电一体化。

引脚 SPICLK 上的四种不同的时钟模式是由时钟极性位和时钟相位位控制的,其中时钟极性位选择时钟有效沿为上

升沿还是下降沿,时钟相位位则设定是否选择时钟的 1/2 周期延时。四种不同的时钟模式如表 2 所示。

| 表 2 | 4 | 种时钟模式 |

|-----|---|-------|

|     |   |       |

| SPLK 时钟模式 | 时钟极性 | 时钟相位 | 说明                              |

|-----------|------|------|---------------------------------|

| 无延时上升沿    | 0    | 0    | SPI 信号上升沿发送数据,下降沿接收数据           |

| 有延时上升沿    | 0    | 1    | 提前 SPICLK 信号上升沿半个周期发送数据,上升沿接收数据 |

| 无延时下降沿    | 1    | 0    | SPI 信号下降沿发送数据,上升沿接收数据           |

| 有延时下降沿    | 1    | 1    | 提前 SPICLK 信号下降沿半个周期发送数据,下降沿接收数据 |

# 3 TLC5620I 简介

TLC5620I 是四路 8 位电压输出数模转换器(DAC),带有缓冲基准输入端(高阻抗),包含上电复位功能以确保可重复启动,用 5 V 电源工作。DAC产生范围在基准电压一倍或两倍与地(GND)之间的输出电压,且 DAC 是单调变化的。

TLC5620I 使用 4 个电阻串(resistor-string)来实现 D/A 转换。每个 D/A 转换的核心是带有 256 个抽头的单电阻,分别对应 256 个可能的代码。每个电阻串的一端连接到 GND端,另一端由基准输入缓冲器的输出馈电。通过使用电阻串保持单调性。线性度取决于电阻元件的一致性以及输出缓冲器的性能。由于输入端是经过缓冲的,所以 DAC 对于基准源总是呈现为高阻抗负载。每一个 DAC 的输出由可配置增益输出放大缓冲,它可以配置为一倍或两倍增益。

通过简单的 3 线串行总线可数字控制 TLC5620I,此总线与 CMOS 兼容且易于与所有常用的微处理器作为控制器器件接口。11 位的命令字由 8 位数据(DO~D7),2 个 DAC 选择位(AO、A1)和 1 个范围位(RNG)组成。后者允许在一倍或两倍输出范围之间作选择。DAC 寄存器是双缓冲的,允许完整的新数值组写人器件,然后 DAC 输出通过 LDAC 端的控制同时更新。每个通道输出的电压 V<sub>0</sub> 由下式计算:

$V_0$ =REF×(CODE/256)×(1+RNG bit value) 式中,REF为相应通道基准电压,CODE是从数据位(D7~D0) 计算出的十进制数,RNG是范围位串行控制字的 0 或 1。

#### 4 TLC5620I 和 TMS320F2812 的接口电路

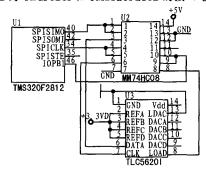

图 2 为 TLC5620I 和 TMS320F2812 的接口电路。

图 2 TLC5620I与TMS320F2812接口电路图

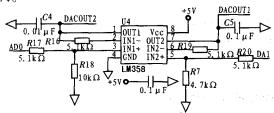

该设计中,引出 4 路 D/A 转换通道电压,均由 LM358 构

成电压跟随器输出,如图 3 所示。该图为 AD0 和 AD1 口由 LM358 组成的同向放大电路。AD2 和 AD3 的放大电路与之 相同。

图 3 LM358 组成同向放大电路

TMS320F2812 在引脚 SPISIMO 上将数据输出,与之相对应的是 TLC5620I 的 DATA 数据接收引脚;TMS320F2812 的 SPICLK 引脚和 TLC5620I 的 CLK 引脚相对应,二者共用串行时钟;TMS320F2812 的 IOPB1 模拟控制 TLC5620I 的 LOAD 引脚电平,以锁存数据,更新输出电压。在数据传输时,有两种方式控制 TLC5620I 输出电压的更新:LOAD 引脚控制更新和 LDAC 引脚控制更新。该设计采用 LOAD 引脚控制更新方式,此时,LDAC 引脚接低电平<sup>14</sup>。开始控制 LOAD 引脚控制更新方式,此时,LDAC 引脚接低电平<sup>14</sup>。开始控制 LOAD 为高电平,数据在 CLK 引脚的每一个下降沿与时钟同步从 DATA 引脚输入。当所有的数据传输完毕时,控制 LOAD 引脚跳至低电平,所选择的 D/A 通道的输出电压得到更新。由于 TLC5620I 的控制信号要求的 VIH 较高,所以需要将 DSP 输出的 SPI-CLK、SPISIMO 以及 I/O 口模拟的 CS 信号的高电平提高,该设计采用 MM74HC08 器件来实现。

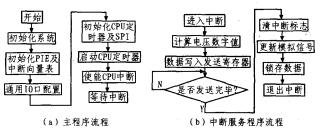

### 5 软件设计

由于 TLC5620I 的工作频率是 1 MHz, 故将 DSP 的 SPI 通信频率也设置为 1 MHz<sup>[5]</sup>。程序采用 C 语言模块化编写,其流程如图 4 所示,图 4a 主程序完成系统初始化,中断使能,等待中断等工作;图 4b 中断服务程序主要完成输出电压的

图 4 程序流程图

```

TMS320F2812 的低速外设预分频和通信频率间的关系。

void main()

InitSysCtrl(); //初始化系统

InitPieCtrl(); //初始化 PIE

Gpio_select(void);

IER !=M_INT1; //使能 CPU 中断

for(::): //等待中断

}

//发送数据子程序

void DA_OUT (unsigned CHANNEL, unsigned int RND, unsigned

int SPI_DATA)

flag=SpiaRegs.SPISTS.all & 0x40;

if(flag==0x40) break; //读中断标志位,判断是否发送完毕

SpiaRegs.SPIRXBUF=SpiaRegs.SPIRXBUF; //虚读寄存器以

清除中断标志

GpioDataRegs.GPADAT.bit.GPIOA0=0; //CS_DA=0,更新模

拟信号输出

//中断服务子程序

interrupt void cpu_timer0_isr(void)

PieCtrlRegs.PIEACK.all = PIEACK_GROUP1;

DA_OUT(0,0,Voltage); //电压范围 0~255,对应 0~3 V

DA_OUT(1,0,Voltage);

```

数字量计算和数据发送等工作。在编写程序过程中,要注意

DA\_OUT(2,0,192); //2.475 V,电压范围 0~255,对应 0~3 V DA\_OUT(3,0,128); //1.65 V,电压范围 0~255,对应 0~3 V ....

利用该实验程序,可以通过示波器在 DACOUTO 和 DACOUT1 接口输出端观测到三角波,利用万能表在 DACOUT2 接口输出端测得电压为 2.475 V,在 DACOUT3 接口输出端测得电压为 1.65 V。

# 6 结束语

以 TMS320F2812 与 TLC5620I 为例,详细讨论两者的串口通信的硬件接口及软件设计,实现数字信号到模拟信号的转换,扩展 TMS320TMS320F2812 在控制领域的应用范围<sup>10</sup>。在设计过程中,充分利用 TMS320F2812 的 SPI 模块,只有少量的数据线和控制线,使电路设计简化,提高了设计可靠性,并在实际应用中效果良好。

#### 参考文献:

- [1] 三恒星科技.TMS320TMS320F2812 DSP 原理与应用实例 [M]. 北京:电子工业出版社,2009.

- [2] 刘和平,邓力,江渝,等.数字信号处理器原理、结构及应用基础[M].北京:机械工业出版社,2007.

- [3] 朱德荣, 常云朋. 串行 D/A 转换器 TLV5638 与 DSP 的 SPI 接口设计[J]. 机床电器,2008(6):11-13.

- [4] 李 利, 陈 刚. 串行数模转换器 TLC5617 与 DSP 接口设计 [J]. 电测与仪器,2004,41(8):50-53.

- [5] Texas Instrument Inc.TLC5620C, TLC5620I Data sheet[EB/OL].2000.http://focus.ti.com/docs/prod/folders/print/tlc5620. html

- [6] 戴育良. 串行数模转换器 TLV0832 与 DSP 的接口设计[J]. 机械与电子,2007(33):100-101.

#### (上接第 119 页)

频信号(标准的正弦波),滤波效果满足系统要求,嵌入式逻辑分析仪中的输出波形如图 7 所示。

图 7 SignalTap II 的 Data 窗口中的 FIR 滤波器输出波形

#### 8 结束语

本文在 FPGA 内利用 DSPBuilder 实现 FIR 数字低通滤波器,通过 Simulink 算法仿真和 ModelSim 进行 RTL 仿真,接着在 Quartus 中进行时序仿真,最后用嵌入式逻辑分析仪 SignalTapII 进行实际测试,结果证明采用该方法设计的 FIR 数字低通滤波器功能正确,性能良好,可以提高 FIR 滤波器的设计质量,加快设计进程,验证结果直观明了。随着各类数—124—

字信号处理的 IP Cores 的进一步完善,基于 FPGA 的 DSP 系统的应用会更加广泛。

#### 参考文献:

- [1] 潘 松,黄继业,王国栋.现代 DSP 技术[M].西安:西安电子 科技大学出版社,2003.

- [2] 彭雪峰.基于 SOPC 的嵌入式导航计算机设计[D].哈尔滨:哈尔滨工程大学,2009.

- [3] 许金生,周春雪,赵从毅.基于 IP Core 的 FIR 数字滤波器的 FPGA 实现[J]. 安徽工业大学学报,2007,24(3):309-312.

- [4] 袁 博,宋万杰,吴顺军.基于 FPGA 的 MATLAB 与 Quartus II 联合设计技术研究[J].电子工程师 2007(1):6-8.

- [5] 周立功.EDA 实验与实践[M].北京:北京航空航天大学出版 社,2007.

- [6] 王传新.FPGA 设计基础[M].北京:高等教育出版社,2007.