文章编号:1007-2780(2009)05-0698-06

## TMS320F2812 与液晶显示模块的接口电路及其程序设计

黄树毅,程汉湘,荆怀成,唐清培

(广东工业大学 自动化学院,广东 广州 510006, E-mail: sure-e@163. com)

摘 要:介绍了 DSP 芯片 TMS320F2812 和液晶模块 MGLS-12032 的功能特点以及 TMS320F2812 与液晶模块之间的接口设计方法,通过适当的电路设计解决了电平不兼容的 问题。通过分析液晶模块的时序,阐述了在 TMS320F2812 中用软件模拟时序的方法,也即通过软件的方法解决了高速 DSP 处理器与慢速液晶模块之间时序不兼容的问题,实现了对液晶模块 MGLS-12032 的控制。

关 键 词: TMS320F2812; MGLS-12032; 液晶显示; 接口; 兼容

中图分类号: TN27; TP311 文献标识码: A

## 1 引 言

近年来,随着微电子技术的飞速发展,数字信 号处理器(DSP)得到越来越多的关注。TI 公司 推出的 TMS320F2812 由于具有功耗低、运算速 度快、集成度高、资源丰富、编程灵活、价格相对低 廉等优点,而成为电子设计中使用最为广泛的 DSP 芯片之一。由于具有较强的运算能力, TMS320F2812 可在满足实时控制要求的同时, 支持一个良好的人机界面。人机界面产品由硬件 和软件两部分组成,硬件部分包括处理器、显示单 元、输入单元、通讯接口、数据存贮单元等。显示 单元是其中一个重要的组成部分,是实现人机交 互的窗口。由于受到体积、功耗和电磁干扰等多 方面的制约,目前 CRT 显示器已经较少应用于 人机界面系统;而 LCD 液晶显示器,由于具有体 积小、重量轻、功耗低、寿命长、稳定性高、无辐射 等诸多优点,现已在数字控制系统和电子仪表等 领域得到了极为广泛的应用[1]。

本文采用间接访问的方式设计了数字信号处理器和液晶模块之间的接口电路,通过软件的方法解决了高速 DSP 处理器与慢速液晶模块之间时序不兼容的问题,实现了对液晶模块 MGLS-12032 的控制。所提出的设计方案已应用于有源电力滤波器项目中,实际应用证明,采用此方案的液晶模块能够在强电磁干扰、电压波动等恶劣环

境下稳定运行。

2 TMS320F2812 与 MGLS-12032 的接口电路

#### 2.1 TMS320F2812 数字信号处理器

TMS320F2812 是美国德州仪器公司推出的 新一代32位定点数字信号处理器,该芯片采用高 性能静态 CMOS 技术,使其供电电压降至 3.3 V 并具有 150 MIPS 的运算能力;采用哈佛总线结 构,可单周期执行 32 位×32 位的乘和累加操作 (MAC)或双 16 位×16 位 MAC 运算;片上存储 器包括 128K×16 位 Flash 存储器、1K×16 位的 OPT 存储器和 14K×16 位的 SARAM;同时,128 位密匙可有效保护 Flash/OPT 和 SARAM 中的 内容不被解密;具有外部中断扩展(PIE)模块,可 支持多达 45 个的外部中断,两个多功能的事件管 理器(EVA, EVB)可方便地实现电机控制;集成 了 16 通道 12 位的高速 ADC, 其转换速率约为 80 ns/12.5 MSPS;最多可达 56 个的可编程通用输 人/输出(GPIO)引脚,此外还有极为丰富的串行 接口外设,包括串行外设接口(SPI)、两个串行通 信接口(SCI)、增强型局域网络控制器(eCAN)和 多通道缓冲串口(McBSP)[2]。

#### 2.2 MGLS-12032 液晶模块

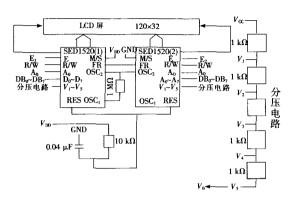

MGLS-12032 液晶模块为 120×32 点阵,内

嵌有两个 SED1520 控制芯片。其结构框图如图 1 所示。

图 1 MGLS-12032 液晶模块结构图

Fig. 1 Diagram of MGLS-12032 LCD module

由图 1 可以看出,SED1520(1)为主方式工作,OSC<sub>1</sub> 和 OSC<sub>2</sub> 跨接一个电阻,并由 OSC<sub>2</sub> 输出时序信号;SED1520(2)为从方式工作,时钟由 SED1520(1)的 OSC<sub>2</sub> 端提供。两芯片的选通由  $E_1$ 、 $E_2$  信号决定。MGLS-12032 液晶模块在横向上可分为 4 页,每 1 页有 8 行,则总共有 32 行;而在纵向上可细分为 120 列,每个 SED1520 芯片分别控制左右半屏的 60 列<sup>[3]</sup>。

要实现对该液晶模块的控制,关键是对其内 嵌的控制芯片 SED1520 进行正确的操作。 SED1520 的主要特性如下:

- (1)内置 2 560 位显示 RAM 区,RAM 中的 1 位数据控制液晶屏上一个像素的亮、暗状态:"1"表示亮,"0"表示暗;

- (2)具有 16 个行驱动输出和 61 个列驱动输出:

- (3)可直接与80系列微处理器相连,也可直接与68系列微处理器相连;

- (4)驱动占空比为 1/16 或 1/32;

- (5)可以与 SED1520 级联使用,以便扩展行、 列驱动能力。

#### 2.3 接口电路设计

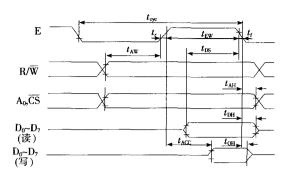

SED1520 有两种读/写操作时序,分别对应于 6800 系列 MPU 和 8080 系列 MPU。由于在 MGLS-12032 液晶显示模块中,两个 SED1520 芯片的 RES 端上电后经一定时间升为高电平,所以 其控制时序被选择为 68 系列 MPU 时序。68 系列 MPU 时序如图 2 所示。

MGLS-12032 液晶模块与 MPU 之间可有两

图 2 SED1520 时序

Fig. 2 Timing chart of SED1520

#### 表 1 SED1520 时序特性

Table 1 Timing characteristics of SED1520

| 参数                           | 最小值(ns)        | 最大值(ns) |

|------------------------------|----------------|---------|

| 系统周期时间(t <sub>cyc</sub> )    | 1 000          | _       |

| 地址建立时间(t <sub>AW</sub> )     | 20             | _       |

| 地址保持时间(tAH)                  | 10             | _       |

| 数据建立时间(写)(t <sub>DS</sub> )  | 80             |         |

| 数据保持时间(写)(t <sub>DH</sub> )  | 10             | _       |

| 数据保持时间(读)(t <sub>OH</sub> )  | 10             | 60      |

| 数据读取时间(读)(t <sub>ACC</sub> ) | and the second | 90      |

| 使能脉冲宽度(读)(tew)               | 100            | _       |

| 使能脉冲宽度(写)(t <sub>EW</sub> )  | 80             | _       |

种接口方式:一种是直接访问方式,就是把液晶模 块当成一个存储器,对其直接进行读写操作;另一 种是间接访问方式,把液晶模块当成一个终端,通 过 MPU 的并口进行访问操作[4]。在以上两种方 式中,直接访问方式比较常见,其主要优点是软件 编程简单且不占用并口等 I/O 口资源。但直接 访问方式也有一些不足之处,比如,相对于 TMS320F2812 DSP 而言,液晶模块是一种慢速 设备,与 DSP 的时序不兼容,如果采用直接访问 方式,则必须在两者之间加入适当的缓冲电路以 及相应的译码电路,结构比较复杂[5];同时,在实 际的应用系统中经常有可能要接外部存储器,若 液晶模块采用直接访问方式,那意味着外部存储 器将和液晶模块共用外部数据总线,如果外部存 储器和液晶模块的时序不一致,那么处理器要对 这两种设备进行读写操作时则不得不频繁地设置 外部数据总线的读写速度,以分别兼容这两种设 备的时序,这样不但增加了程序的复杂性也大幅 降低了整个系统的运行效率。所以,直接访问方 式比较适合于外部数据存储器未被占用或者 I/O 口资源比较紧张的系统。

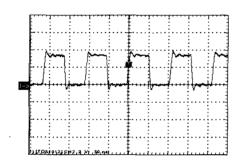

TMS320F2812 具有多达 56 个的可编程通用输入/输出(GPIO)引脚,所以可充分利用这一优势,使用其中一部份 GPIO 引脚作为液晶显示模块的接口。这样,既简化了接口电路,也减少了对数字信号处理器外部数据总线的占用,不影响处理器对外部存储器的读写操作,更重要的是GPIO 口的速度小于外部数据总线的速度<sup>[6]</sup>,有利于与慢速液晶模块的兼容。图 3 是处理器的CPU 频率达到 150 MHz 时,通过一个死循环程序让 I/O 口电平不断翻转(即 I/O 口所能达到的最高输出频率)的波形。

图 3 从 TMS320F2812 的 I/O 口以最高频率输出的波形 Fig. 3 Maximal frequency output waveform from the I/O port of TMS320F2812

从图 3 可以看出处理口的最高输出频率约为 9.3 MHz,一个周期内高电平的最小维持时间约 为 54 ns。参照表 1 的时序特性,可知 I/O 口的输出特性与液晶模块的时序特性大致相符,只是当 I/O 以最大速率输出时则无法满足  $t_{DS}$  和  $t_{EW}$  的要求。为了保证即使在 I/O 口以最高速率且从同一 I/O 反复输出数据的极限条件下仍能与液晶模块的时序相兼容,在程序设计时可加入适当的延时,具体方法将在程序设计部分说明。

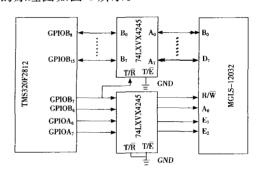

在 TMS320F2812 数字信号处理器中,GPIOA和GPIOB两组I/O口都具有16个引脚,可以方便地实现与液晶显示模块相接。TMS320F2812的GPIO口是功能复用的,既可工作于通用I/O端口模式,也可工作于特定功能模式。为了保留信号处理器的两组PWM输出口,以备它用,优先考虑选用GPIOB。~GPIOB15端与

液晶模块的 $D_0 \sim D_7$ 端相接,而 GPIOB<sub>6</sub>、GPIOB<sub>7</sub>端分别控制液晶模块的  $A_0$ 、R/W端,GPIOA<sub>6</sub>、GPIOA<sub>7</sub>分别控制液晶模块的  $E_1$ 、 $E_2$ 端,既可方便地实现对液晶模块的控制,同时又保留了数字信号处理器比较有用的 PWM 输出端口。最后需要注意的问题是:处理器所输出的电平为 0 V 与 3.3 V 的 CMOS 电平,而液晶模块是 0 与 5 V 的 TTL 电平。为了增强液晶模块的稳定性,同时确保处理器的安全,在进行接口设计时必须加入相应的电平转换电路。在设计中采用了 8 位双电源供电的双向驱动器 74LVX4245,通过控制该驱动器的  $T/\overline{R}$ 端便可控制数据的传送方向,方便处理器进行读、写操作[7]。通过以上措施,电平兼容问题得到了很好的解决。处理器与液晶模块硬件接口的原理图如图 4 所示。

图 4 TMS320F2812 与 MGLS-12032 接口电路 Fig. 4 Interface circuit of TMS320F2812 and MGLS-12032

为了能够实现对液晶模块进行读写操作,GPIOB<sub>8</sub>~GPIOB<sub>15</sub>上的数据必须是双向传送的,因此第一个双向驱动器的 T/R 端受控于 GPI-OB<sub>7</sub> 的读写操作信号。而第二个双向驱动器由于所接信号为控制信号只需单向传送,因此其 T/R 直接与地相接即可。

## 3 显示程序的设计

{

MGLS-12032 液晶模块共有 13 种控制指令, 具体指令可参阅文献[2]。要实现对液晶模块的 正确控制,就必须适当地运用这些指令,向液晶模 块传送相应的数据。以下是根据液晶模块的控制 指令并结合图 2 所示的时序图所编写的基本子程 序以供调用。主要 C 语言子程序如下<sup>[8]</sup>:

prl(unsigned int com) //写指令代码子程序 (E1),参数 com 为要执行的指令。

```

unsigned int temp;

clr_a0();

clr_rw();

temp = (GpioDataRegs. GPBDAT. all &=

0x00FF);

GpioDataRegs. GPBDAT. all = (temp |

(com << 8));

set_el(); //使 E 为高电平

delay(5); //延时环节。

clr_el(); //使 E 为低电平

pr2(unsigned int data) //写显示数据子程序

(E1),参数 data 为字符的点阵数据。

{

unsigned int temp;

data <<=8;

set_a0();

clr_rw();

temp = (GpioDataRegs. GPBDAT. all &=

0x00FF);

```

```

GpioDataRegs. GPBDAT. all=(temp|data);

set_e1(); //使 E 端为高电平

delay(5); //延时环节。

clr_e1(); //使 E 端为低电平

```

针对前文所提到的在极限条件下(处理器工作于最高频率,并以最大速率从同一 I/O 口反复输出数据)有可能出现数据建立时间( $t_{DS}$ )和使能脉冲宽度( $t_{EW}$ )不能满足要求,从图 2 的时序图中可以看出: $t_{DS}$ 和  $t_{EW}$ 都和 E 为高电平时所维持的时间密切相关,因此,只要延长 E 为高电平的时间就能同时延长  $t_{DS}$  和  $t_{EW}$ 。为此,在程序中的"set\_e1()"(使 E 为高电平)之后加入了一个延时环节"delay(5)"再清除 E 的高电平状态。这样便可保证在任何条件下都能符合液晶模块的时序特性<sup>[9]</sup>。以上两个子程序是对液晶模块左半屏的SED1520(1)芯片进行控制,类似地,可以编写出pr3,pr4 子程序,以实现对右半屏 SED1520(2)芯片进行控制。在调用以上子程序之前,还必须先做好如下定义:

```

# define set a0() GpioDataRegs. GPBSET. bit. GPIOB<sub>6</sub> = 1

//使 A。端为高电平

# define clr_a0()

GpioDataRegs. GPBCLEAR. bit. GPIOB_6 = 1

//使 A。端为低电平

# define set_rw() GpioDataRegs. GPBSET. bit. GPIOB<sub>7</sub> = 1

//使 R/W 端为高电平

# define clr_rw() GpioDataRegs. GPBCLEAR. bit. GPIOB<sub>7</sub> = 1

//使 R/W 端为低电平

GpioDataRegs. GPASET. bit. GPIOA<sub>6</sub> = 1

//使 E<sub>1</sub> 端为高电平

# define set_el()

//使 E1 端为低电平

GpioDataRegs. GPACLEAR. bit. GPIOA<sub>6</sub> = 1

# define clr_e1()

//延迟子程序

void delay(unsigned int i)

while(i--);

```

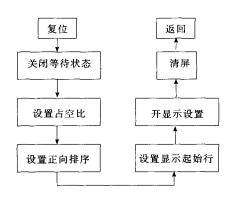

图 5 液晶模块初始化子程序流程图 Fig. 5 Flowchart of initialize routine of LCD module

在开机或给液晶模块上电时,一般都要先经过初始化才能正常使用,其初始化的子程序流程如图 5 所示。

上述的液晶模块初始化子程序既具有对模块 初始化的功能,同时也具有对整个液晶模块进行 清屏的功能,所以当需要对整个液晶模块实行清 屏时只需调用该子程序即可实现。

## 4 结 论

采用间接访问方式设计了液晶模块与 DSP 处理器之间的接口电路,利用处理器系统多余的 I/O 口与液晶模块相接,在软件的控制下模拟出

与液晶模块相兼容的时序,其优点是不占用系统的外部总线资源,不会对处理器读写其它外部存储器造成干扰,保证了系统的运行效率。在所介绍的 DSP 处理器系统中,由于 I/O 口的读写速度小于外部总线的读写速度并基本上能与液晶时序相匹配,只是在最高速度条件下个别时间(如数据建立时间)不能满足要求,所以只须在程序中适当处加入一个延时环节,即可保证 DSP 处理器运行于最高速度以下的任何状态都能与液晶模块的时序相兼容。从总体上看,间接访问方式的接口电路比较简洁,只需在液晶模块与处理器之间接入两个双向驱动器即可实现电平兼容;在软件方面,可根据液晶模块和处理器 I/O 口的时序特性灵

活编程,很容易实现两者之间的时序兼容。本方案可以推广到其它型号的液晶模块或处理器,特别适合于处理器的外部总线资源紧张但有多余的 I/O 口可供利用的系统。在应用于其它的系统时,须根据实际情况设计合适的电平转换电路以及在控制程序中增加适当的延时环节(当处理器I/O 口速度小于液晶模块所能接受的最高读写速度时,则可不必添加延时环节),从而实现处理器和液晶模块之间的电平和时序都相兼容,确保液晶模块能够正确、稳定地工作。所提出的设计方案已应用于有源电力滤波器项目中,实际应用证明,采用此方案的液晶模块能够在强电磁干扰、电压波动等恶劣环境下稳定运行。

#### 参考文献:

- [1] 李维諟,郭强. 液晶显示应用技术 [M]. 北京:电子工业出版社,2000.

- [2]徐科军,张瀚,陈智渊, TMS320X281X DSP 原理与应用[M],北京:北京航空航天大学出版社,2006.

- [3]北京精电蓬远显示技术有限公司,内藏 SED1520 控制器图形液晶显示模块使用手册 [R], 2002.

- [4] 鄂飞,程汉湘,吴春芳,等. ADMC401 与液晶模块 MGLS-12032 接口电路及其应用 [J]. 液晶与显示,2005,20(3): 254-259.

- [5] 杨保亮,蒲琪,代祥俊. 基于 TMS320F2812 控制的液晶显示屏的设计和实现 [J]. 山东理工大学学报,2007,21(3): 88-89

- [6] Texas Instruments Incorporated. TMS320C281X system control and Interrupts reference guide (Rev. B) [R/OL]. [2009-03-10]. http://www.ti.com/digitalcontrol.

- [7] 余华芳,刘健. 单片机与液晶显示模块的软硬件接口技术 [J]. 液晶与显示,2003,18(2):125-129.

- [8] Texas Instruments Incorporated. TMS320C28X DSP CPU and instruction set reference guide (Rev. D) [R/OL]. [2009-03-10]. http://www.ti.com/digitalcontrol.

- [9] 刘勇,蔡延财,陈永冰. 基于 TMS320F2812&CPLD 的液晶显示驱动设计 [J]. 终端与显示技术,2006,(3):142-143.

# Design of Interface Circuit and Program for TMS320F2812 and LCD Module

HUANG Shu-yi, CHEN Han-xiang, JING Huai-cheng, TANG Qing-pei (Faculty of Automation, Guangdong University of Technology, Guangzhou 510006, China, E-mail: sure-e@163.com)

#### **Abstract**

TMS320F2812 digital signal processor and MGLS-12032 LCD module are introduced. The interface circuit between the digital signal processor and the LCD module is discussed. By designing a proper interface circuit between the DSP controller and the LCD module, the problem of electrical level compatibility is settled. According to the timing chart of the LCD module, this paper shows how to design LCD display program to control the LCD module properly. By this way the compatibility

problem between a high speed device and a low speed one is solved well.

Key words: TMS320F2812; MGLS-12032; LCD; interface; compatibility

作者简介:黄树毅(1983一),男,广东汕头人,硕士研究生,主要从事电工理论与新技术的研究。

## 科技参考文献著录的规则

根据中华人民共和国国家标准"文后参考文献著录规则"(GB/T7714-2005),《液晶与显示》编辑部希望广大作者在向本刊投稿时注意参考文献的著录。

1. 文后参考文献书写格式

期刊:[序号]作者.文献题名[文献类型标志].连续出版物题名:其他题名信息,年份,卷号(期号):起止页码[引用日期].获取和访问路径.

例:[1]凌志华. STN-LCD 技术的发展[J]. 液晶与显示,2002,17(4):233-242.

例:[2]李晓东,张庆红,叶瑾琳. 气候学研究的若干理论问题[J]. 北京大学学报:自然科学版, 1999,35(1):101-106.

例:[3]邵喜斌,王丽娟,李梅.a-Si:H TFT 亚阈值区 SPICE 模型的研究[J/OL]. 液晶与显示, 2005,20(4):267-272. [2005-10-18]. http://www.wanfangdata.com.cn/src/szhqk/wf\_szhqk\_browser. Asp.

专著:[序号]作者.题名[文献类型标志].析出文献其他责任者//专著主要责任者.专著题名:其他题名信息.版本项(第1版略).出版地:出版者,出版年:析出文献的页码[引用日期].获取和访问路径.

例:[4]周其凤,王新久. 液晶高分子[M]. 北京:科学出版社,1994:27-38.

例:[5]日本学术振兴会第 142 委员会. 液晶器件手册[M]. 黄锡珉,黄辉光,李之熔,译. 北京:航空工业出版社,1992.

例:[6]母国光. 白光光学信息处理及期彩色摄影术[M]//陈星旦. 光学与光学工程,北京:科学出版社,2005:62-72.

例:[7]赵耀东.新时代的工业工程师[M/OL].台北:天下文化出版社,1998[1998-09-26]. httq://www.ie. nthu. edu. tw/inf/ie. newie. htm(Big5).

例:[8]陈兵,徐寿颐.新型烷基环已基炔类液晶的合成与性质[C]//2002 年中国平板显示会议论文集.深圳;深圳天马微电子股份有限公司,2002;167-168.

例:[9]闫石. 液晶光控取向膜材料的研究[D]. 长春:中国科学院长春光学精密机械与物理研究 所,2001.

例:[10]全国文献工作标准化技术委员会第七分委员会.GB/T5795-1986 中国标准书号[S].北京:中国标准出版社,1986.

专利:[序号]专利所有者.专利题名:专利国别,专利号[文献类型标志].公告日期或公开日期[引用日期].获取和访问路径.

例:[11]吕永积,王群伟,邵佑军,等. 平板真空摄像器件:中国,ZL95241185.7[P]. 1997-08-09.

(下转 P734)