# TMS320C674x/OMAP-L1x Processor Serial ATA (SATA) Controller

# **User's Guide**

Literature Number: SPRUGJ8B August 2010

| Prefa | ice     |                                                                   | . 7 |

|-------|---------|-------------------------------------------------------------------|-----|

| 1     | Introdu | ction                                                             | . 9 |

|       | 1.1     | Purpose of the Peripheral                                         | . 9 |

|       | 1.2     | Features Supported                                                | 10  |

|       | 1.3     | Features Not Supported                                            | 10  |

|       | 1.4     | Functional Block Diagram                                          | 10  |

|       | 1.5     | Terminology Used in this Document                                 | 11  |

|       | 1.6     | Industry Standard(s) Compliance                                   | 12  |

| 2     | Archite | cture                                                             | 13  |

|       | 2.1     | Clock Control                                                     | 13  |

|       | 2.2     | Signal Description                                                | 14  |

|       | 2.3     | Pin Multiplexing                                                  | 14  |

|       | 2.4     | Interfacing to Single and Multiple Devices                        | 14  |

|       | 2.5     | DMA                                                               | 15  |

|       | 2.6     | Transport Layer                                                   | 15  |

|       | 2.7     | Link Layer                                                        | 15  |

|       | 2.8     | Phy                                                               | 15  |

|       | 2.9     | Reset                                                             | 16  |

|       | 2.10    | Initialization                                                    | 16  |

|       | 2.11    | Interrupt Support                                                 | 17  |

|       | 2.12    | EDMA Event Support                                                | 18  |

|       | 2.13    | Power Management                                                  | 18  |

| 3     | Use Cas | ses                                                               | 18  |

|       | 3.1     | General Utilities: Structures and Subroutines Sample Program Uses | 19  |

|       | 3.2     | Example on Initialization and Spinning Up Device                  |     |

|       | 3.3     | Example of DMA Write Transfer                                     | 34  |

|       | 3.4     | Example of DMA Read Transfer                                      | 35  |

| 4     | Registe | rs                                                                | 36  |

|       | 4.1     | HBA Capabilities Register (CAP)                                   | 38  |

|       | 4.2     | Global HBA Control Register (GHC)                                 | 39  |

|       | 4.3     | Interrupt Status Register (IS)                                    |     |

|       | 4.4     | Ports Implemented Register (PI)                                   |     |

|       | 4.5     | AHCI Version Register (VS)                                        |     |

|       | 4.6     | Command Completion Coalescing Control Register (CCC_CTL)          |     |

|       | 4.7     | Command Completion Coalescing Ports Register (CCC_PORTS)          |     |

|       | 4.8     | BIST Active FIS Register (BISTAFR)                                |     |

|       | 4.9     | BIST Control Register (BISTCR)                                    |     |

|       | 4.10    | BIST FIS Count Register (BISTFCTR)                                |     |

|       | 4.11    | BIST Status Register (BISTSR)                                     |     |

|       | 4.12    | BIST DWORD Error Count Register (BISTDECR)                        |     |

|       | 4.13    | BIST DWORD Error Count Register (TIMER1MS)                        |     |

|       | 4.14    | Global Parameter 1 Register (GPARAM1R)                            |     |

|       | 4.15    | Global Parameter 2 Register (GPARAM2R)                            | 50  |

# TEXAS INSTRUMENTS

| 4.16       | Port Parameter Register (PPARAMR)                    | 51        |

|------------|------------------------------------------------------|-----------|

| 4.17       | Test Register (TESTR)                                | 52        |

| 4.18       | Version Register (VERSIONR)                          | 53        |

| 4.19       | ID Register (IDR)                                    | 53        |

| 4.20       | Port Command List Base Address Register (P0CLB)      | 54        |

| 4.21       | Port FIS Base Address Register (P0FB)                | 54        |

| 4.22       | Port Interrupt Status Register (P0IS)                | 55        |

| 4.23       | Port Interrupt Enable Register (P0IE)                | 57        |

| 4.24       | Port Command Register (P0CMD)                        | 58        |

| 4.25       | Port Task File Data Register (P0TFD)                 | 61        |

| 4.26       | Port Signature Register (P0SIG)                      | 61        |

| 4.27       | Port Serial ATA Status (SStatus) Register (P0SSTS)   | 62        |

| 4.28       | Port Serial ATA Control (SControl) Register (P0SCTL) | 63        |

| 4.29       | Port Serial ATA Error (SError) Register (P0SERR)     | 64        |

| 4.30       | Port Serial ATA Active (SActive) Register (P0SACT)   | 66        |

| 4.31       | Port Command Issue Register (P0CI)                   | 66        |

| 4.32       | Port Serial ATA Notification Register (P0SNTF)       | 67        |

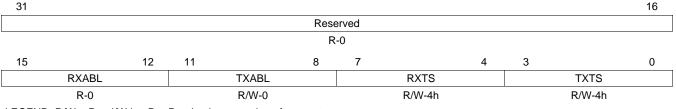

| 4.33       | Port DMA Control Register (P0DMACR)                  | <b>68</b> |

| 4.34       | Port PHY Control Register (P0PHYCR)                  | 70        |

| 4.35       | Port PHY Status Register (P0PHYSR)                   |           |

| Appendix A | Revision History                                     | 75        |

|            |                                                      |           |

# List of Figures

| 1  | SATA Subsystem Functional Block Diagram                  | 10              |

|----|----------------------------------------------------------|-----------------|

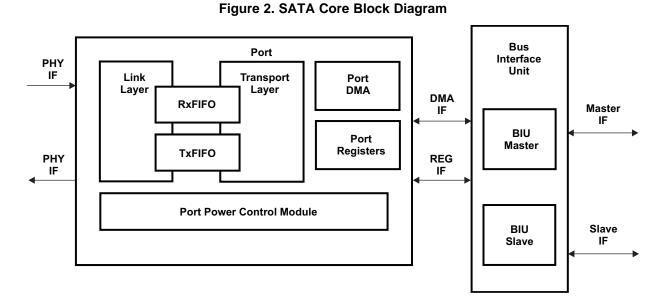

| 2  | SATA Core Block Diagram                                  | 11              |

| 3  | HBA Capabilities Register (CAP)                          | 38              |

| 4  | Global HBA Control Register (GHC)                        | 39              |

| 5  | Interrupt Status Register (IS)                           | 40              |

| 6  | Ports Implemented Register (PI)                          | 41              |

| 7  | AHCI Version Register (VS)                               | 41              |

| 8  | Command Completion Coalescing Control Register (CCC_CTL) | 42              |

| 9  | Command Completion Coalescing Ports Register (CCC_PORTS) | 43              |

| 10 | BIST Active FIS Register (BISTAFR)                       | 44              |

| 11 | BIST Control Register (BISTCR)                           | 45              |

| 12 | BIST FIS Count Register (BISTFCTR)                       | 47              |

| 13 | BIST Status Register (BISTSR)                            | 47              |

| 14 | BIST DWORD Error Count Register (BISTDECR)               | 48              |

| 15 | BIST DWORD Error Count Register (TIMER1MS)               | 48              |

| 16 | Global Parameter 1 Register (GPARAM1R)                   | 49              |

| 17 | Global Parameter 2 Register (GPARAM2R)                   | <b>5</b> 0      |

| 18 | Port Parameter Register (PPARAMR)                        | 51              |

| 19 | Test Register (TESTR)                                    | 52              |

| 20 | Version Register (VERSIONR)                              | 53              |

| 21 | ID Register (IDR)                                        | 53              |

| 22 | Port Command List Base Address Register (P0CLB)          | 54              |

| 23 | Port FIS Base Address Register (P0FB)                    | 54              |

| 24 | Port Interrupt Status Register (POIS)                    | 55              |

| 25 | Port Interrupt Enable Register (P0IE)                    | 57              |

| 26 | Port Command Register (P0CMD)                            | <b>58</b>       |

| 27 | Port Task File Data Register (P0TFD)                     | 61              |

| 28 | Port Signature Register (P0SIG)                          | 61              |

| 29 | Port Serial ATA Status Register (P0SSTS)                 | 62              |

| 30 | Port Serial ATA Control Register (P0SCTL)                | 63              |

| 31 | Port Serial ATA Error Register (P0SERR)                  | <b>6</b> 4      |

| 32 | Port Serial ATA Active Register (P0SACT)                 | 66              |

| 33 | Port Serial ATA Active (SActive) Register (P0SACT)       | 66              |

| 34 | Port Serial ATA Notification Register (POSNTF)           | 67              |

| 35 | Port DMA Control Register (P0DMACR)                      | <mark>68</mark> |

| 36 | Port PHY Control Register (P0PHYCR)                      | 70              |

| 37 | Port PHY Status Register (P0PHYSR)                       | 74              |

|    |                                                          |                 |

## List of Tables

| 1  | MPY Bit Field of P0PHYCR                                                    | 13 |

|----|-----------------------------------------------------------------------------|----|

| 2  | Signal Descriptions                                                         | 14 |

| 3  | SATASS Memory Summary                                                       |    |

| 4  | SATA Controller Registers                                                   |    |

| 5  | HBA Capabilities Register (CAP) Field Descriptions                          |    |

| 6  | Global HBA Control Register (GHC) Field Descriptions                        |    |

| 7  | Interrupt Status Register (IS) Field Descriptions                           |    |

| 8  | Ports Implemented Register (PI) Field Descriptions                          |    |

| 9  | AHCI Version Register (VS) Field Descriptions                               |    |

| 10 | Command Completion Coalescing Control Register (CCC_CTL) Field Descriptions |    |

| 11 | Command Completion Coalescing Ports Register (CCC_PORTS) Field Description  | 43 |

| 12 | BIST Active FIS Register (BISTAFR) Field Descriptions                       |    |

| 13 | BIST Control Register (BISTCR) Field Descriptions                           | 45 |

| 14 | BIST FIS Count Register (BISTFCTR) Field Description                        | 47 |

| 15 | BIST Status Register (BISTSR) Field Description                             | 47 |

| 16 | BIST DWORD Error Count Register (BISTDECR) Field Description                | 48 |

| 17 | BIST DWORD Error Count Register (TIMER1MS) Field Description                | 48 |

| 18 | Global Parameter 1 Register (GPARAM1R) Field Descriptions                   | 49 |

| 19 | Global Parameter 2 Register (GPARAM2R) Field Descriptions                   | 50 |

| 20 | Port Parameter Register (PPARAMR) Field Descriptions                        | 51 |

| 21 | Test Register (TESTR) Field Descriptions                                    | 52 |

| 22 | Version Register (VERSIONR) Field Description                               | 53 |

| 23 | ID Register (IDR) Field Description                                         | 53 |

| 24 | Port Command List Base Address Register (P0CLB) Field Description           | 54 |

| 25 | Port FIS Base Address Register (P0FB) Field Description                     | 54 |

| 26 | Port Interrupt Status Register (P0IS) Field Descriptions                    | 55 |

| 27 | Port Interrupt Enable Register (P0IE) Field Descriptions                    | 57 |

| 28 | Port Command Register (P0CMD) Field Descriptions                            | 58 |

| 29 | Port Task File Data Register (P0TFD) Field Descriptions                     | 61 |

| 30 | Port Signature Register (P0SIG) Field Description                           | 61 |

| 31 | Port Serial ATA Status Register (P0SSTS) Field Descriptions                 | 62 |

| 32 | Port Serial ATA Control Register (P0SCTL) Field Descriptions                | 63 |

| 33 | Port Serial ATA Error Register (P0SERR) Field Descriptions                  | 64 |

| 34 | Port Serial ATA Active Register (P0SACT) Field Description                  | 66 |

| 35 | Port Serial ATA Active (SActive) Register (P0SACT) Field Description        | 66 |

| 36 | Port Serial ATA Notification Register (POSNTF) Field Description            | 67 |

| 37 | Port DMA Control Register (P0DMACR) Field Description                       | 68 |

| 38 | Port PHY Control Register (P0PHYCR) Field Descriptions                      | 70 |

| 39 | Port PHY Status Register (P0PHYSR) Field Description                        | 74 |

| 40 | Document Revision History                                                   | 75 |

6

#### About This Manual

This document describes the serial ATA (SATA) controller. The SATA controller is the successor of the parallel ATA/ATAPI controller that has served as the choice of the communication medium between a portable computer (PC) and a hard-disk drive for several decades.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320C674x Digital Signal Processors (DSPs) and OMAP-L1x Applications Processors. Copies of these documents are available on the Internet at <u>www.ti.com</u>. *Tip:* Enter the literature number in the search box provided at www.ti.com.

The current documentation that describes the DSP, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <a href="http://www.ti.com/c6000">www.ti.com/c6000</a>.

- SPRUGM5 TMS320C6742 DSP System Reference Guide. Describes the C6742 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

- SPRUGM6 TMS320C6746 DSP System Reference Guide. Describes the C6746 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

- SPRUGJ7 TMS320C6748 DSP System Reference Guide. Describes the C6748 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

- <u>SPRUGM7</u> OMAP-L138 Applications Processor System Reference Guide. Describes the System-on-Chip (SoC) including the ARM subsystem, DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, ARM interrupt controller (AINTC), and system configuration module.

- SPRUFK9 TMS320C674x/OMAP-L1x Processor Peripherals Overview Reference Guide. Provides an overview and briefly describes the peripherals available on the TMS320C674x Digital Signal Processors (DSPs) and OMAP-L1x Applications Processors.

- SPRUFK5 TMS320C674x DSP Megamodule Reference Guide. Describes the TMS320C674x digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

7

- <u>SPRUFE8</u> *TMS320C674x DSP CPU and Instruction Set Reference Guide.* Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C674x digital signal processors (DSPs). The C674x DSP is an enhancement of the C64x+ and C67x+ DSPs with added functionality and an expanded instruction set.

- <u>SPRUG82</u> *TMS320C674x DSP Cache User's Guide.* Explains the fundamentals of memory caches and describes how the two-level cache-based internal memory architecture in the TMS320C674x digital signal processor (DSP) can be efficiently used in DSP applications. Shows how to maintain coherence with external memory, how to use DMA to reduce memory latencies, and how to optimize your code to improve cache efficiency. The internal memory architecture in the C674x DSP is organized in a two-level hierarchy consisting of a dedicated program cache (L1P) and a dedicated data cache (L1D) on the first level. Accesses by the CPU to the these first level caches can complete without CPU pipeline stalls. If the data requested by the CPU is not contained in cache, it is fetched from the next lower memory level, L2 or external memory.

# Serial ATA (SATA) Controller

#### 1 Introduction

During these times, the parallel ATA (PATA) interface has gone through changes to sustain the demands of the newly emerging applications needs. However, the PATA controller reached a point where it required major changes to satisfy the upcoming applications requirements and this led to its successor, the birth of the SATA controller. This device has a built-in SATA controller with a single HBA port operating in Advanced Host Controller Interface (AHCI) mode and is used to interface to data storage devices at both 1.5 Gbits/second and 3.0 Gbits/second line speeds. AHCI describes a system memory structure that contains a generic area for control and status, and a table of entries describing a command list where each command list entry contains information necessary to program an SATA device, and a pointer to a descriptor table for transferring data between system memory and the device.

#### 1.1 Purpose of the Peripheral

The SATA controller addresses the drawback of the PATA interface architecture, throughput, and protocol perspectives. PATA required 40/80 wire parallel cable with a length requirement not exceeding 18 inches. With the current hardware design, PATAs maximum transfer rate saturated to a 133 Mbytes/second of transfer. In addition to newly added features, like Hot swapping and native command queuing, the SATA controller abandoned the parallel physical interface and transitioned to a serial format using two differential pairs supporting up to 3 Mbits/second transfer rate, translating to a 300 Mbytes/second raw throughput.

With the intent on handling the previous and current role of the PATA controller and addressing the future needs, the SATA controller is architected with the option of operating in a Legacy mode, a mode that behaves similar to the PATA controller from the protocol/driver perspective, and a new AHCI mode that is different from the Legacy mode allowing it to overcome the drawbacks of PATA as well as extending PATAs capabilities. The SATA controller that is supported by this device supports AHCI mode of operation only. AHCI is a PCI class device that acts as a data movement engine between system memory and serial ATA devices. However, the AHCI controller on this device is integrated within the core chipset, a common attribute for embedded devices. The AHCI controller supported has no support for Legacy mode of operation.

Communication between a device and software moves from the task file via byte-wide accesses to a command FIS located in system memory that is fetched by the HBA. This reduces command setup time significantly, allowing for many more devices to be added to a single host controller. Software no longer communicates directly to a device via the task file. In other words, all data transfers between the device and system memory occur through the HBA acting as a bus master to system memory. Whether the transaction is of a DMA type or a PIO type (the use of the PIO command type is strongly discouraged and all transfers should be performed using DMA unless otherwise that a transaction is only performed via PIO command), the HBA fetches and stores data to memory, offloading the CPU. There is no accessible data port. Software written for AHCI is not allowed to utilize any of the legacy mechanisms to program devices.

The SATA controller uses a less massive thinner flexible cable that can be up to 3 feet (1 meter) in length allowing for easier routing and better air ventilation inside a case. Its power budget is significantly reduced to 250 mV compared to the required 5V power of PATA.

Like its predecessor, the SATA controller is most commonly used by PCs and portable devices to interface a host processor with data storage or CD/audio devices. It also has the support for hot swapping capability. It also supports the use of a Port Multiplier to increase the number of devices that can be attached to the single HBA port.

TEXAS INSTRUMENTS

www.ti.com

Introduction

#### 1.2 Features Supported

The main features of the SATA controller are:

- Synopsis DWH Serial ATA 1.5 Gbps and 3 Gbps speeds core

- Support for the AHCI controller spec 1.1

- Integrated TI SERDES PHY

- Integrated Rx and Tx data buffers

- Supports all SATA power management features

- Internal DMA engine per port

- Hardware-assisted native command queuing (NCQ) for up to 32 entries

- 32-bit addressing

- Supports port multiplier with command-based switching

- Activity LED support

- Mechanical presence switch

- Cold presence detect

#### 1.3 Features Not Supported

Features not supported in this SATA controller are:

- Legacy mode of operation

- Master/slave type of configuration

- Far-end analog loopback

- Message signaled interrupts

- 64-bit addressing

#### 1.4 Functional Block Diagram

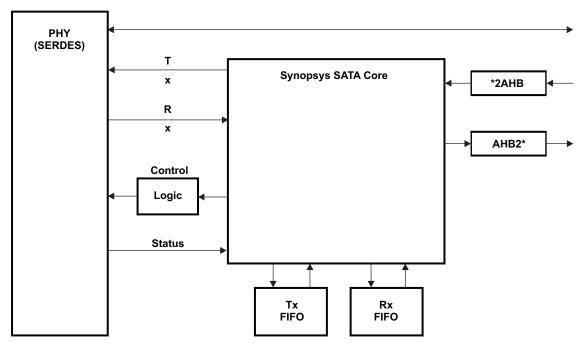

The SATA subsystem (SATASS) is a fully contained serial ATA host with built-in DMA. It uses the AHCI standard for communication with a SATA device. It has no support for the Legacy mode of operation. Figure 1 shows a high-level block diagram of the SATA subsystem (core and the integrated TI PHY). Figure 2 shows a high-level block diagram of the SATA core.

Figure 1. SATA Subsystem Functional Block Diagram

## 1.5 Terminology Used in this Document

The following is a brief explanation of some terms used in this document:

| Term         | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AHCI         | Advanced host controller Interface (necessary for implementing newly supported features like native command queuing). Freon device supports only this mode of operation, i.e., has no support for Legacy mode. It also reduces CPU/Software overhead when moving data in and out of the system memory. Note that system software is responsible to ensure that queued and non-queued commands are not mixed in the command list. |

| ATA/ATAPI    | AT attachment/ATA packet interface                                                                                                                                                                                                                                                                                                                                                                                               |

| CF           | Compact Flash                                                                                                                                                                                                                                                                                                                                                                                                                    |

| device       | External SATA or ATAPI device attached to the SATA controller                                                                                                                                                                                                                                                                                                                                                                    |

| DMA          | DMA within the ATA controller, not the processor EDMA system                                                                                                                                                                                                                                                                                                                                                                     |

| DWORD        | DWORD is 32 bits of data.                                                                                                                                                                                                                                                                                                                                                                                                        |

| command list | A memory buffer for as much as 32 commands. Each command is entered in a command slot. This is a required feature when supporting command queuing.                                                                                                                                                                                                                                                                               |

| command slot | A subset of the command list. It is the memory buffer for a single command. A total of 32 command slots exist.                                                                                                                                                                                                                                                                                                                   |

| D2H          | Device to HBA. Mostly used to indicate the direction of the transmission of FIS that is from device to the HBA (host).                                                                                                                                                                                                                                                                                                           |

| FIS          | Frame Information Structure. A frame is made of a data payload with computed CRC and a start and end primitives.                                                                                                                                                                                                                                                                                                                 |

| H2D          | HBA to device. Mostly used to indicate the direction of the transmission of FIS that is from HBA (host) to device.                                                                                                                                                                                                                                                                                                               |

| HBA          | Host bus adapter. It is the SATA controller that implements the AHCI specification to communicate between system memory and Serial ATA devices.                                                                                                                                                                                                                                                                                  |

| Legacy mode  | This mode of operation makes the user access (application software or driver) to view the SATA controller in a similar fashion as a PATA controller. This device does not support this mode of operation but AHCI mode of operation.                                                                                                                                                                                             |

| OOB          | Out of band. OOB signaling is used for during device detection and when recovering from power states.                                                                                                                                                                                                                                                                                                                            |

Introduction

| <b>Term</b><br>PORT | <b>Meaning</b><br>Refers to HBA port mainly, within this document. However, the PORT is also be used<br>to refer to a port of a PORT Multiplier.                                                                                                                                                         |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | to refer to a port of a PORT Multiplier.                                                                                                                                                                                                                                                                 |

| PRD                 | Physical region descriptor. A PRD table is a data structure used by DMA engines that comply with the ATA/ATAPI Host Adapters standard. The PRD describes memory regions to be used as the source or destination of data during DMA transfers. A PRD table is often referred to as a scatter/gather list. |

| РМ                  | Port Multiplier. A Port Multiplier allows extending an HBA port connection capability to connect to multiple SATA devices, a maximum of 15 devices. Note that the operating bandwidth is shared amongst all the Devices when using this type of configuration                                            |

| SATA controller     | Serial ATA controller, also HBA.                                                                                                                                                                                                                                                                         |

| System memory       | The memory that is external from the SATA controller but is a memory that is accessible by the built in SATA controller DMA or the CPU.                                                                                                                                                                  |

## 1.6 Industry Standard(s) Compliance

This module is compliant with the SATA revision 2.6 Gold standard and the AHCI revision 1.1 specifications.

#### 2 Architecture

This section discusses the architecture of the Serial ATA Controller. The Serial ATA Controller supports Advanced Host Controller Interface (AHCI) operation only. It does not support the Legacy mode of operation. Since the controller complies with the AHCI standard (version 1.1) the details of its operation is detailed within the AHCI version 1.1 specification. See the specification for the general behavior of the SATA Core operation. The SATA Controller supported within the Freon device has a single HBA port.

#### 2.1 Clock Control

The SATA controller uses two internal clocks (SYSCLK2 and SYSCLK4) and one external differential clock (REFCLKP/N) for its operation. SATA controller access to CPU and its resources is implemented through, SYSCLK2 (PLL0 output frequency divided by 2). SYCLK2 to the SATA controller is gated by the PSC and is required to be enabled prior to accessing the SATA controller. SYCLK4 (PLL0 output frequency divided by 4), is the keep alive clock and is always ON.

A high quality low jitter external differential clock is required as a source clock input for the PHY and the frequency of the input clock should be between 75MHz and 375 MHz (depending upon the supported multiplier used). Maximum Jitter should not exceed 50ps pk-pk. Duty cycle must be between 40 and 60%. Nominal Rise/fall time should be 700 ps.

This input frequency requirement is dependent upon the supported PHY PLL multiplier value. The MPY field of the port PHY control register (P0PHYCR) is programmed with the PLL multiplier value based on the input frequency clock. Note that the PHY PLL output frequency should be exactly 1.5GHz (for both 3 and 1.5 Gbits/Sec line rate) and its accuracy is very important to the operation of the SATA controller.

Table 1 shows the MPY bit field of P0PHYCR for supported PHY PLL multiplier values.

| MPY Bit Field Value | Effect   |

|---------------------|----------|

| 0                   | Reserved |

| 1h                  | 5×       |

| 2h                  | 6×       |

| 3h                  | Reserved |

| 4h                  | 8×       |

| 5h                  | 10×      |

| 6h                  | 12×      |

| 7h                  | 12.5×    |

| 8h                  | 15×      |

| 9h                  | 20×      |

| Ah                  | 25×      |

| Bh-Fh               | Reserved |

#### Table 1. MPY Bit Field of P0PHYCR

#### 2.2 Signal Description

This device has bonded the Data lines (two sets of differential data lines) along the pins necessary for detecting device insertion, power supply needs and powering a device. The power pins necessary to power up a cold SATA device should be handled external to the device, on the board along the signal path connector.

| Terminal Name  | Туре   | Description                                                                       |

|----------------|--------|-----------------------------------------------------------------------------------|

| SATA_RXP       | Input  | SATA receive data (positive)                                                      |

| SATA_RXN       | Input  | SATA receive data (negative)                                                      |

| SATA_TXP       | Output | SATA transmit data (positive)                                                     |

| SATA_TXN       | Output | SATA transmit data (negative)                                                     |

| SATA_REFCLKP   | Input  | SATA PHY reference clock (positive)                                               |

| SATA_REFCLKN   | Input  | SATA PHY reference clock (negative)                                               |

| SATA_MP_SWITCH | Input  | SATA mechanical presence switch input                                             |

| SATA_CP_DET    | Input  | SATA cold presence detect input                                                   |

| SATA_CP_POD    | Output | SATA cold presence power-on output                                                |

| SATA_LED       | Output | SATA LED control output                                                           |

| SATA_REG       | Output | SATA PHY PLL regulator output. Requires an external 0.1 $\mu$ F filter capacitor. |

| SATA_VDDR      | Power  | SATA PHY 1.8V internal regulator supply                                           |

| SATA_VDD       | Power  | SATA PHY 1.2V logic supply                                                        |

| SATA_VSS       | Ground | SATA PHY ground reference                                                         |

#### Table 2. Signal Descriptions

#### 2.3 Pin Multiplexing

Extensive pin multiplexing is used to accommodate the largest number of peripheral functions in the smallest possible package. Pin multiplexing is controlled using a combination of hardware configuration at device reset and software programmable register settings. Refer to the device-specific data manual to determine how pin multiplexing affects the SATA.

#### 2.4 Interfacing to Single and Multiple Devices

The SATA Controller supports a single HBA port. This HBA port can be used to interface directly to a single SATA device or to multiple SATA devices via a Port Multiplier. Note that on a multiple target setup, the available bandwidth will be shared amongst all the attached devices.

Note that Port Multipliers and Power Supplies for external SATA devices, when needed, should be furnished external to the device. However, the appropriate signals for controlling power and device detection are bonded and can be controlled via software.

#### 2.4.1 Interfacing to a Single Device

If you need to interface directly to a single device, there is no need of populating a Port Multiplier. The software needs to ensure that the PMP field within the Command Header and the PM\_PORT field of the FIS be cleared at all times.

If the external SATA device is not Self Powered, it is the responsibility of the System Designer to populate and furnish the right power supply needed. Consult the SATA specification for details.

#### 2.4.2 Interfacing to Multiple Devices

Interfacing to multiple devices is similar to interfacing with a single device, except the existence of a Port Multiplier on the setup. The couple of additional tasks from the software perspective is that the requirement for the software to detect and configure the Port Multiplier prior and then after when accessing individual SATA devices, the software is required to populate the PMP filed of the Command Headers and PM\_PORT field of the FISes with the Port Multiplier Port value.

#### 2.5 DMA

The HBA port contains two DMA engines: one to fetch commands from the command list and one to move FISes in and out of system memory.

The DMA used to move FISes in and out of system memory has a port DMA control register (P0DMACR) to control the burst transfer. This DMA is used to transfer all information between system memory and the attached SATA device, as well as configuration and status FISes.

You can program the maximum burst size that is issued on the system bus independently for both reads and writes. The DMA issues transactions this size or smaller (in DWORD increments). This is used to optimize burst size for overall system throughput efficiency. See Section 4.33 for details on valid values. Note that programming a burst size of greater than a transaction size, while not invalid, is meaningless because the DMA maximizes out at transaction size.

You can also program the transaction size for both receive and transmit (see Section 4.33). The transaction size is the minimum amount of data that the DMA works on. For example, if there is a FIS coming from the device to the host, the DMA does not begin transferring data into system memory until there is at least rx\_transaction\_size (RXTS) data in the receive FIFO. During transmit, the DMA reads data from system memory in tx\_transaction\_size (TXTS) increments to put into the transmit FIFO. Note that transactions may be broken up into multiple bursts based on burst size, crossing of a 1K boundary, or end-of-frame.

#### 2.6 Transport Layer

The transport layer handles all of the transport layer functions of the SATA protocol. During reception, it receives a FIS from the Link layer via the Rx FIFO, decodes the type, and routes it to the proper location via the port DMA. During transmission, it transfers a FIS constructed by the port DMA to the link layer via the Tx FIFO. It also passes link layer errors and checks for transport layer errors to pass up to the system.

The transport layer also contains the Tx and Rx FIFOs. These FIFOs are used as asynchronous data buffers between the serial domain and the bus clock domain. The size of these FIFOs affects the subsystems ability to buffer data before flow control must be asserted. It also affects the maximum programmable transaction and burst sizes that can be programmed into the port DMA. The Tx FIFO size is 32 DWORDS (124 bytes) deep and the Rx FIFO size is 64 DWORDS (256 bytes) deep.

#### 2.7 Link Layer

The link layer maintains the link and supports all SATA link layer functionality including:

- Out-of-band (OOB) transmit signaling

- Frame negotiation and arbitration

- Envelope framing/de-framing

- CRC calculation (receive and transmit)

- 8b/10b encoding/decoding

- Flow control

- Frame acknowledgment and status

- Data width conversion

- Data scrambling/descrambling

- Primitive transmission

- Primitive detection and dropping

- Power management

#### 2.8 Phy

The SATASS includes an integrated TI SERDES macro as a phy. The phy handles all of the serialization/de-serialization, symbol alignment, and Rx OOB signal detection. There is some logic between the Synopsis core and the SERDES for control and configuration.

#### 2.9 Reset

SATA peripheral reset is handled using the power and sleep controller (PSC). For detailed information on power management procedures using the PSC, see your device-specific *System Reference Guide*. Other types of resets supported by the SATA controller are part of the AHCI specification is discussed within the AHCI specification 1.1. See the standard specification for the details on HBA reset, port rest and software reset.

#### 2.10 Initialization

Proper initialization of the HBA is required after power-up to ensure proper operation of the SATA controller peripheral. The initialization process starts by performing a write to one-time write-only registers, this is documented as firmware initialization within the AHCI specification, where the values written depends on the features that the applications supports followed by software initialization. This part of the initialization is similar to what a PC BIOS does and allows you to enable/disable some features by software.

The software can then continue with a normal initialization that is required by the software and the details and sequence of initialization done here is also documented within the AHCI specification. In general, all resources that are required by the AHCI controller, PHY initialization, structures and memories for Command Slots, FIS, and Data Memories are configured and the FIS DMAs is enabled. The software will then spin-up the device and ensure that a proper Device Detection and Speed Negotiation has completed prior to enabling the Command DMA.

Note that DMA Configuration/Initialization should take place after Device Detection and Speed Negotiation. If done earlier, the default value is used (this is the recommended setting) since RESET removes the initialized value. The only time it is advisable to change the DMA Configuration is if you need to prioritize System Resource access. It also requires that the Command DMA is not running (POCMD.ST = 0) when modifying the value of the DMA Configuration fields.

#### 2.10.1 Initialization (Firmware and Software)

Software reads the HBA capabilities register (CAP), ports implemented register (PI), AHCI version register (VS), global parameter 1 register (GPARAM1R), global parameter 2 register (GPARAM2R), and the port parameter register (PPARAMR) to obtain information about the subsystems capabilities. The software should then take the following steps to configure each port for operation:

- 1. Do all firmware capability writes.

- 2. Setup all appropriate structures in memory as per the AHCI specification.

- 3. Configure the PHY using the port PHY control register (P0PHYCR):

- (a) Set the MPY bit field for the PLL multiply factor.

- (b) Set LOS = 1 (enable loss of signal detection)

- (c) Set ENPLL = 1 (enable the PLL)

- 4. Set the port command list base address register (P0CLB).

- 5. Set the port FIS base address register (P0FB).

- 6. Set appropriate bits in the port command register (P0CMD).

- 7. Program the port serial ATA control register (POSCTL).

- 8. Wait for Device Detection and Speed Negotiation to end.

- 9. Program the port DMA control register (P0DMACR).

- 10. Enable the appropriate interrupts.

- 11. Enable FIS reception in P0CMD.

- 12. Spin-up the device(s), if necessary.

#### 2.10.2 Issuing a Command

Once the host and device are configured, perform the following steps to issue a command:

- 1. Create the appropriate FIS in system memory.

- 2. Create the PRD.

- 3. Queue the command to the command queue list (location specified by the port command list base address register (POCLB).

For detailed information, see the AHCI Specification Version 1.1.

#### 2.11 Interrupt Support

The AHCI controller supports both standard interrupt sourcing, where interrupts are generated when enabled events occur, or a different type method of generating interrupts that minimize interrupt loading by either generating interrupts in a batch or periodically.

The interrupt handling method where interrupt loading issue is a factor is handled using Command Completion Coalescing method.

#### 2.11.1 Command Completion Coalescing

Command Completion Coalescing (CCC) is a feature designed to reduce the interrupt and command completion overhead in a heavily loaded system. The feature enables the number of interrupts taken per completion to be reduced significantly, while ensuring a minimum quality of service for command completions. When software specified number of commands have completed or a software specified timeout has expired, an interrupt is generated by hardware to allow software to process completed commands. the command completion coalescing ports register (CCC\_PORTS) should be programmed with 1 to indicate that the single available port, Port0, is selected.

For a detailed explanation of the CCC initialization and usage, see the AHCI Specification 1.1 Section 11.6.

#### 2.11.1.1 CCC Interrupt Based on Timer Expiration

When CCC is enabled and the desired method to receive an interrupt is based on a timer elapse condition, then you need to communicate a resolution for a 1ms time by programming the BIST DWORD error count register (TIMER1MS) with the VBUS cycle count derived from the VBUS clock frequency sourced to the SATA controller. For a DSP clock frequency of 300 MHz, the VBUS Clock is 150 MHz and the 1ms cycle count is 150 MHz/1000 = 150000. This means that when the TV bit in the command completion coalescing control register (CCC\_CTL) is a non-zero value and the EN bit in CCC\_CTL is set to 1 (CCC is enabled), it will take 15 ms or 15 × 150000 = 2,250,000 VBUS cycles for the timer to elapse and when it does, the CCC generates an interrupt. This happens periodically until disabled.

**NOTE:** Make sure the CC bit in the command completion coalescing control register (CCC\_CTL) is cleared to 0.

#### 2.11.1.2 CCC Interrupt Based on Completion Count

When CCC is enabled and the desired method to receive an interrupt is based on a completion count, that is, the CC bit in the command completion coalescing control register (CCC\_CTL) is programmed with a non-zero value and the CCC interrupt is enabled (EN bit in CCC\_CTL is set to 1), an interrupt is sourced from the SATA controller when the programmed desired number of interrupt is received.

**NOTE:** Make sure the TV bit in the command completion coalescing control register (CCC\_CTL) is cleared to 0.

Architecture

#### 2.11.2 Non CCC Interrupt Configuration

For a standard interrupt handling method where every event that is enabled generates an interrupt, is handled as follows. For more information, see the AHCI Specification.

After insuring that CCC is disabled, the EN bit in the command completion coalescing control register (CCC\_CTL) is 0, in order for the SATA Core to source interrupts, the interrupt should be enabled at both the global level (the IE bit in the global HBA control register (GHC) is 1) and at the port level by enabling the bit fields for the desired interrupt. An enable bit at a Port level that control interrupts dispatch to the processor interrupt handling resource. So long as the CPU interrupt handler is configured properly, the CPU receives the interrupt when the enabled event occurs.

#### 2.12 EDMA Event Support

The SATA controller makes use of its own built-in DMA and has no need nor utilizes the processor EDMA.

#### 2.13 Power Management

The SATA controller can be placed in reduced power modes to conserve power during periods of no use. The main power management of the peripheral is controlled by the processor power and sleep controller (PSC). The PSC acts as a master controller for power management of all of the peripherals on the processor. For detailed information on power management procedures using the PSC, see your device-specific *System Reference Guide*.

During times of the SATA peripheral use, the SATASS supports the industry standard power-down modes (both Partial and Slumber low-power modes) as provided within the SATA specification. These modes allow for power savings through powering down part of the SERDES PHY and the ability to gate off the clocks to the link layer. The Port Power Control Module is used to enter and exit these modes that may have the normal functional clocks gated off.

**NOTE:** When SATA communication is in the idle state, that is, when no disk activity takes place, the communication remains active with both the host and the device sending a logical sync primitive and scrambled data at the speed negotiated continuously. For power sensitive applications, the power consumed during the disk inactivity stage might be undesirable and it might be a desired task to place the communication interface into an electrical idle (Partial or Slumber) state until data transfer activity is needed in order to conserve power.

#### 3 Use Cases

The following sections include some sample program snippets that can be used as a guide for software development. The example demonstrates one of the ways of creating the necessary structures; properly aligned system memory resources, initialization, as well as performing basic DMA Read/Write transfer using Couple of Command Slots.

Section 3.1 contains examples in relations to System Memory resource allocations, Structures, and Subroutines used by the Initialization and Read/Write Transfer functions. The remaining sections include examples of basic Initialization, DMA Write transfer, and DMA Read transfer examples.

TEXAS INSTRUMENTS

www.ti.com

3.1

```

General Utilities: Structures and Subroutines Sample Program Uses

/* Allocating memory for Command List. The structure pointed to by this

address range is 1K-bytes in length and must be 1K-byte aligned.

Note that each command header occupies 32 bytes of memory and 32

command headers require 1024 bytes of memory.

*/

#pragma DATA_SECTION(CmdLists,

".L3_BUF");

#pragma DATA_ALIGN(CmdLists, 1024);

CmdListHeader CmdLists[32]={0};

/* Indicates the 32-bit physical address of the command table, which

contains

the command FIS,

ATAPI Command,

andPRD table.

This address must be aligned to a 128-bytes of memory,

* /

#pragma DATA_SECTION(CmdTable,

".L3 BUF");

#pragma DATA_ALIGN(CmdTable, 128);

CommandTable CmdTable[LISTLENGTH];

/* Indicates the 32-bit base physical address for received FISes. The

structure pointed to by this address range is 256 bytes in length

and must be 256-byte aligned.

*/

#pragma DATA_SECTION(RcvFis,

".L3_BUF");

#pragma DATA_ALIGN(RcvFis, 256);

ReceiveFis RcvFis;

#pragma DATA_SECTION(prdTableDataBuff,

".L3 BUF");

unsigned char prdTableDataBuff[LISTLENGTH][PRDLENGTH][DATABUFFERLEN];

#define NUMOFPORTS

(1)

// Freon Supports A Single HBA Port. However it can support up to

11

16 additional Ports with the use of an external Port Multiplier.

11

So keep this value to 1.

// Max Command Header Per Port is 32

#define LISTLENGTH

(2)

#define WRITE_CMD_SLOT

(0)

// Value used here should be <= LISTLENGTH-1

#define READ_CMD_SLOT

// Value used here should be <= LISTLENGTH-1

(1)

// WARNING. PRDLENGTH can not be greater than 8 for this program.

// See Note captured by the area when memory has been reserved for

// within sata_utilities.c for Command Table "CmdTable" for

// more information.

#if 1

#define _MAX_DATA_TRANSFER_ // Define this in project file when needed.

#endif

#ifndef _MAX_DATA_TRANSFER_

// 512 Bytes Data Size within 2 PRD Descriptors.

#define PRDLENGTH (2) // Max PRD Length is 65535 per port.

#define DATABUFFERLEN (256) // DMA Data Buffer Length

#else // Max Data Size Transfer 8K Bytes within 2 PRD Descriptors

// Max PRD Length is 65535 per port.

#define PRDLENGTH

(2)

#define DATABUFFERLEN (2*4096)

// DMA Data Buffer Length

#endif

#if ((PRDLENGTH > 8) | (WRITE_CMD_SLOT > LISTLENGTH-1) | (READ_CMD_SLT > LISTLENGTH-1))

#error PRDLENGTH ENTRY ERROR - PROGRAM HARD CODED FOR MAX VALUE OF 8 - CMD SLOT ENTRY ERROR

#endif

// GOASFASTASDEVICE, GEN1, GEN2

#define DESIRED_SPEED

(GEN1)

(0x0000002) // Dev28bitLbaAddress = 28-Bit LBA Address

#define DEVICE_LBA_ADDRESS

#define WAIT_500_MILLISECONDS

// This should be set to 500 once the ONE_MS_VALUE is

(50)

programmed correctly.

#define WAIT 1 MILLISECOND

(1)

#define ONE_MS_VALUE

(1)

// Number of CPU Cycles needed to generate a millisecond

wait time.

// [0x0 - 0x9] Burst=2^(-1) i.e., 0x8=> 2^(9-

#define DMA_BURST_LENGTH

(0x9)

1)=256

#define DMA TRANSACTION SIZE

(0x4)

// [0x0 - 0xA] TransSize=2^n i.e., 0xA=> 2^10=1024

```

```

Texas

Instruments

```

```

www.ti.com

```

```

Use Cases

\prime\prime Maximum of 32 commands slots per port exist where each command occupies 8 DWs (64 Bytes).

// The structure 'CmdListHeader' defines a single command header definition.

// The start of the first Command List &CmdListHeader[0] needs to be programmed onto POCLB.

11

// Command List Base Address should be 1K Byte Aligned.

typedef struct {

Uint32 CmdLen:5; //bits[4:0]

Uint32 Atapi:1; //bit[5]

Uint32 Write:1;

//bit[6]

Uint32 Prefetch:1; //bit[7]

Uint32 Reset:1; //bit[8]

Uint32 Bist:1;

//bit[9]

Uint32 Rok:1;

//bit[10]

//bit[11]

Uint32 Rsv:1;

Uint32 Pmp:4;

//bits[15:12]

Uint32 Prdtl:16; //bits[31:16]

}CmdListHeaderW0;

typedef struct {

Uint32 PrdByteCnt; //bits[31:0]

}CmdListHeaderW1;

typedef struct {

Uint32 CmdTableAddLowRsv:7; //bit[6:0]

11

Uint32 CmdTableAddLow:25; //bits[31:7]

11

Uint32 CmdTableAddLow; //bits[31:7]

}CmdListHeaderW2;

typedef struct {

Uint32 CmdTableAddHigh; //bits[31:0]

}CmdListHeaderW3;

typedef struct {

CmdListHeaderW0 DW0;

CmdListHeaderW1 DW1;

CmdListHeaderW2 DW2;

CmdListHeaderW3 DW3;

Uint32

DW4;

Uint32

DW5;

Uint32

DW6;

Uint 32

DW7;

} CmdListHeader;

typedef struct {

Uint32 B0FisType:8;//bits[7:0]

Uint32 BYTE1:8; //bits[15:8]

Uint32 B2Cmd:8; //bits[23:16]

Uint32 B3Feature:8;//bits[31:24]

{CmdFisWord0;

typedef struct {

Uint32 B0LbaLow:8; //bits[7:0]

Uint32 BlLbaMid:8; //bits[15:8]

Uint32 B2LbaHigh:8;//bits[23:16]

Uint32 B3Device:8; //bits[31:24]

}CmdFisWord1;

typedef struct {

Uint32 B0LbaLowExp:8; //bits[7:0]

Uint32 B1LbaMidExp:8; //bits[15:8]

Uint32 B2LbaHighExp:8;//bits[23:16]

Uint32 B3FeatureExp:8; //bits[31:24]

{CmdFisWord2;

typedef struct {

Uint32 B0SecCnt:8;

//bits[7:0]

Uint32 BlSecCntExp:8; //bits[15:8]

```

```

TEXAS

INSTRUMENTS

```

```

www.ti.com

```

```

Uint32 B2Rsv:8;

//bits[23:16]

Uint32 B3Control:8; //bits[31:24]

{CmdFisWord3;

typedef struct {

Uint32 DWResv; //bits[31:0]

}CmdFisWord4;

typedef struct {

CmdFisWord0 DW0;

CmdFisWord1 DW1;

CmdFisWord2 DW2;

CmdFisWord3 DW3;

CmdFisWord4 DW4;

Uint32

DW5;

Uint 32

DW6;

Uint32

DW7;

Uint 32

DW8;

Uint32

DW9;

Uint32

DW10;

Uint 32

DW11;

Uint32

DW12;

Uint32

DW13;

Uint32

DW14;

Uint32

DW15;

{CommandFIS;

//-----Command FIS end ATAPI Command -----

// ATAPI Command Data Structure

typedef struct {

Uint32 ATAPI[4];

}Atapi;

//-----ATAPI Command end PRDT -----

// Physical Region Descriptor Table Data Structure

typedef struct {

Uint32 DbaLow;

//bits[31:0]

}DbaAddressLow;

typedef struct {

Uint32 DbaHigh; //bits[31:0]

}DbaAddressHigh;

typedef struct {

Uint32 DW2Reserved; //bits[31:0]

}PrdtRsv;

typedef struct {

Uint32 DataBC:22; //bits[21:0]

}DataByteCnt;

typedef struct {

DbaAddressLow DW0;

DbaAddressHigh DW1;

PrdtRsv

DW2;

DataByteCnt

DW3;

} prdt ;

//----PRDT end -----

//-----Command Table Data Structure ------

// Since Command Table has to be 128 bytes = 0x80 bytes aligned if supporting more

// than a single Command Header, then need to make sure that the Array you are

// creating for all associated Command Tables match the 128 bytes alignment.

// In order to do so, the number of PRD Table length you are allocating should be

// multiples of 8.

typedef struct {

CommandFIS cfis;

Atapi

atapi;

Uint32

Rsv[12];

// Have forced this size to 8 in order to meet the minimum

prdTable[16];

PRDT

// required size for Command Table.

```

Use Cases

{CommandTable;

```

//----Command Table Data Structure end ---

// Receive FIS requires the Receive FIS to be 256 byte aligned. POFB should be programmed

// with this restriction.

11

// RECEIVE FIS Data Structure

// Members: DMA Setup FIS (DSFIS)

11

PIO Setup FIS (PSFIS)

//

D2H Register FIS (RFIS)

11

Set Device Bits FIS (SDBFIS)

11

Unknown FIS (UFIS)

//-----DMA Setup FIS-----

typedef struct {

Uint32 B0FisType:8;//bits[7:0]

Uint32 BYTE1:8;

//bits[15:8]

//bits[23:16]

Uint32 B2Rsv:8;

Uint32 B3Rsv:8; //bits[31:24]

}DsfisW0;

typedef struct {

DsfisW0 DW0;

Uint32 DW1DmaBuffLow;

Uint32 DW2DmaBuffHigh;

Uint32 DW3Rsv;

Uint32 DW4DmaBuffOffset;

Uint32 DW5DmaXfrCnt;

Uint32 DW6Rsv;

}DMASetupFis;

//-----DMA Setup FIS end PIO Setup FIS ----

typedef struct {

Uint32 B0FisType:8;//bits[7:0]

Uint32 BYTE1:8; //bits[15:8]

Uint32 B2Status:8; //bits[23:16]

Uint32 B3Errror:8;//bits[31:24]

}PioSetupDW0;

typedef struct {

Uint32 B0LbaLow:8; //bits[7:0]

Uint32 BlLbaMid:8; //bits[15:8]

Uint32 B2LbaHigh:8;//bits[23:16]

Uint32 B3Device:8; //bits[31:24]

}PioSetupDW1;

typedef struct {

Uint32 B0LbaLowExp:8; //bits[7:0]

Uint32 BlLbaMidExp:8; //bits[15:8]

Uint32 B2LbaHighExp:8;//bits[23:16]

Uint32 B3Rsv:8;

//bits[31:24]

}PioSetupDW2;

typedef struct {

Uint32 B0SecCnt:8; //bits[7:0]

Uint32 BlSecCntExp:8; //bits[15:8]

Uint32 B2Rsv:8; //bits[23:16]

Uint32 B3Estatus:8; //bits[31:24]

}PioSetupDW3;

typedef struct {

Uint32 HW0XferCnt:16; //bits[15:0]

Uint32 HW1Rsv:16;

//bits[31:16]

}PioSetupDW4;

```

```

typedef struct {

PioSetupDW0 DW0;

PioSetupDW1 DW1;

PioSetupDW2 DW2;

PioSetupDW3 DW3;

PioSetupDW4 DW4;

}PIOSetupFis;

//-----PIO Setup FIS end D2H Reg FIS------

typedef struct {

Uint32 B0FisType:8;//bits[7:0]

Uint32 BYTE1:8; //bits[15:8]

Uint32 B2Status:8; //bits[23:16]

Uint32 B3Errror:8;//bits[31:24]

}D2HRegDW0;

typedef struct {

Uint32 B0LbaLow:8; //bits[7:0]

Uint32 BlLbaMid:8; //bits[15:8]

Uint32 B2LbaHigh:8;//bits[23:16]

Uint32 B3Device:8; //bits[31:24]

}D2HRegDW1;

typedef struct {

Uint32 B0LbaLowExp:8; //bits[7:0]

Uint32 B1LbaMidExp:8; //bits[15:8]

Uint32 B2LbaHighExp:8;//bits[23:16]

Uint32 B3Rsv:8; //bits[31:24]

}D2HRegDW2;

typedef struct {

Uint32 B0SecCnt:8; //bits[7:0]

Uint32 BlSecCntExp:8; //bits[15:8]

Uint32 HW1Rsv:16; //bits[31:16]

}D2HRegDW3;

typedef struct {

Uint32 WORsv;

//bits[31:0]

}D2HRegDW4;

typedef struct {

D2HRegDW0 DW0;

D2HRegDW1 DW1;

D2HRegDW2 DW2;

D2HRegDW3 DW3;

D2HRegDW4 DW4;

}D2HRegFis;

//----D2H Reg FIS end Set Device Bits FIS-

\ensuremath{\prime\prime} // The Set Device Bit FIS definition does not contain the 2nd Word required

// for Native Command Queueing. This second word is the SACTVE register and

^{\prime\prime} the AHCI takes care of updating SACTIVE register at its location.

typedef struct {

Uint32 B0FisType:8;//bits[7:0]

Uint32 BYTE1:8; //bits[15:8]

Uint32 B2Status:8; //bits[23:16]

Uint32 B3Errror:8; //bits[31:24]

}SetDevBitsDW0;

typedef struct {

Uint32 W1Rsv;

//bits[31:0]

}SetDevBitsDW1;

typedef struct {

SetDevBitsDW0 DW0;

SetDevBitsDW1 DW1;

}SetDevBitsFis;

```

//----Set Device Bits FIS end Unkonwn FIS-

TEXAS INSTRUMENTS

```

typedef struct {

Uint32 UserDefined; //bits[31:0]

}UnknownDWx;

typedef struct {

UnknownDWx DW[16]; // 16 Words (Max 64 Bytes allowed)

}UnknownFis;

//-----Unkonw FIS end-----

//-----Receive Register FIS Structure-----

typedef struct {

DMASetupFis

DSFIS;

Uint32

Rsv1;

PIOSetupFis

PSFIS;

Uint32

Rsv2[3];

D2HRegFis

RFIS;

Uint32

Rsv3;

SetDevBitsFis SDBFIS;

UnknownFis

UFIS;

}ReceiveFis;

/

typedef struct {

Uint8 cfisType;

Uint8 cfisBytel;

Uint8 cfisCmd;

Uint8 cfisFeature;

Uint8 cfisDwlSecNumLbaLow;

Uint8 cfisDw1Cy1LowLbaMid;

Uint8 cfisDwlCylHighLbahigh;

Uint8 cfisDw1Dev;

Uint8 cfisDw2SecNumLbaLowExp;

Uint8 cfisDw2CylLowLbaMidExp;

Uint8 cfisDw2CylHighLbahighExp;

Uint8 cfisDw2FeatureExp;

Uint8 cfisDw3SecCnt;

Uint8 cfisDw3SecCntExp;

Uint8 cfisDw3Ctrl;

}cmdFis;

typedef struct {

Uint8 dsfisType;

Uint8 dsfisBytel;

Uint32 dsfisDw1DmaBuffLow;

Uint32 dsfisDw2DmaBuffHigh;

Uint32 dsfisDw4DmaBuffOffset;

Uint32 dsfisDw5DmaXferCnt;

}dsFis;

typedef struct {

Uint8 psfisType;

Uint8 psfisBytel;

Uint8 psfisStatus;

Uint8 psfisError;

Uint8 psfisDwlSecNumLbaLow;

Uint8 psfisDw1Cy1LowLbaMid;

Uint8 psfisDwlCylHighLbahigh;

Uint8 psfisDw1Dev;

Uint8 psfisDw3SecCnt;

Uint8 psfisDw3Estatus;

Uint16 psfisDw4XferCnt;

}piosFis;

typedef struct {

Uint8 regfisType;

Uint8 regfisBytel;

```

```

TEXAS

INSTRUMENTS

```

```

Uint8 regfisStatus;

Uint8 regfisError;

Uint8 regfisDwlSecNumLbaLow;

Uint8 regfisDw1Cy1LowLbaMid;

Uint8 regfisDwlCylHighLbahigh;

Uint8 regfisDw1Dev;

Uint8 regfisDw3SecCnt;

}regFis;

typedef struct {

Uint8 sdbfisType;

Uint8 sdbfisBytel;

Uint8 sdbfisStatus;

Wint8 sdbfisError;

}sdbFis;

typedef struct {

Uint32 ufisWord[16];

luFis;

typedef struct {

Uint32 capSMPS:1;

Uint32 capSSS:1;

Uint32 piPi:2;

Uint32 p0cmdCpd:1;

Uint32 p0cmdEsp:1;

Uint32 p0cmdMpsp:1;

Uint32 p0cmdHpcp:1;

Uint32 rsv:24;

}FirmwareCtrlFeatures;

void initMemory(Uint32 *startAddress, Uint32 length, Uint32 seedWord, Uint32 modifyVal) {

Uint32 I;

*startAddress++ = seedWord;

for (I=0; i<length-1; I++) {</pre>

seedWord += modifyVal;

*startAddress++ = seedWord;

}

}

void clearCmdList(void) {

//clear Host to Device (Command FIS) Space

initMemory((Uint32*)CmdLists, (LISTLENGTH*(sizeof(CmdListHeader)/4)), 0, 0);

}

void clearCmdTables(void) {

Uint16 cmdSlot;

for (cmdSlot=0; cmdSlot<LISTLENGTH; cmdSlot++) {</pre>

//Clear Command FIS and ATAPI Command Spaces for Command Header X; LISTLENGTH < X < 0

initMemory((Uint32 *)&CmdTable[cmdSlot], (sizeof(CommandFIS)/4)+(sizeof(Atapi)/4), 0, 0);

//Clear PRD Descriptor Locations for Command Header X; LISTLENGTH < X < 0

initMemory((Uint32*)((Uint32)&CmdTable[cmdSlot]+0x80),

(sata_input_filePageSize*(sizeof(PRDT)/4)*sata_input_prdLength), 0, 0);

}

}

void clearRcvFis() {

//clear Receive DMA Setup FIS Space.

initMemory((Uint32*)&RcvFis, (sizeof(DMASetupFis)/4), 0, 0);

//clear Receive PIO Setup FIS Space.

initMemory((Uint32*)((Uint32)&RcvFis+0x20), (sizeof(PIOSetupFis)/4), 0, 0);

//clear Receive Device to Host (D2H) Register FIS Space.

initMemory((Uint32*)((Uint32)&RcvFis+0x40), (sizeof(D2HRegFis)/4), 0, 0);

//clear Set Device Bits FIS Space.

initMemory((Uint32*)((Uint32)&RcvFis+0x58), (sizeof(SetDevBitsFis)/4), 0, 0);

//clear Unknow FIS Space.

initMemory((Uint32*)((Uint32)&RcvFis+0x60), (sizeof(UnknownFis)/4), 0, 0);

}

```

void clearDmaBuffers(void) {

//Clear PRD Data Buffer Memory

```

TEXAS

INSTRUMENTS

```

```

Use Cases

```

```

initMemory((Uint32 *)prdTableDataBuff, (LISTLENGTH*PRDLENGTH*DATABUFFERLEN/4), 0, 0);

}

void performFirmwareInit(void) {

/* Firmware Initialization*/

11

Make sure you perform a Single Write in one operation of all HwInit Fields

initialization defined within a single register

11

sataRegs->CAP |= ((swCtrlFeatures.capSMPS << 28) |</pre>

(swCtrlFeatures.capSSS << 27)

);

// Configure PI[31:0]

sataRegs->PI |= (swCtrlFeatures.piPi << 0);</pre>

// Configure POCMD[ESP,CPD,MPSP,HPCP=21,20,19,18]

sataRegs->P0CMD |= ((swCtrlFeatures.p0cmdEsp << 21)</pre>

(swCtrlFeatures.p0cmdCpd << 20)

(swCtrlFeatures.p0cmdMpsp << 19)

(swCtrlFeatures.p0cmdHpcp << 18)

);

/* Software Initialization*/

// Initialize PHY and DMA Parameters (Corresponding to Gen1/2i timing)

sataRegs->P0PHYCR = 0x80182048;

initBaseAddresses(); // Initialize Command List (POCLB) and Receive FIS (POFS)

// Configure Line Speed.

setSataSpeed(DESIRED_SPEED); //GOASFASTASDEVICE=0,GEN1=1,GEN2=2

// Enable Receive DMA

enableRcvFis();

// The below are general Semaphores/Flags used and want to make sure they are initialized.

// 28 Bit LBA Address of Device. 0xFFFFFFFF is used by test S/W to indicate that it is not

initialized

Dev28bitLbaAddress = 0xFFFFFFF; // S/W needs to initialize this variable prior to calling

//_INT_DRIVEN_TEST_ is defined within the Project File

#ifdef _INT_DRIVEN_TEST_

intHandlingMethod = USE_INT_HANDLER;

#else

intHandlingMethod = USE_POLLING;

#endif

}

char spinUpDeviceAndWaitForInitToComplete(void) {

// Make sure that the HBA is in a Listen Mode prior to Spinning Up Device

// Following Configuration is not allowed.

[POSCTL.DET, POCMD.SUD] = [1,1] NOT Allowed.

11

if((sataRegs->POSCTL & AHCI_PxSCTL_PxSSTS_DET) != 0)

sataRegs->POSCTL &= ~(Oxf << AHCI_PxSCTL_PxSSTS_DET_SHIFT);</pre>

// Clear POSERR.DIAG.X (RWC bit field) so that the POTFD is updated by HBA.

sataRegs->POSERR |= 0x04000000;

// Spin Up Device.

sataRegs->P0CMD |= (1 << AHCI_PxCMD_SUD_SHIFT);</pre>

// Wait for Device Detection or/and Speed Negotiation to take place and finish.

while ((sataRegs->POSSTS & AHCI_PxSCTL_PxSSTS_DET) !=0x3);

// Device would send its status and and default Task file regs content (signature)

// when finished with Power Up: Look for Device ready status.

while ((sataRegs->POTFD & AHCI_PxTFD_STS_BSY_DRQ_ERR) != 0);

// Make sure that the expected Device signature is received.

if (sataRegs->P0SIG != AHCI_P0SIG_SIG_ATA_DEV_GOOD_STAT) // LBAhigh:LBAmid:LBAlow:SECcnt

return(1);

// = 0 \times 0.0000101

return(0);

```

#### TEXAS INSTRUMENTS

```

}

void initIntAndClearFlags(void) {

// Make sure Interrupt is disabled (Disable at Port Level followed by Global Level).

// Clear Interrupt at Port Level

enableDisableInt(PORTint, DISABLE, 0xFFFFFFF); // clearInt(int type, intState, specificField)

// int type=GLOBALint or PORTint

// intState=DISABLE or ENABLE

// specificField=bit field to Enable or Disable

// is used for the RWC feature for PORTint

// Disable interrrupt at Global Level

enableDisableInt(GLOBALint, DISABLE, 0);

// clearInt(intType, intState fields2clr)

// int type=GLOBALint or PORTint

// intState=DISABLE or ENABLE

// fields2clr=dontcare for GLOBALint

// is used for the RWC feature for PORTint

// Need to clear interrupts at Port Level followed by Global Level.

// Ensure all pending Port Error and Status are cleared.

clearIntOrErrorDiag(ERRORFIELDS, sataRegs->POSERR); // Clear POSERR Register

// Ensure all pending Port Interrupts and The Single Global Interrupt are cleared.

clearIntOrErrorDiag(INTFIELDS, sataRegs->POIS); // Clear POIS and IS Regs

}

void invokeHBAReset() {

// HBA Reset will not affect the following Registers settings of PxFB and PxCLB

// regs and HwInit fields of Port Registers are not affected.

// To Do: Check if the Global Registers are affected. Spec mentions not affected.

// Note: COMRESET OOB will not be sent to attached Device because Freon supports

// Staggered Spinup capability and POCMD.SUD is cleared to Zero when HBA Reset

\ensuremath{{\prime}}\xspace // takes place. Software needs to invoke this if needed.

// Most likely user want to ensure HBA comes up in its default operation state

// or has hung and is unable to idle the port when needing to perform an HBA

// reset. Regardless, there is no need to attempt to idle the HBA from

// running

sataRegs->GHC |= (1 << AHCI_GHC_HR_SHIFT);</pre>

// Max Spec time is 1 Second for Reset to complete.

while((sataRegs->GHC & AHCI_GHC_HR) != 0) {

waitForXms(WAIT_500_MILLISECONDS);

waitForXms(WAIT_500_MILLISECONDS);

}

}

char placeHbaInIdle(void) {

// To Place HBA In IDLE, need to make sure both DMAs (Cmd List and Rcv FIS) are not running.

// Order of Disabling the DMA is important.

// Ensure that the Cmd List DMA is not running

// If is running, clear ST and wait for 500ms. Then Check CR.

if (sataRegs->P0CMD & AHCI_PxCMD_ST) {

sataRegs->P0CMD &= ~(1 << AHCI_PxCMD_ST_SHIFT);</pre>

waitForXms(WAIT_500_MILLISECONDS);

}// Wait another 500 Milliseconds for CR to clear. This is twice more than required.

if (sataRegs->P0CMD & AHCI_PxCMD_CR)

waitForXms(WAIT_500_MILLISECONDS);

// If POCMD.CR is still set, HBA probably has hunged. No need to continue.

// Need to perform HBA Reset.

if (sataRegs->P0CMD & AHCI_PxCMD_CR)

return(1);

// Ensure that the Receive FIS DMA is running.

// If is running, clear FRE and wait for 500ms. Then Check FR.

if (sataRegs->P0CMD & AHCI_PxCMD_FRE) {

sataRegs->P0CMD &= ~(1 << AHCI_PxCMD_FRE_SHIFT);</pre>

waitForXms(WAIT_500_MILLISECONDS);

}// Wait unti FR is Cleared.

while (sataRegs->POCMD & AHCI_PxCMD_FR)

waitForXms(WAIT_500_MILLISECONDS);

```

```

TEXAS

INSTRUMENTS

```

Use Cases

```

www.ti.com

```

```

// If POCMD.FRE is still set, HBA probably has hunged. No need to continue.

// Need to perform HBA Reset.

if (sataRegs->P0CMD & AHCI_PxCMD_FRE)

return(1);

return(0);

}

void associateSysMem2Hba(Uint16 cmdSlot) {

associtateCmdSlotWithCmdTable(cmdSlot);

// Assign Sys Mem allocated for Cmd Table to Cmd

List Slot

//associtatePrdsWithCmdTable(cmdSlot);

// Assign PRD info to Cmd Table

associtatePrdsWithCmdTable(cmdSlot, sata_input_filePageSize);

}

void associtateCmdSlotWithCmdTable(Uint16 cmdSlot) {

CmdLists[cmdSlot].DW2.CmdTableAddLow=((unsigned int)&CmdTable[cmdSlot] & 0xFFFFF80);

CmdLists[cmdSlot].DW3.CmdTableAddHigh=0x0;

}

void associtatePrdsWithCmdTable(Uint16 cmdSlot, Uint16 fSize) {

Uint16 fileSIZE, prdLength;

for (fileSIZE=0; fileSIZE<fSize; fileSIZE++) {</pre>

for (prdLength=0; prdLength<sata_input_prdLength; prdLength++) {</pre>

// Command Header 0 PRD Descriptors 0 & 1 are Initialized.

CmdTable[cmdSlot].prdTable[(sata_input_prdLength*fileSIZE)+prdLength].DW0.DbaLow=(unsigned

int)&prdTableDataBuff[cmdSlot][prdLength];

CmdTable[cmdSlot].prdTable[(sata_input_prdLength*fileSIZE)+prdLength].DW1.DbaHigh=0x0;

CmdTable[cmdSlot].prdTable[(sata_input_prdLength*fileSIZE)+prdLength].DW3.DataBC=sata_input_prd_da

taBuffLen-1;

}

}

}

void setSataSpeed(unsigned char iSpeed) {

sataRegs->P0SCTL |= (iSpeed << AHCI_PxSCTL_PxSSTS_SPD_SHIFT);</pre>

waitForXms(5); // This might not be necessary: wait a bit

}

char setupCfisEntriesForDataRdWr(CmdListHeader *CmdListNum, dataXferDir readOrWrite, xferProtocol

xferType) {

//$$$$$$$$$$$$$$$$$$$$$$$$$$$$ **** Initializing the Command Header *******

// Other part of the Command List Structure, with the exception of Word 0 for the

// Command Slots[0] and [1] are already initialized when invoking sata_init_and_spin_up()

// function via associateMem2HBA() function.

// Configure Word 0 of Command List

// This is the length of H2D FIS. This might need changing

CmdListNum->DW0.CmdLen=5;

based on the Command issued to Device. Need to Check.

11

CmdListNum->DW0.Atapi=0;

// Command is destined to HDD Like Device.

CmdListNum->DW0.Prefetch=1; // Doesn't hurt prefetching so do it.

// WARNING: Do Not Prefetch if using:

11

=> Command Oueuing

11

=> Port Multiplier

CmdListNum->DW0.Reset=0;

// This is normally set to Zero unless a Soft Reset is required.

CmdListNum->DW0.Bist=0;

// This is for entering test mode and should be cleared for

normal operation.

\ensuremath{{//}} For Normal operation require to Clear this bit so POTFD and

CmdListNum->DW0.Rok=0;

POCI are modified by HBA as appropriate.

// Rok should be set for S/W Reset Command.

\ensuremath{{\prime}}\xspace // Used only if an external Port Multiplier is attached and

CmdListNum->DW0.Pmp=0x0;

selects the Port of the Port Multiplier.

//$$$$$$$$$$$$$$$$$$$$$$$

// The above DWO fields usually would not change for Normal operation.

if (readOrWrite == DATA_DIR_WR) // The Write setting here is based on the Data FIS direction.

CmdListNum->DW0.Write=1; // Write=1/0=>Write/Read;

else if (readOrWrite == DATA_DIR_RD) // The Write setting here is based on the Data FIS

direction.

```

ÈXAS

RUMENTS

```

Use Cases

```

```

CmdListNum->DW0.Write=0; // Write=1/0=>Write/Read;

else return(1);

CmdListNum->DW0.Prdtl=sata_input_prdLength;

// Need to update this when using DMA for

11

Data transfer.

CmdListNum->DW0.Prdtl=sata_input_filePageSize*sata_input_prdLength;

// Need to update this

when using DMA for Data transfer.

//$$$$$$$$$$$$$$$$$$$$$$$$$$$ **** Initializing the Command FIS (H2D FIS) *****

// Cmd FIS is made of a 20 Bytes size FIS.