## TMS320C674x/OMAP-L1x Processor 64-Bit Timer Plus

# **User's Guide**

Literature Number: SPRUFM5A June 2009

## Contents

| Prefac | e      |                                                          | . 6       |

|--------|--------|----------------------------------------------------------|-----------|

| 1      | Introd | uction                                                   | . 8       |

|        | 1.1    | Purpose of the Peripheral                                | . 8       |

|        | 1.2    | Features                                                 | . 8       |

|        | 1.3    | Block Diagram                                            | . 9       |

|        | 1.4    | Industry Standard Compatibility Statement                | . 9       |

| 2      | Archit | ecture                                                   | 10        |

|        | 2.1    | Architecture – General-Purpose Timer Mode                | 10        |

|        | 2.2    | Architecture – Watchdog Timer Mode                       | 21        |

|        | 2.3    | Reset Considerations                                     | 23        |

|        | 2.4    | Interrupt Support                                        | 23        |

|        | 2.5    | DMA Event Support                                        | 23        |

|        | 2.6    | TM64P_OUT Event Support                                  | 24        |

|        | 2.7    | External Timer Pin GPIO Mode                             | 25        |

|        | 2.8    | Interrupt/DMA Event Generation Control and Status        | 25        |

|        | 2.9    | Power Management                                         | 25        |

|        | 2.10   | Emulation Considerations                                 | 25        |

| 3      | Regist | ers                                                      | <b>26</b> |

|        | 3.1    | Revision ID Register (REVID)                             | 27        |

|        | 3.2    | Emulation Management Register (EMUMGT)                   | 27        |

|        | 3.3    | GPIO Interrupt Control and Enable Register (GPINTGPEN)   | 28        |

|        | 3.4    | GPIO Data and Direction Register (GPDATGPDIR)            | 30        |

|        | 3.5    | Timer Counter Registers (TIM12 and TIM34)                | 32        |

|        | 3.6    | Timer Period Registers (PRD12 and PRD34)                 | 33        |

|        | 3.7    | Timer Control Register (TCR)                             | 34        |

|        | 3.8    | Timer Global Control Register (TGCR)                     | 37        |

|        | 3.9    | Watchdog Timer Control Register (WDTCR)                  | 38        |

|        | 3.10   | Timer Reload Register 12 (REL12)                         | 39        |

|        | 3.11   | Timer Reload Register 34 (REL34)                         | 39        |

|        | 3.12   | Timer Capture Register 12 (CAP12)                        |           |

|        | 3.13   | Timer Capture Register 34 (CAP34)                        |           |

|        | 3.14   | Timer Interrupt Control and Status Register (INTCTLSTAT) |           |

|        | 3.15   | Timer Compare Registers (CMP0-CMP7)                      | 42        |

| Appen  | dix A  | Revision History                                         | <b>43</b> |

## List of Figures

| 1  | Timer Block Diagram                                      | . 9 |

|----|----------------------------------------------------------|-----|

| 2  | Timer Clock Source Block Diagram                         | 10  |

| 3  | 64-Bit Timer Mode Block Diagram                          | 12  |

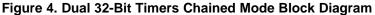

| 4  | Dual 32-Bit Timers Chained Mode Block Diagram            | 14  |

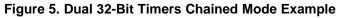

| 5  | Dual 32-Bit Timers Chained Mode Example                  | 14  |

| 6  | Dual 32-Bit Timers Unchained Mode Block Diagram          | 16  |

| 7  | Dual 32-Bit Timers Unchained Mode Example                | 17  |

| 8  | 32-Bit Timer Counter Overflow Example                    | 20  |

| 9  | Watchdog Timer Mode Block Diagram                        | 22  |

| 10 | Watchdog Timer Operation State Diagram                   | 22  |

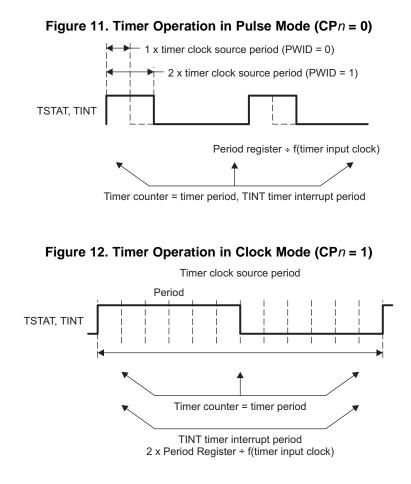

| 11 | Timer Operation in Pulse Mode (CPn = 0)                  | 24  |

| 12 | Timer Operation in Clock Mode (CPn = 1)                  | 24  |

| 13 | Revision ID Register (REVID)                             | 27  |

| 14 | Emulation Management Register (EMUMGT)                   | 27  |

| 15 | GPIO Interrupt Control and Enable Register (GPINTGPEN)   | 28  |

| 16 | GPIO Data and Direction Register (GPDATGPDIR)            | 30  |

| 17 | Timer Counter Register 12 (TIM12)                        | 32  |

| 18 | Timer Counter Register 34 (TIM34)                        | 32  |

| 19 | Timer Period Register 12 (PRD12)                         | 33  |

| 20 | Timer Period Register 34 (PRD34)                         | 33  |

| 21 | Timer Control Register (TCR)                             | 34  |

| 22 | Timer Global Control Register (TGCR)                     | 37  |

| 23 | Watchdog Timer Control Register (WDTCR)                  | 38  |

| 24 | Timer Reload Register 12 (REL12)                         | 39  |

| 25 | Timer Reload Register 34 (REL34)                         | 39  |

| 26 | Timer Capture Register 12 (CAP12)                        | 40  |

| 27 | Timer Capture Register 34 (CAP34)                        | 40  |

| 28 | Timer Interrupt Control and Status Register (INTCTLSTAT) | 41  |

| 29 | Timer Compare Register (CMPn)                            | 42  |

## List of Tables

| 1   | Timer Clock Source Selection                                                | 10 |

|-----|-----------------------------------------------------------------------------|----|

| 2   | 64-Bit Timer Configurations                                                 | 13 |

| 3   | 32-Bit Timer Chained Mode Configurations                                    | 15 |

| 4   | 32-Bit Timer Unchained Mode Configurations                                  | 18 |

| 5   | Counter and Period Registers Used in GP Timer Modes                         | 20 |

| 6   | TSTAT Parameters in Pulse and Clock Modes                                   | 24 |

| 7   | Timer Emulation Modes Selection                                             | 26 |

| 8   | Timer Registers                                                             | 26 |

| 9   | Revision ID Register (REVID) Field Descriptions                             | 27 |

| 10  | Emulation Management Register (EMUMGT) Field Descriptions                   | 27 |

| 11  | GPIO Interrupt Control and Enable Register (GPINTGPEN) Field Descriptions   | 28 |

| 12  | GPIO Data and Direction Register (GPDATGPDIR) Field Descriptions            | 30 |

| 13  | Timer Counter Register 12 (TIM12) Field Descriptions                        | 32 |

| 14  | Timer Counter Register 34 (TIM34) Field Descriptions                        | 32 |

| 15  | Timer Period Register (PRD12) Field Descriptions                            | 33 |

| 16  | Timer Period Register (PRD34) Field Descriptions                            | 33 |

| 17  | Timer Control Register (TCR) Field Descriptions                             | 34 |

| 18  | Timer Global Control Register (TGCR) Field Descriptions                     | 37 |

| 19  | Watchdog Timer Control Register (WDTCR) Field Descriptions                  | 38 |

| 20  | Timer Reload Register 12 (REL12) Field Descriptions                         | 39 |

| 21  | Timer Reload Register 34 (REL34) Field Descriptions                         | 39 |

| 22  | Timer Capture Register 12 (CAP12) Field Descriptions                        | 40 |

| 23  | Timer Capture Register 34 (CAP34) Field Descriptions                        | 40 |

| 24  | Timer Interrupt Control and Status Register (INTCTLSTAT) Field Descriptions | 41 |

| 25  | Timer Compare Register (CMPn) Field Descriptions                            | 42 |

| A-1 | Document Revision History                                                   | 43 |

Preface SPRUFM5A–June 2009

## About This Manual

This document describes the operation of the software-programmable 64-bit Timer Plus.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320C674x Digital Signal Processors (DSPs) and OMAP-L1x Applications Processors. Copies of these documents are available on the Internet at <u>www.ti.com</u>. *Tip:* Enter the literature number in the search box provided at www.ti.com.

The current documentation that describes the DSP, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <a href="http://www.ti.com/c6000">www.ti.com/c6000</a>.

<u>SPRUGM5</u> — TMS320C6742 DSP System Reference Guide. Describes the C6742 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

- <u>SPRUGJ0</u> *TMS320C6743 DSP System Reference Guide.* Describes the System-on-Chip (SoC) including the C6743 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

- <u>SPRUFK4</u> TMS320C6745/C6747 DSP System Reference Guide. Describes the System-on-Chip (SoC) including the C6745/C6747 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

- SPRUGM6 TMS320C6746 DSP System Reference Guide. Describes the C6746 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

- SPRUGJ7 TMS320C6748 DSP System Reference Guide. Describes the C6748 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

- <u>SPRUG84</u> OMAP-L137 Applications Processor System Reference Guide. Describes the System-on-Chip (SoC) including the ARM subsystem, DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, ARM interrupt controller (AINTC), and system configuration module.

- SPRUGM7 OMAP-L138 Applications Processor System Reference Guide. Describes the System-on-Chip (SoC) including the ARM subsystem, DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, ARM interrupt controller (AINTC), and system configuration module.

- SPRUFK9 TMS320C674x/OMAP-L1x Processor Peripherals Overview Reference Guide. Provides an overview and briefly describes the peripherals available on the TMS320C674x Digital Signal Processors (DSPs) and OMAP-L1x Applications Processors.

- SPRUFK5 TMS320C674x DSP Megamodule Reference Guide. Describes the TMS320C674x digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

- SPRUFE8 TMS320C674x DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C674x digital signal processors (DSPs). The C674x DSP is an enhancement of the C64x+ and C67x+ DSPs with added functionality and an expanded instruction set.

- SPRUG82 TMS320C674x DSP Cache User's Guide. Explains the fundamentals of memory caches and describes how the two-level cache-based internal memory architecture in the TMS320C674x digital signal processor (DSP) can be efficiently used in DSP applications. Shows how to maintain coherence with external memory, how to use DMA to reduce memory latencies, and how to optimize your code to improve cache efficiency. The internal memory architecture in the C674x DSP is organized in a two-level hierarchy consisting of a dedicated program cache (L1P) and a dedicated data cache (L1D) on the first level. Accesses by the CPU to the these first level caches can complete without CPU pipeline stalls. If the data requested by the CPU is not contained in cache, it is fetched from the next lower memory level, L2 or external memory.

## 64-Bit Timer Plus

#### 1 Introduction

This document describes the operation of the software-programmable 64-bit Timer Plus. The number of supported Timer modules will vary between devices. The 64-bit Timer Plus can be programmed in 64-bit mode, dual 32-bit unchained mode, or dual 32-bit chained mode. Some Timer Plus implementations have signal connections to internal device reset that can be used in watchdog timer mode. New features over previous timers include: external clock/event input, period reload, external event capture, and timer counter register read reset.

#### 1.1 Purpose of the Peripheral

The timer can support four basic modes of operation: a 64-bit general-purpose (GP) timer, dual unchained 32-bit GP timers, dual chained 32-bit timers, or a watchdog timer. The GP timer modes can be used to generate periodic interrupts and DMA synchronization events. The watchdog timer mode is used to provide a recovery mechanism for the device in the event of a fault condition (such as a non-exiting code loop).

#### 1.2 Features

The 64-bit timer consists of the following features -- some features may not be supported on all timer instantiations (see your device-specific data manual for supported features):

- 64-bit count-up counter

- Timer modes:

- 64-bit general-purpose timer mode

- Dual 32-bit unchained general-purpose timer mode

- Dual 32-bit chained timer mode

- Watchdog timer mode

- 2 possible clock sources:

- Internal clock

- External clock/event input via timer input pins

- 3 possible operation modes:

- One-time operation (timer runs for one period then stops)

- Continuous operation (timer automatically resets to zero after each period and continues to operate)

- Continuous operation with period reload (timer automatically assumes the value of the reload registers after each period and continues to operate)

- Generates interrupts to CPU

- Generates sync events to DMA

- Generates output event to device reset (watchdog only)

- Generates output event to timer output pins (if pins are available)

- External event capture via timer input pins (if pins are available)

## 1.3 Block Diagram

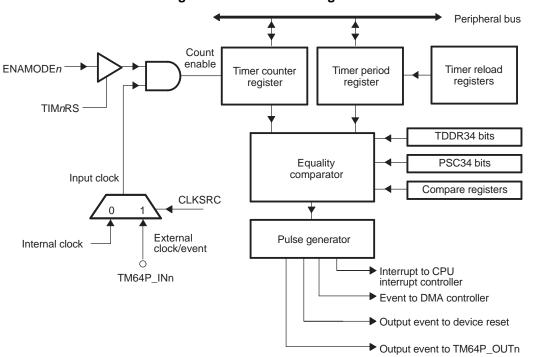

A block diagram of the timer is shown in Figure 1. Detailed information about the architecture and operation of the timers is in Section 2.1 and Section 2.2.

Figure 1. Timer Block Diagram

## 1.4 Industry Standard Compatibility Statement

This peripheral is not intended to conform to any specific industry standard.

TEXAS INSTRUMENTS

www.ti.com

Architecture

#### 2 Architecture

#### 2.1 Architecture – General-Purpose Timer Mode

This section describes the timer in the general-purpose (GP) timer mode.

#### 2.1.1 Backward Compatible Mode

The Timer Plus supports the following additional features over the other timers:

- External clock/event input

- Period reload

- External event capture mode

- Timer counter register read reset mode

- Timer counter capture registers

- Register for interrupt/DMA generation control and status

By default, period reload, external event capture mode, timer counter register read reset mode, timer counter capture registers, and interrupt/DMA/TM64P\_OUT generation control and status are not available. To enable these features, you must set the PLUSEN bit in the timer global control register (TGCR). These features are described throughout the following sections. External clock/event input is always available, regardless of the state of the backward compatible bit.

#### 2.1.2 Clock Control

The timer can use an internal or external clock source for the counter period. The following sections explain how to select the clock source.

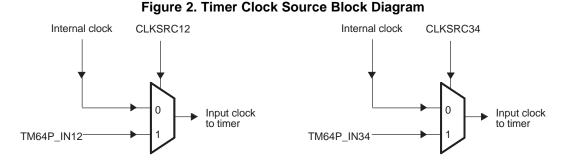

As shown in Table 1 and Figure 2, the timer clock source is selected using the clock source (CLKSRC12) and (CLKSRC34) bits in the timer control register (TCR). Two clock sources are available to drive the timer clock:

- internal clock, by setting CLKSRC12 and/or CLKSRC34 = 0.

- external clock on input pin TM64P\_IN12 and/or TM64P\_IN34, by setting CLKSRC12 and/or CLKSRC34 = 1.

At reset, the clock source is the internal clock. Details on each of the clock source configuration options are included in the following sections.

| CLKSRC(12/34) | Input Clock                   |

|---------------|-------------------------------|

| 0             | Internal clock (default)      |

| 1             | External clock on timer input |

Table 1. Timer Clock Source Selection

10 64-Bit Timer Plus

#### 2.1.2.1 Using the Internal Clock Source to the Timer

The internal clock source to the timer is driven by the auxiliary clock of the PLL controller. The frequency of the auxiliary clock is equal to the input reference clock of the PLL controller, and therefore is not affected by the multiplier and divider values of the PLL controller. This clock source determines the speed of the timer since the timer counts up in units of source clock cycles. When determining the period and prescaler settings for the timer, choose the desired period in units of source clock cycles. For details on the generation of the on-chip clocks, see your device-specific *System Reference Guide*.

The CLKSRC12 and CLKSRC34 parameters in the timer control register (TCR) control whether the internal or external clock is used as the clock source for the timer. If the timer is configured in 64-bit mode or 32-bit chained mode, CLKSRC12 controls the clock source for the entire timer. If the timer is configured in dual 32-bit unchained mode (TIMMODE = 01 in TGCR), CLKSRC12 controls the timer 1:2 side of the timer while CLKSRC34 controls the timer 3:4 side of the timer.

To select the internal clock as the clock source for the timer, CLKSRC12 and/or CLKSRC34 in TCR must be cleared to 0. If the timer being used does not have pins available to source external clocks, CLKSRC12 and/or CLKSRC34 must always be 0.

#### 2.1.2.2 Using the External Clock Source to the Timer

An external clock source can be provided to clock the timer through the timer input pins TM64P\_IN12 and TM64P\_IN34. The CLKSRC12 and CLKSRC34 parameters in the timer control register (TCR) control whether the internal or external clock is used as the clock source for the timer. If the timer is configured in 64-bit mode or 32-bit chained mode, CLKSRC12 controls the clock source for the entire timer. If the timer is configured in dual 32-bit unchained mode (TIMMODE = 01 in TGCR), CLKSRC12 controls the timer 1:2 side of the timer while CLKSRC34 controls the timer 3:4 side of the timer.

The external clock source for the timer 1:2 side of the timer comes from TM64P\_IN12; the external clock source for the timer 3:4 side of the timer comes from TM64P\_IN34.

At reset, the clock source defaults to the internal clock. Details on each of the clock source configuration options are included in the following sections. To select the external clock as the clock source for the timer, CLKSRC12 and/or CLKSRC34 in TCR must be set to 1. The external clock source frequency must be no greater than the timer peripheral reference clock (see your device-specific data manual).

#### 2.1.3 Signal Descriptions

As shown in Figure 2, pins TM64P\_IN12 and TM64P\_IN34 may be used as input to the timer. These signals can be used to drive the clock/event count or be used as an external event input for event capture mode.

#### 2.1.4 Timer Modes

Texas Instruments

www.ti.com

The following section describes the general-purpose (GP) timer modes.

#### 2.1.4.1 64-Bit Timer Mode

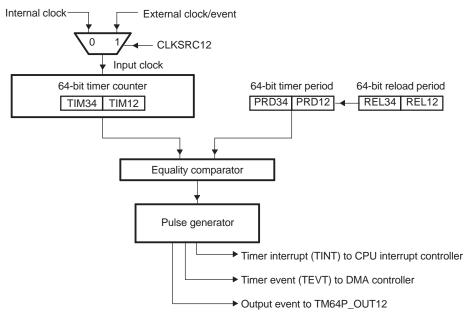

The timer can be configured as a 64-bit timer by clearing the TIMMODE bit in the timer global control register (TGCR) to 0. At reset, 0 is the default setting for the TIMMODE bit.

In this mode, the timer operates as a single 64-bit up-counter (Figure 3). The counter registers (TIM12 and TIM34) form a 64-bit timer counter register and the period registers (PRD12 and PRD34) form a 64-bit timer period register. When the timer is enabled, the timer counter starts incrementing by 1 at every timer input clock cycle. When the timer counter matches the timer period, a maskable timer interrupt (TINT*n*) and a timer EDMA (TEVT*n*) are generated. When the timer is configured in continuous mode, the timer counter is reset to 0 on the cycle after the timer counter reaches the timer period. The timer can be stopped, restarted, reset, or disabled using control bits in TGCR.

Figure 3. 64-Bit Timer Mode Block Diagram

#### 2.1.4.1.1 Enabling the 64-Bit Timer

The TIM12RS and TIM34RS bits in TGCR control whether the timer is in reset or capable of operating. For the timer to operate in 64-bit timer mode, the TIM12RS and TIM34RS bits must be set to 1.

The ENAMODE12 bit in the timer control register (TCR) controls whether the timer is disabled, enabled to run once, enabled to run continuously, or enabled to run continuously with period reload; the ENAMODE34 bit has no effect in 64-bit timer mode. When the timer is disabled (ENAMODE12 = 0), the timer does not run and maintains its current count value. When the timer is enabled for one time operation (ENAMODE12 = 1), it counts up until the counter value equals the period value and then stops. When the timer is enabled for continuous operation (ENAMODE12 = 2h), the counter counts up until it reaches the period value, then resets itself to zero and begins counting again. When the timer is enabled for continuous operation (ENAMODE12 = 3h), the counter counts up until it reaches the period value, then resets itself to zero, reloads the period registers (PRD12 and PRD34) with the value in the period reload registers (REL12 and REL34), and begins counting again.

Table 2 shows the bit values in TGCR to configure the 64-bit timer.

|                                                                        | TGCR Bit |         | TCR Bit   |  |

|------------------------------------------------------------------------|----------|---------|-----------|--|

| 64-Bit Timer Configuration                                             | TIM12RS  | TIM34RS | ENAMODE12 |  |

| To place the 64-bit timer in reset                                     | 0        | 0       | 0         |  |

| To disable the 64-bit timer (out of reset)                             | 1h       | 1h      | 0         |  |

| To enable the 64-bit timer for one-time operation                      | 1h       | 1h      | 1h        |  |

| To enable the 64-bit timer for continuous operation                    | 1h       | 1h      | 2h        |  |

| To enable the 64-bit timer for continuous operation with period reload | 1h       | 1h      | 3h        |  |

#### Table 2. 64-Bit Timer Configurations

Once the timer stops, if an external clock is used as the timer clock, the timer must remain disabled for at least one external clock period or the timer will not start counting again. When using the external clock, the count value is synchronized to the internal clock.

Note that when both the timer counter and timer period are cleared to 0, the timer can be enabled but the timer counter does not increment because the timer period is 0.

#### 2.1.4.1.2 Reading the Counter Registers

When reading the timer count in 64-bit timer mode, the CPU must first read TIM12 followed by TIM34. When TIM12 is read, the timer copies TIM34 into a shadow register. When reading TIM34, the hardware logic forces the reads to read from the shadow register. This ensures that the values read from the registers are not affected by the fact that the timer may continue to run as the registers are read. When reading the timers in 32-bit mode, TIM12 and TIM34 may be read in either order.

#### 2.1.4.1.3 64-Bit Timer Configuration Procedure

To configure the GP timer to operate as a 64-bit timer, follow the steps below:

- 1. Select 64-bit mode (TIMMODE in TGCR).

- 2. Remove the timer from reset (TIM12RS and TIM34RS in TGCR).

- 3. Select the desired timer period (PRD12 and PRD34).

- 4. Enable the timer (ENAMODE12 in TCR).

- 5. If ENAMODE12 = 3h, write the desired timer period for the next timer cycle in the period reload registers (REL12 and REL34). This step can be done at any time before the current timer cycle ends.

#### 2.1.4.2 Dual 32-Bit Timer Modes

Each of the general-purpose timers can be configured as dual 32-bit timers by configuring the TIMMODE bit in the timer global control register (TGCR). In dual 32-bit timer mode, the two 32-bit timers can be operated independently (unchained mode) or in conjunction with each other (chained mode).

#### 2.1.4.2.1 Chained Mode

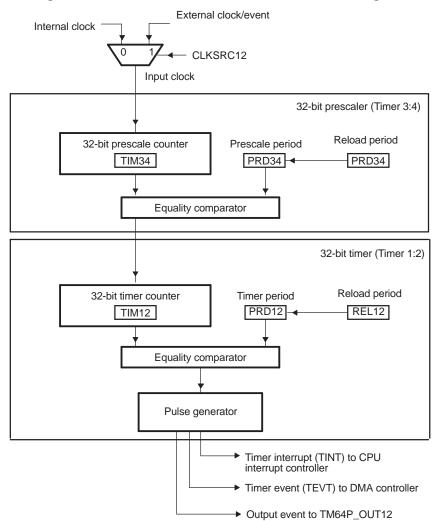

The general-purpose timers can each be configured as a dual 32-bit chained timer by setting the TIMMODE bit to 3h in TGCR.

In the chained mode (Figure 4), one 32-bit timer (timer 3:4) is used as a 32-bit prescaler and the other 32-bit timer (timer 1:2) is used as a 32-bit timer. The 32-bit prescaler is used to clock the 32-bit timer. The 32-bit prescaler uses one counter register (TIM34) to form a 32-bit prescale counter register and one period register (PRD34) to form a 32-bit prescale period register.

When the timer is enabled, the prescale counter starts incrementing by 1 at every timer input clock cycle. One cycle after the prescale counter matches the prescale period, a clock signal is generated and the prescale counter register is reset to 0 (see the example in Figure 5).

The other 32-bit timer (timer 1:2) uses one counter register (TIM12) to form a 32-bit timer counter register and one period register (PRD12) to form a 32-bit timer period register. This timer is clocked by the output clock from the prescaler. The timer counter increments by 1 at every prescaler output clock cycle. When the timer counter matches the timer period, a maskable timer interrupt (TINT12) and a timer EDMA event (TEVT12) are generated. When the timer is configured in continuous mode, the timer counter is reset to 0 on the cycle after the timer counter reaches the timer period. The timer can be stopped, restarted, reset, or disabled using the TIM12RS and TIM34RS bits in TGCR. In the chained mode, the upper 16-bits of the timer control register (TCR) are not used.

32-bit prescaler settings: count = TIM34 = 200; period = PRD34 = 202 32-bit timer settings: count = TIM12 = 3; period = PRD12= 4

#### 2.1.4.2.1.1 Enabling the 32-Bit Timer Chained Mode

The TIM12RS and TIM34RS bits in TGCR control whether the timer is in reset or capable of operating. The TIM12RS bit controls the reset of the timer 1:2 side of the timer and the TIM34RS bits control the reset of the timer 3:4 side of the timer. For the timer to operate, the TIM12RS and TIM34RS bits must be set to 1.

The ENAMODE12 bit in the timer control register (TCR) controls whether the timer is disabled, enabled to run once, enabled to run continuously, enabled to run continuously with period reload; the ENAMODE34 bit has no effect in 32-bit timer chained mode. When the timer is disabled (ENAMODE12 = 0), the timer does not run and maintains its current count value. When the timer is enabled for one time operation (ENAMODE12 = 1), it counts up until the counter value equals the period value and then stops. When the timer is enabled for continuous operation (ENAMODE12 = 2h), the counter counts up until it reaches the period value, then resets itself to zero and begins counting again. When the timer is enabled for continuous operation (ENAMODE12 = 3h), the counter counts up until it reaches the period value, then resets itself to zero, reloads the period registers (PRD12 and PRD34) with the value in the period reload registers (REL12 and REL34), and begins counting again.

Table 3 shows the bit values in TGCR to configure the 32-bit timer in chained mode.

|                                                                                                    | •        |         |           |

|----------------------------------------------------------------------------------------------------|----------|---------|-----------|

|                                                                                                    | TGCR Bit |         | TCR Bit   |

| 32-Bit Timer Configuration                                                                         | TIM12RS  | TIM34RS | ENAMODE12 |

| To place the 32-bit timer chained mode in reset                                                    | 0        | 0       | 0         |

| To disable the 32-bit timer chained mode (out of reset)                                            | 1h       | 1h      | 0         |

| To enable the 32-bit timer chained mode for one-time operation                                     | 1h       | 1h      | 1h        |

| To enable the 32-bit timer chained mode for continuous operation                                   | 1h       | 1h      | 2h        |

| To enable the 32-bit timer chained mode for continuous operation with period reload (Timer 3 only) | 1h       | 1h      | 3h        |

#### Table 3. 32-Bit Timer Chained Mode Configurations

Once the timer stops, if an external clock is used as the timer clock, the timer must remain disabled for at least one external clock period or the timer will not start counting again. When using the external clock, the count value is synchronized to the internal clock.

Note that when both the timer counter and timer period are cleared to 0, the timer can be enabled but the timer counter does not increment because the timer period is 0.

## 2.1.4.2.1.2 32-Bit Timer Chained Mode Configuration Procedure

To configure the GP timer to operate as a dual 32-bit chained mode timer, follow the steps below:

- 1. Select 32-bit chained mode (TIMMODE in TGCR).

- 2. Remove the timer from reset (TIM12RS and TIM34RS in TGCR).

- 3. Select the desired timer period (PRD12).

- 4. Select the desired timer prescaler value (PRD34).

- 5. Enable the timer (ENAMODE12 in TCR).

- 6. If ENAMODE12 = 3h, write the desired timer period for the next timer cycle in the period reload registers (REL12 and REL34). This step can be done at any time before the current timer cycle ends.

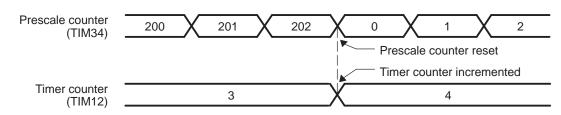

## 2.1.4.2.2 Unchained Mode

The general-purpose timers can be configured as a dual 32-bit unchained timers by setting the TIMMODE bit to 1 in TGCR.

In the unchained mode (Figure 6), the timer operates as two independent 32-bit timers. One 32-bit timer (timer 3:4) operates as a 32-bit timer being clocked by a 4-bit prescaler. The other 32-bit timer (timer 1:2) operates as a 32-bit timer with no prescaler.

Independent of the normal timer behavior, eight compare registers (CMP*n*) are compared against the value of the TIM12 register when the PLUSEN bit in TGCR is set. Upon a successful non-zero match, an interrupt and a DMA event are generated without affecting the TIM12 value, behavior, or associated counter registers. Note that some timer instantiations may not map the CMP interrupt and DMA events to the CPU and DMA engines (see your device-specific data manual for information).

#### Figure 6. Dual 32-Bit Timers Unchained Mode Block Diagram

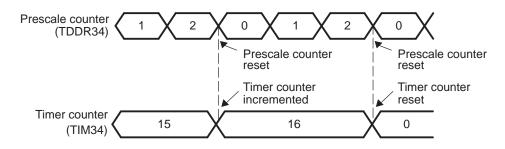

#### 2.1.4.2.2.1 32-Bit Timer With a 4-Bit Prescaler

In the unchained mode, the 4-bit prescale can be clocked by the internal clock or an external clock source. Use CLKSRC34 to select the clock source. The 4-bit prescaler uses the timer divide-down ratio (TDDR34) bit in TGCR to form a 4-bit prescale counter register and the prescale counter bits (PSC34) to form a 4-bit prescale period register (see Figure 6). When the timer is enabled, the prescale counter starts incrementing by 1 at every timer input clock cycle. One cycle after the prescale counter matches the prescale period, a clock signal is generated for the 32-bit timer.

The 32-bit timer uses TIM34 as a 32-bit timer counter register and PRD34 as a 32-bit timer period register. The 32-bit timer is clocked by the output clock from the 4-bit prescaler (see the example in Figure 7). The timer counter increments by 1 at every prescaler output clock cycle. When the timer counter matches the period, a maskable timer interrupt (TINT*n*), a timer DMA event (TEVT*n*), and a timer output event to TM64P\_OUT*n* are generated. When the timer is configured in continuous mode, the timer counter is reset to 0 on the cycle after the timer counter reaches the timer period. The timer can be stopped, restarted, reset, or disabled using the TIM34RS bit in TGCR. For timer 3:4, the lower 16 bits of the timer control register (TCR) have no control.

Figure 7. Dual 32-Bit Timers Unchained Mode Example

4-bit prescaler settings: count = TDDR34 = 1; period = PSC34 = 2 32-bit timer settings: count = TIM34 = 15; period = PRD34 = 16

## 2.1.4.2.2.2 32-Bit Timer with No Prescaler

The other 32-bit timer (timer 1:2) uses TIM12 as the 32-bit counter register and PRD12 as a 32-bit timer period register (see Figure 6). When the timer is enabled, the timer counter increments by 1 at every timer input clock cycle. When the timer counter matches the timer period, a maskable timer interrupt (TINT*n*), a timer DMA event (TEVT*n*), and a timer output event on TM64P\_OUT*n* are generated. When the timer is configured in continuous mode, the timer counter is reset to 0 on the cycle after the timer counter reaches the timer period. The timer can be stopped, restarted, reset, or disabled using the TIM12RS bit in TGCR. For timer 1:2, the upper 16 bit of the timer control register (TCR) have no control.

#### 2.1.4.2.2.3 Enabling the 32-Bit Unchained Mode Timer

The TIM12RS and TIM34RS bits in TGCR control whether the timer is in reset or capable of operating. The TIM12RS bit controls the reset of the timer 1:2 side of the timer and the TIM34RS bit controls the reset of the timer 3:4 side of the timer. For the timer to operate, the TIM12RS and/or TIM34RS bits must be set to 1.

The ENAMODE*n* bit in the timer control register (TCR) controls whether the timer is disabled, enabled to run once, or enabled to run continuously.

- When the timer is disabled (ENAMODE*n* = 0), the timer does not run and maintains its current count value.

- When the timer is enabled for one time operation (ENAMODE *n* = 1), it counts up until the counter value equals the period value and then stops.

- When the timer is enabled for continuous operation (ENAMODEn = 2h), the counter counts up until it reaches the period value, then resets itself to zero and begins counting again.

- When the timer is enabled for continuous operation with period reload (ENAMODE n = 3h), the counter counts up until it reaches the period value, then resets itself to zero, reloads the period registers (PRD12 and/or PRD34) with the value in the period reload registers (REL12 and/or REL34), and begins counting again.

Table 4 shows the bit values in TGCR to configure the 32-bit timer in unchained mode.

Once the timer stops, if an external clock is used as the timer clock, the timer must remain disabled for at least one external clock period or the timer will not start counting again. When using the external clock, the count value is synchronized to the internal clock.

Note that when both the timer counter and timer period are cleared to 0, the timer can be enabled but the timer counter does not increment because the timer period is 0.

|                                                                                                            | TGCR Bit |         | TCR Bit   |           |

|------------------------------------------------------------------------------------------------------------|----------|---------|-----------|-----------|

| 32-Bit Timer Configuration                                                                                 | TIM12RS  | TIM34RS | ENAMODE12 | ENAMODE34 |

| To place the 32-bit timer unchained mode with 4-bit prescaler in reset                                     | х        | 0       | х         | 0         |

| To disable the 32-bit timer unchained mode with 4-bit prescaler (out of reset)                             | х        | 1h      | х         | 0         |

| To enable the 32-bit timer unchained mode with 4-bit prescaler for one-time operation                      | х        | 1h      | х         | 1h        |

| To enable the 32-bit timer unchained mode with 4-bit prescaler for continuous operation                    | x        | 1h      | x         | 2h        |

| To enable the 32-bit timer unchained mode with 4-bit prescaler for continuous operation with period reload | x        | 1h      | x         | 3h        |

| To place the 32-bit timer unchained mode with no prescaler in reset                                        | 0        | x       | 0         | x         |

| To disable the 32-bit timer unchained mode with no prescaler (out of reset)                                | 1h       | Х       | 0         | x         |

| To enable the 32-bit timer unchained mode with no prescaler for one-time operation                         | 1h       | Х       | 1h        | x         |

| To enable the 32-bit timer unchained mode with no prescaler for continuous operation                       | 1h       | х       | 2h        | x         |

| To enable the 32-bit timer unchained mode with no prescaler for<br>continuous operation with period reload | 1h       | x       | 3h        | x         |

#### Table 4. 32-Bit Timer Unchained Mode Configurations

#### 2.1.4.2.2.4 32-Bit Timer Unchained Mode Configuration Procedure

- To configure timer 1:2, follow the steps below:

- 1. Select 32-bit unchained mode (TIMMODE in TGCR).

- 2. Remove the timer 1:2 from reset (TIM12RS in TGCR).

- 3. Select the desired timer period for timer 1:2 (PRD12).

- 4. Select the desired clock source for timer 1:2 (CLKSRC12 in TCR).

- 5. Enable timer 1:2 (ENAMODE12 in TCR).

- 6. If ENAMODE12 = 3h, write the desired timer period for the next timer cycle in the period reload register (REL12). This step can be done at any time before the current timer cycle ends.

To configure timer 3:4, follow the steps below:

- 1. Select 32-bit unchained mode (TIMMODE in TGCR).

- 2. Remove the timer 3:4 from reset (TIM34RS in TGCR).

- 3. Select the desired timer period for timer 3:4 (PRD34).

- 4. Select the desired prescaler value for timer 3:4 (PSC34 in TGCR).

- 5. Enable timer 3:4 (ENAMODE34 in TCR).

- 6. If ENAMODE34 = 3h, write the desired timer period for the next timer cycle in the period reload register (REL34). This step can be done at any time before the current timer cycle ends.

#### 2.1.4.2.2.5 Event Capture Mode

When the PLUSEN bit in the timer global control register (TGCR) is set, Event Capture Mode is available. Event Capture Mode is available only when the timer is configured in 32-bit unchained mode. When Event Capture Mode is enabled, the timer cycle is restarted when an external input event occurs. In particular, when an external input event occurs, the timer stops counting, generates output events (TINT*n*, TEVT*n*, and TM64P\_OUT*n*), copies values from the timer counter registers (TIM12 and/or TIM34) to the timer capture registers (CAP12 and/or CAP34), reloads the timer period registers (PRD12 and/or PRD34) if in continuous mode with period reload (ENAMODE = 3h), and then restarts counting in continuous mode. Event Capture Mode is available only when the timer clock source is the internal timer (CLKSRC = 0) and the timer is in continuous mode (ENAMODE = 2h or 3h).

The external input event for the timer 1:2 side of the timer comes from TM64P\_IN12; the external input event for the timer 3:4 side of the timer comes from TM64P\_IN34.

Capture mode is enabled using the Capture mode enable bit (CAPMODE12 and/or CAPMODE34) in the timer control register (TCR). The type of input event is selected by the capture event mode bit (CAPEVTMODE12 and/or CAPEVTMODE34) in the timer control register (TCR). All of the following input event types are available:

- Rising edge of input signal

- Falling edge of input signal

- Rising or falling edge of input signal

## 2.1.4.2.2.6 Timer Counter Register Read Reset Mode

Read Reset Mode is available when the PLUSEN bit in the timer global control register (TGCR) is set and the timer is configured in 32-bit unchained mode. When Read Reset Mode is enabled, the timer cycle is restarted when the timer counter registers are read (TIM12 and/or TIM34). In particular, when the timer registers are read, the timer stops counting, copies values from the timer counter registers (TIM12 and/or TIM34) to the timer capture registers (CAP12 and/or CAP34), reloads the timer period registers (PRD12 and/or PRD34) if in continuous mode with period reload (ENAMODE = 3h), and then restarts counting in continuous mode. Timer output events (TINT*n*, TEVT*n*, and TM64P\_OUT*n*) are not generated during this process. Read Reset Mode is enabled using the read reset mode enable bit (READRSTMODE) in the timer control register (TCR).

#### 2.1.4.3 Timer Capture Registers

When the timer has a timeout due to a normal expiration of timer, external input event in Event Capture Mode, or read of timer counter registers in Read Reset Mode, the values of the timer counter registers (TIM12 and TIM34) are copied onto the timer counter capture registers (CAP12 and CAP34). Note that the value in TDDR is not captured when a read of TIM34 happens.

#### 2.1.4.4 Counter and Period Registers Used in GP Timer Modes

Table 5 summarizes how the counter registers (TIM*n*) and period registers (PRD*n*) are used in each GP timer mode.

| Timer Mode                       | Counter Registers     | Period Registers     |  |

|----------------------------------|-----------------------|----------------------|--|

| 64-bit general-purpose           | TIM34:TIM12           | PRD34:PRD12          |  |

| Dual 32-bit chained:             |                       |                      |  |

| Prescaler (Timer 3:4)            | TIM34                 | PRD34                |  |

| Timer (Timer 1:2)                | TIM12                 | PRD12                |  |

| Dual 32-bit unchained:           |                       |                      |  |

| Timer (Timer 1:2)                | TIM12                 | PRD12                |  |

| Timer with prescaler (Timer 3:4) | TDDR34 bits and TIM34 | PSC34 bits and PRD34 |  |

#### Table 5. Counter and Period Registers Used in GP Timer Modes

#### 2.1.5 Timer Operation Boundary Conditions

The following boundary conditions affect the timer operation.

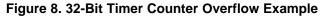

#### 2.1.5.1 Timer Counter Overflow

Timer counter overflow can happen when the timer counter register is set to a value greater than the value in the timer period register. The counter reaches its maximum value (FFFF FFFFh or FFFF FFFF FFFFh), rolls over to 0, and continues counting until it reaches the timer period. An example is in Figure 8.

#### 2.1.5.2 Writing to Registers of an Active Timer

Writes to most timer registers are not allowed when the timer is active, except for setting the timer period reload registers (REL12 and REL34) and stopping and resetting the timers. In the 64-bit and dual 32-bit timer modes, registers that are protected by hardware are:

- TIM12

- TIM34

- PRD12

- PRD34

- TCR (except the ENAMODE bit)

- TGCR (except the TIM12RS and TIM34RS bits)

#### 2.1.6 General-Purpose Timer Power Management

The timer can be placed in reduced power modes to conserve power during periods of low activity. The power management of the peripheral is controlled by the processor Power and Sleep Controller (PSC). The PSC acts as a master controller for power management for all of the peripherals on the device. For detailed information on power management procedures using the PSC, see your device-specific *System Reference Guide*. The timer can be placed in an idle mode to conserve power when it is not being used.

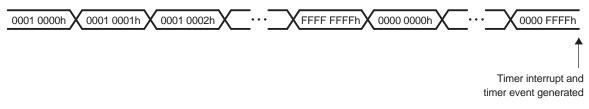

## 2.2 Architecture – Watchdog Timer Mode

This section describes the use of timer as a watchdog timer. In order to fully function in watchdog timer mode, the timer must be connected to the device hardware reset signal. For information on which timer instantiation can function as a watchdog timer, see your device-specific data manual.

#### 2.2.1 Watchdog Timer

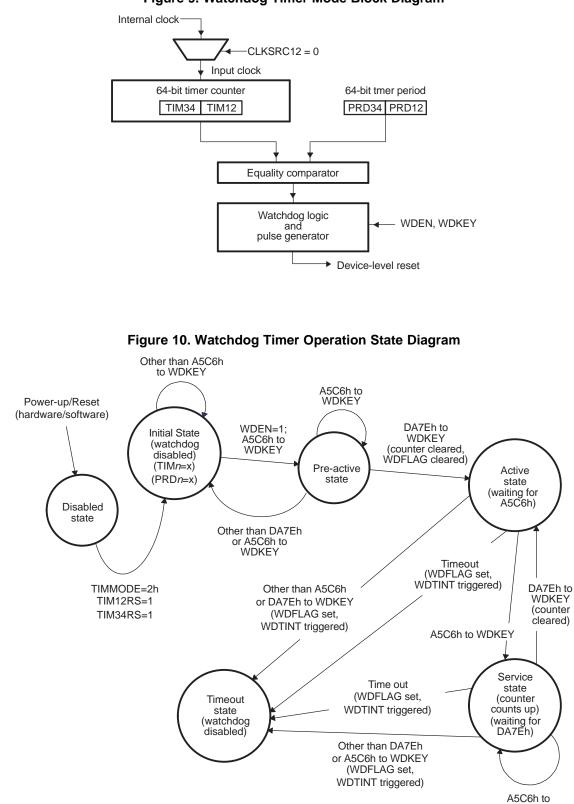

As a 64-bit watchdog timer, the peripheral can be used to prevent system lockup when the software becomes trapped in loops with no controlled exit.

After a hardware reset, the watchdog timer is disabled. The timer then can be configured as a watchdog timer using the timer mode (TIMMODE) bit in the timer global control register (TGCR) and the watchdog timer enable (WDEN) bit in the watchdog timer control register (WDTCR). In the watchdog timer mode, the timer requires a special service sequence to be executed periodically. Without this periodic servicing, the timer counter increments until it matches the timer period and causes a watchdog timeout event.

When the timeout event occurs, the watchdog timer resets the entire processor.

#### 2.2.2 Watchdog Timer Mode Restrictions

The watchdog timer mode has the following restrictions:

- No external clock source

- No one-time enabling

#### 2.2.3 Watchdog Timer Mode Operation

The watchdog timer mode is selected and enabled when:

- TIMMODE = 2h in TGCR

- WDEN = 1 in WDTCR

Figure 9 shows the timer when it is used in the watchdog timer mode. The counter registers (TIM12 and TIM34) form a 64-bit timer counter register and the period registers (PRD12 and PRD34) form a 64-bit period register. When the timer counter matches the timer period, the timer generates a watchdog timeout event which resets the entire processor.

To activate the watchdog timer, a certain sequence of events must be followed, as shown in the state diagram of Figure 10.

Once the watchdog timer is activated, it can be disabled only by a watchdog timeout event or by a hardware reset. A special key sequence is required to prevent the watchdog timer from being accidentally serviced while the software is trapped in a loop or by some other software failure.

To prevent a watchdog timeout event, the timer has to be serviced periodically by writing A5C6h followed by DA7Eh to the watchdog timer service key (WDKEY) bits in WDTCR before the timer finishes counting up. Both A5C6h and DA7Eh are allowed to be written to the WDKEY bits, but only the correct sequence of A5C6h followed by DA7Eh to the WDKEY bits services the watchdog timer. Any other writes to the WDKEY bits triggers the watchdog timeout event immediately.

Figure 9. Watchdog Timer Mode Block Diagram

WDKEY

When the watchdog timer is in the Timeout state, the watchdog timer is disabled, the WDEN bit is cleared to 0, and the timer is reset. After entering the Timeout state, the watchdog timer cannot be enabled again until a hardware reset occurs.

After a hardware reset, the watchdog timer is disabled; however, reads or writes to the watchdog timer registers are allowed. Once the WDEN bit is set (enabling the watchdog timer) and A5C6h is written to the WDKEY bits, the watchdog timer enters the Pre-active state. In the Pre-active state:

- A write to WDTCR is allowed only when the write comes with the correct key (A5C6h or DA7Eh) to the WDKEY bits.

- A write of DA7Eh to the WDKEY bits when the WDEN bit is set to 1 resets the counters and activates the watchdog timer.

The watchdog timer must be configured before the watchdog timer enters the Active state. The WDEN bit must be set to 1 before writing DA7Eh to the WDKEY bits in the Pre-active state. Every time the watchdog timer is serviced by the correct WDKEY sequence, the watchdog timer counter is automatically reset.

#### 2.2.4 Watchdog Timer Register Write Protection

Once the watchdog timer enters the Pre-active state (see Figure 10), writes to TIM12, TIM34, PRD12, PRD34, and WDTCR are write protected (except for the WDKEY field). While the watchdog timer is in the Timeout state, writing to the WDEN bit has no effect.

Once the watchdog timer enters its Initial state (see Figure 10), do not write to TGCR.

#### 2.2.5 Watchdog Timer Power Management

The watchdog timer cannot be placed in power-down mode.

#### 2.3 Reset Considerations

The timer has two reset sources: hardware reset and the timer reset (TIM12RS and TIM34RS) bits in the timer global control register (TGCR).

#### 2.3.1 Software Reset Considerations

When the TIM12RS bit in TGCR is cleared to 0, the TIM12 register is held with the current value.

When the TIM34RS bit in TGCR is cleared to 0, the TIM34 register is held with the current value.

#### 2.3.2 Hardware Reset Considerations

When a hardware reset is asserted, all timer registers are set to their default values.

#### 2.4 Interrupt Support

Each of the timers can send either one of two separate interrupt events (TINT*n*) to the CPU, depending on the operating mode of the timer. The timer interrupts are generated when the count value in the counter register reaches the value specified in the period register. For supported interrupts, see your device-specific *System Reference Guide*.

When the PLUSEN bit in the timer global control register (TGCR) is set, matches between TIM12 and CMP*n* in dual 32-bit unchained mode will also generate interrupts. Setting the PLUSEN bit also enables additional features for control, status, and generation of interrupts. See Section 2.8 for more information.

#### 2.5 DMA Event Support

Each of the timers can send either one of two separate timer events (TEVT*n*) to the DMA engine, depending on the operating mode the timer. The timer events are generated when the count value in the counters register reaches the value specified in the period register. For the supported DMA events, see your device-specific *System Reference Guide*.

#### Architecture

www.ti.com

When the PLUSEN bit in the timer global control register (TGCR) is set, matches between TIM12 and CMP*n* in dual 32-bit unchained mode will also generate DMA events. Setting the PLUSEN bit also enables additional features for control, status, and generation of dma events are enabled. See Section 2.8 for more information.

## 2.6 TM64P\_OUT Event Support

The timer can generate output pulse (Figure 11) or clock (Figure 12) signals on the TM64P\_OUT*n* output pins. The output signals are generated when the count value in the counter registers reaches the value specified in the period registers (TSTAT drives the TM64P\_OUT pins). The timer 1:2 side of the timer generates events on TM64P\_OUT12, while the timer 3:4 side of the timer generates events on TM64P\_OUT34. Table 6 gives equations for various TSTAT timing parameters in pulse and clock modes.

The output mode is selected with the clock/pulse bit (CP*n*) in the timer control register (TCR). In pulse mode, the PWID*n* bit in TCR sets the pulse width between 1 to 4 timer clock periods. The TM64P\_OUT*n* pins may be inverted using the INVOUTP*n* bit in TCR.

| Mode  | Frequency                                                       | Period                                                             | Width High                                | Width Low                                                       |

|-------|-----------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------|

| Pulse | f (clock source)<br>timer period register                       | tim <u>er period regis</u> ter<br>f (clock source)                 | $\frac{(PWID + 1)}{f (clock source)}$     | timer per <u>iod register - (P</u> WID + 1)<br>f (clock source) |

| Clock | $\frac{f (clock \ source)}{2 \times timer \ period \ register}$ | $2 \times \underline{timer \ period \ reg}$ ister f (clock source) | timer period register<br>f (clock source) | timer period register<br>f (clock source)                       |

## 2.7 External Timer Pin GPIO Mode

The external timer pins (TM64P\_IN*n* and TM64P\_OUT*n*) can be individually configured to function as general-purpose input/output (GPIO) pins. In GPIO mode, the pins are able to detect and drive arbitrary data. The pins are also able to source external interrupt events. Some timer instantiations may not have external pins, see your device-specific data manual for pin information.

The GPIO interrupt and GPIO enable register (GPINTGPEN) enables the GPIO mode and associated interrupts. The GPIO data and GPIO direction register (GPDATGPDIR) determines if GPIO-enabled pins are used as input or output pins; and it is the means by which data is read-from or written-to the GPIO pins.

Normal timer counting modes cannot be used when the GPIO mode is enabled -- TIM*n*RS in the timer global control register (TGCR) cannot be brought out of reset when GPEN*n* in GPINTGPEN is asserted.

## 2.8 Interrupt/DMA Event Generation Control and Status

When the PLUSEN bit in the timer global control register (TGCR) is set, the timer supports additional features for control and status of interrupt and DMA event generation. Interrupt/DMA events are generated when the count value in the counter registers reaches the value specified in the period registers and they are also generated when Event Capture Mode is enabled and an external event occurs. To generate events in the case when the value specified in the period registers equals the value specified in the period registers, set the period compare interrupt enable bit (PRDINTEN*n*) in the interrupt control and status register (INTCTLSTAT). The event status for this case is reflected in the period compare interrupt status bit (PRDINTSTAT*n*), which is also in INTCTLSTAT. The PRDINTSTAT*n* bit is cleared by writing a 1 to the bit. Similarly, to generate events in Event Capture Mode, set the event interrupt status bit (EVTINTEN*n*) in INTCTLSTAT. The EVTINTSTAT*n* bit is cleared by writing a 1 to the bit.

## 2.9 Power Management

The general-purpose timers can be placed in reduced power modes to conserve power during periods of low activity. The power management of the peripheral is controlled by the processor Power and Sleep Controller (PSC). The PSC acts as a master controller for power management for all of the peripherals on the device. For detailed information on power management procedures using the PSC, see your device-specific *System Reference Guide*.

## 2.10 Emulation Considerations

Each timer has an emulation management register (EMUMGT). As shown in Table 7, the FREE and SOFT bits of EMUMGT determine how the timer responds to an emulation suspend event. An emulation suspend event corresponds to any type of emulator access to the CPU, such as a hardware or software breakpoint or a probe point.

Note that during emulation, the timer count values will increment once every timer peripheral clock (not CPU clock). So when single-steeping though code, the timer values will not update on every CPU clock cycle.

The timer can respond to emulation events from the CPU based on the configuration of the emulation suspend source register (SUSPSRC) in the system configuration module. See your device-specific *System Reference Guide* for information on SUSPSRC and how it is configured.

TEXAS INSTRUMENTS

www.ti.com

| FREE | SOFT | Emulation Mode                                                                                              |  |  |  |

|------|------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| 0    | 0    | The timer stops immediately.                                                                                |  |  |  |

| 0    | 1    | The timer stops when the timer counter value increments and reaches the value in the timer period register. |  |  |  |

| 1    | х    | The timer runs free regardless of SOFT bit status.                                                          |  |  |  |

Table 7. Timer Emulation Modes Selection

## 3 Registers

Registers

Table 8 lists the memory-mapped registers for the 64-bit Timer Plus. See your device-specific datamanual for the memory address of these registers. All other register offset addresses not listed in Table 8should be considered as reserved locations and the register contents should not be modified.

| Offset | Acronym    | Register Description                        | Section      |

|--------|------------|---------------------------------------------|--------------|

| 0h     | REVID      | Revision ID Register                        | Section 3.1  |

| 4h     | EMUMGT     | Emulation Management Register               | Section 3.2  |

| 8h     | GPINTGPEN  | GPIO Interrupt and GPIO Enable Register     | Section 3.3  |

| Ch     | GPDATGPDIR | GPIO Data and GPIO Direction Register       | Section 3.4  |

| 10h    | TIM12      | Timer Counter Register 12                   | Section 3.5  |

| 14h    | TIM34      | Timer Counter Register 34                   | Section 3.5  |

| 18h    | PRD12      | Timer Period Register 12                    | Section 3.6  |

| 1Ch    | PRD34      | Timer Period Register 34                    | Section 3.6  |

| 20h    | TCR        | Timer Control Register                      | Section 3.7  |

| 24h    | TGCR       | Timer Global Control Register               | Section 3.8  |

| 28h    | WDTCR      | Watchdog Timer Control Register             | Section 3.9  |

| 34h    | REL12      | Timer Reload Register 12                    | Section 3.10 |

| 38h    | REL34      | Timer Reload Register 34                    | Section 3.11 |

| 3Ch    | CAP12      | Timer Capture Register 12                   | Section 3.12 |

| 40h    | CAP34      | Timer Capture Register 34                   | Section 3.13 |

| 44h    | INTCTLSTAT | Timer Interrupt Control and Status Register | Section 3.14 |

| 60h    | CMP0       | Compare Register 0                          | Section 3.15 |

| 64h    | CMP1       | Compare Register 1                          | Section 3.15 |

| 68h    | CMP2       | Compare Register 2                          | Section 3.15 |

| 6Ch    | CMP3       | Compare Register 3                          | Section 3.15 |

| 70h    | CMP4       | Compare Register 4                          | Section 3.15 |

| 74h    | CMP5       | Compare Register 5                          | Section 3.15 |

| 78h    | CMP6       | Compare Register 6                          | Section 3.15 |

| 7Ch    | CMP7       | Compare Register 7                          | Section 3.15 |

#### **Table 8. Timer Registers**

## 3.1 Revision ID Register (REVID)

The revision ID register (REVID) contains the peripheral revision. The REVID is shown in Figure 13 and described in Table 9.

#### Figure 13. Revision ID Register (REVID)

| 31           | 0 |

|--------------|---|

| REV          |   |

| R-4472 0211h |   |

LEGEND: R = Read only; -n = value after reset

#### Table 9. Revision ID Register (REVID) Field Descriptions

| Bit  | Field | Value      | Description               |

|------|-------|------------|---------------------------|

| 31-0 | REV   | 4472 0211h | Revision ID of the Timer. |

## 3.2 Emulation Management Register (EMUMGT)

The emulation management register (EMUMGT) is shown in Figure 14 and described in Table 10.

| 31 |          |   |       | 16    |

|----|----------|---|-------|-------|

|    | Reserved |   |       |       |

|    | R-0      |   |       |       |

|    |          |   |       |       |

| 15 |          | 2 | 1     | 0     |

|    | Reserved |   | SOFT  | FREE  |

|    | R-0      |   | R/W-0 | R/W-0 |

Figure 14. Emulation Management Register (EMUMGT)

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

| Bit  | Field    | Value | Description                                                                                                                   |

|------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------|

| 31-2 | Reserved | 0     | Reserved                                                                                                                      |

| 1    | SOFT     |       | Determines emulation mode functionality of the timer. When the FREE bit is cleared to 0, the SOFT bit selects the timer mode. |

|      |          | 0     | The timer stops immediately.                                                                                                  |

|      |          | 1     | The timer stops when the counter increments and reaches the value in the timer period register (PRDn).                        |

| 0    | FREE     |       | Determines emulation mode functionality of the timer. When the FREE bit is cleared to 0, the SOFT bit selects the timer mode. |

|      |          | 0     | The SOFT bit selects the timer mode.                                                                                          |

|      |          | 1     | The timer runs free regardless of the SOFT bit.                                                                               |

## Table 10. Emulation Management Register (EMUMGT) Field Descriptions

27

64-Bit Timer Plus

Registers

## 3.3 GPIO Interrupt Control and Enable Register (GPINTGPEN)

The GPIO interrupt control and enable register (GPINTGPEN) is shown in Figure 15 and described in Table 11.

|      | Fig  | jure 15. GPIO Ir | iterrupt Contro | of and Enable | e Register ( | GPINI GPEN) |          |

|------|------|------------------|-----------------|---------------|--------------|-------------|----------|

| 31   |      |                  |                 |               | 26           | 25          | 24       |

|      |      | Rese             | erved           |               |              | GPENO34     | GPENI34  |

|      |      | R                | -0              |               |              | R/W-0       | R/W-0    |

| 23   |      |                  |                 |               | 18           | 17          | 16       |

|      |      | Rese             | erved           |               |              | GPENO12     | GPENI12  |

|      | R-0  |                  |                 |               |              | R/W-0       | R/W-0    |

| 15   | 14   | 13               | 12              | 11            | 10           | 9           | 8        |

| Rese | rved | GPINT34INVO      | GPINT34INVI     | Rese          | erved        | GPINT34ENO  | GPINT34E |

| R-0  |      | R/W-0            | R/W-0           | R             | -0           | R/W-0       | R/W-0    |

| 7    | 6    | 5                | 4               | 3             | 2            | 1           | 0        |

| Rese | rved | GPINT12INVO      | GPINT12INVI     | Rese          | erved        | GPINT12ENO  | GPINT12E |

| R-   | 0    | R/W-0            | R/W-0           | R             | -0           | R/W-0       | R/W-0    |

## Figure 15. GPIO Interrupt Control and Enable Register (GPINTGPEN)

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Table 11. GPIO Interrupt Control and Enable Register (GPINTGPEN) Field Descriptions

| Bit   | Field       | Value | Description                                                        |

|-------|-------------|-------|--------------------------------------------------------------------|

| 31-26 | Reserved    | 0     | Reserved                                                           |

| 25    | GPENO34     |       | Enable TM64P_OUT34 to function in GPIO mode.                       |

|       |             | 0     | TM64P_OUT34 is used as a TIMER output mode.                        |

|       |             | 1     | TM64P_OUT34 is used as a GPIO pin.                                 |

| 24    | GPENI34     |       | Enable TM64P_IN34 to function in GPIO mode.                        |

|       |             | 0     | TM64P_IN34 is used as a TIMER input pin.                           |

|       |             | 1     | TM64P_IN34 is used as a GPIO pin.                                  |

| 23-18 | Reserved    | 0     | Reserved                                                           |

| 17    | GPENO12     |       | Enable TM64P_OUT12 to function in GPIO mode.                       |

|       |             | 0     | TM64P_OUT12 is used as a TIMER output pin.                         |

|       |             | 1     | TM64P_OUT12 is used as a GPIO pin.                                 |

| 16    | GPENI12     |       | Enable TM64P_IN12 to function in GPIO mode                         |

|       |             | 0     | TM64P_IN12 is used as a TIMER input pin.                           |

|       |             | 1     | TM64P_IN12 is used as a GPIO pin.                                  |

| 15-14 | Reserved    | 0     | Reserved                                                           |

| 13    | GPINT34INVO |       | Invert interrupt/event signal for TM64P_OUT34 when GPINT34ENO = 1. |

|       |             | 0     | Rising signal edge on TM64P_OUT34 generates the interrupt/event.   |

|       |             | 1     | Falling signal edge on TM64P_OUT34 generates the interrupt/event.  |

| 12    | GPINT34INVI |       | Invert interrupt/event signal for TM64P_IN34 when GPINT34ENI = 1.  |

|       |             | 0     | Rising signal edge on TM64P_IN34 generates the interrupt/event.    |

|       |             | 1     | Falling signal edge on TM64P_IN34 generates the interrupt/event.   |

| 11-10 | Reserved    | 0     | Reserved                                                           |

## Table 11. GPIO Interrupt Control and Enable Register (GPINTGPEN) Field Descriptions (continued)

| Bit | Field       | Value | Description                                                         |

|-----|-------------|-------|---------------------------------------------------------------------|

| 9   | GPINT34ENO  |       | Enable TM64P_OUT34 to source interrupts/events in GPIO mode.        |

|     |             | 0     | Timer interrupts/events are sourced in TIMER mode.                  |

|     |             | 1     | Timer interrupts/events are sourced externally from TM64P_OUT34.    |

| 8   | GPINT34ENI  |       | Enable TM64P_IN34 to source interrupts/events in GPIO mode.         |

|     |             | 0     | Timer interrupts/events are sourced in TIMER mode.                  |

|     |             | 1     | Timer interrupts/events are sourced externally from TM64P_IN34.     |

| 7-6 | Reserved    | 0     | Reserved                                                            |

| 5   | GPINT12INVO |       | Invert interrupt/event signal from TM64P_OUT12 when GPINT12ENO = 1. |

|     |             | 0     | Rising signal edge on TM64P_OUT12 generates the interrupt/event.    |

|     |             | 1     | Falling signal edge on TM64P_OUT12 generates the interrupt/event.   |

| 4   | GPINT12INVI |       | Invert interrupt/event signal for TM64P_IN12 when GPINT12ENI = 1.   |

|     |             | 0     | Rising signal edge on TM64P_IN12 generates the interrupt/event.     |

|     |             | 1     | Falling signal edge on TM64P_IN12 generates the interrupt/event.    |

| 3-2 | Reserved    | 0     | Reserved                                                            |

| 1   | GPINT12ENO  |       | Enable TM64P_OUT12 to source interrupts/events in GPIO mode.        |

|     |             | 0     | Timer interrupts/events are sourced in TIMER mode.                  |

|     |             | 1     | Timer interrupts/events are sourced externally from TM64P_OUT12.    |

| 0   | GPINT12ENI  |       | Enable TM64P_IN12 to source interrupts/events in GPIO mode.         |

|     |             | 0     | Timer interrupts/events are sourced in TIMER mode.                  |

|     |             | 1     | Timer interrupts/events are sourced externally from TM64P_IN12.     |

Texas Instruments

www.ti.com

Registers

## 3.4 GPIO Data and Direction Register (GPDATGPDIR)

The GPIO data and direction register (GPDATGPDIR) is shown in Figure 16 and described in Table 12.

|    |          |    | <b>J</b> |          |    | · J · · · (· |    | - ,      |          |

|----|----------|----|----------|----------|----|--------------|----|----------|----------|

| 31 |          | 26 | 25       | 24       | 23 |              | 18 | 17       | 16       |

|    | Reserved |    | GPDIRO34 | GPDIRI34 |    | Reserved     |    | GPDIRO12 | GPDIRI12 |

|    | R-0      |    | R/W-0    | R/W-0    |    | R-0          |    | R/W-0    | R/W-0    |

| 15 |          | 10 | 9        | 8        | 7  |              | 2  | 1        | 0        |

|    | Reserved |    | GPDATO34 | GPDATI34 |    | Reserved     |    | GPDATO12 | GPDATI12 |

|    | R-0      |    | R/W-0    | R/W-0    |    | R-0          |    | R/W-0    | R/W-0    |

## Figure 16. GPIO Data and Direction Register (GPDATGPDIR)

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 12. GPIO Data and Direction Register (GPDATGPDIR) Field Descriptions

| Bit   | Field    | Value | Description                                                                                                                       |

|-------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31-26 | Reserved | 0     | Reserved                                                                                                                          |

| 25    | GPDIRO34 |       | Select direction of TM64P_OUT34 in GPIO mode.                                                                                     |

|       |          | 0     | TM64P_OUT34 functions as an input pin in GPIO mode.                                                                               |

|       |          | 1     | TM64P_OUT34 functions as an output pin in GPIO mode (TM64P_OUT34 cannot capture GPIO interrupt events when configured as output). |

| 24    | GPDIRI34 |       | Select direction of TM64P_IN34 in GPIO mode.                                                                                      |

|       |          | 0     | TM64P_IN34 functions as an input pin in GPIO mode.                                                                                |

|       |          | 1     | TM64P_IN34 functions as an output pin in GPIO mode (TM64P_IN34 cannot capture GPIO interrupt events when configured as output).   |

| 23-18 | Reserved | 0     | Reserved                                                                                                                          |

| 17    | GPDIRO12 |       | Select direction of TM64P_OUT12 in GPIO mode.                                                                                     |

|       |          | 0     | TM64P_OUT12 functions as an input pin in GPIO mode.                                                                               |

|       |          | 1     | TM64P_OUT12 functions as an output pin in GPIO mode (TM64P_OUT12 cannot capture GPIO interrupt events when configured as output). |

| 16    | GPDIRI12 |       | Select direction of TM64P_IN12 in GPIO mode.                                                                                      |

|       |          | 0     | TM64P_IN12 functions as an input pin in GPIO mode.                                                                                |

|       |          | 1     | TM64P_IN12 functions as an output pin in GPIO mode (TM64P_IN12 cannot capture GPIO interrupt events when configured as output).   |

| 15-10 | Reserved | 0     | Reserved                                                                                                                          |

| 9     | GPDATO34 |       | Data on TM64P_OUT34 in GPIO mode. Only valid when GPENO34 = 1.                                                                    |

|       |          |       | When GPDIRO34 = 0 (input):                                                                                                        |

|       |          | 0     | TM64P_OUT34 is detected logic low.                                                                                                |

|       |          | 1     | TM64P_OUT34 is detected logic high.                                                                                               |

|       |          |       | When GPDIRO34 = 1 (output):                                                                                                       |

|       |          | 0     | TM64P_OUT34 is driven logic low.                                                                                                  |

|       |          | 1     | TM64P_OUT34 is driven logic high.                                                                                                 |

| 8     | GPDATI34 |       | Data on TM64P_IN34 in GPIO mode. Only valid when GPENI34 = 1.                                                                     |

|       |          |       | When GPDIRI34 = 0 (input):                                                                                                        |

|       |          | 0     | TM64P_IN34 is detected logic low.                                                                                                 |

|       |          | 1     | TM64P_IN34 is detected logic high.                                                                                                |

|       |          |       | When GPDIRI34 = 1 (output):                                                                                                       |

|       |          | 0     | TM64P_IN34 is driven logic low.                                                                                                   |

|       |          | 1     | TM64P_IN34 is driven logic high.                                                                                                  |

| 7-2   | Reserved | 0     | Reserved                                                                                                                          |

## Table 12. GPIO Data and Direction Register (GPDATGPDIR) Field Descriptions (continued)

| Bit | Field    | Value | Description                                                    |

|-----|----------|-------|----------------------------------------------------------------|

| 1   | GPDATO12 |       | Data on TM64P_OUT12 in GPIO mode. Only valid when GPENO12 = 1. |

|     |          |       | When GPDIRO12 = 0 (input):                                     |

|     |          | 0     | TM64P_OUT12 is detected logic low.                             |

|     |          | 1     | TM64P_OUT12 is detected logic high.                            |

|     |          |       | When GPDIRO12 = 1 (output):                                    |

|     |          | 0     | TM64P_OUT12 is driven logic low.                               |

|     |          | 1     | TM64P_OUT12 is driven logic high.                              |

| 0   | GPDATI12 |       | Data on TM64P_IN12 in GPIO mode. Only valid when GPENI12 = 1.  |

|     |          |       | When GPDIRI12 = 0 (input):                                     |

|     |          | 0     | TM64P_IN12 is detected logic low.                              |

|     |          | 1     | TM64P_IN12 is detected logic high.                             |

|     |          |       | When GPDIRI12 = 1 (output):                                    |

|     |          | 0     | TM64P_IN12 is driven logic low.                                |

|     |          | 1     | TM64P_IN12 is driven logic high.                               |

Registers

## 3.5 Timer Counter Registers (TIM12 and TIM34)

The timer counter register is a 64-bit wide register. This 64-bit register is divided into two 32-bit registers, TIM12 and TIM34.