## TMS320C674x/OMAP-L1x Processor Liquid Crystal Display Controller (LCDC)

## **User's Guide**

Literature Number: SPRUFM0A June 2009

### Contents

| Prefa | ace     |                                                                                                     |

|-------|---------|-----------------------------------------------------------------------------------------------------|

| 1     | Introd  | uction                                                                                              |

|       | 1.1     | Purpose of the Peripheral 9                                                                         |

|       | 1.2     | Features 10                                                                                         |

|       | 1.3     | Terminology Used in this Document 10                                                                |

| 2     | Archit  | ecture                                                                                              |

|       | 2.1     | Clocking 10                                                                                         |

|       | 2.2     | LCD External I/O Signals 12                                                                         |

|       | 2.3     | DMA Engine 13                                                                                       |

|       | 2.4     | LIDD Controller 14                                                                                  |

|       | 2.5     | Raster Controller 19                                                                                |

| 3     | Regist  | ers                                                                                                 |

|       | 3.1     | LCD Revision Identification Register (REVID)                                                        |

|       | 3.2     | LCD Control Register (LCD_CTRL) 32                                                                  |

|       | 3.3     | LCD Status Register (LCD_STAT) 34                                                                   |

|       | 3.4     | LCD LIDD Control Register (LIDD_CTRL)                                                               |

|       | 3.5     | LCD LIDD CSn Configuration Registers (LIDD_CS0_CONF and LIDD_CS1_CONF)                              |

|       | 3.6     | LCD LIDD CSn Address Read/Write Registers (LIDD_CS0_ADDR and LIDD_CS1_ADDR)                         |

|       | 3.7     | LCD LIDD CSn Data Read/Write Registers (LIDD_CS0_DATA and LIDD_CS1_DATA) 40                         |

|       | 3.8     | LCD Raster Control Register (RASTER_CTRL) 41                                                        |

|       | 3.9     | LCD Raster Timing Register 0 (RASTER_TIMING_0) 48                                                   |

|       | 3.10    | LCD Raster Timing Register 1 (RASTER_TIMING_1) 50                                                   |

|       | 3.11    | LCD Raster Timing Register 2 (RASTER_TIMING_2) 54                                                   |

|       | 3.12    | LCD Raster Subpanel Display Register (RASTER_SUBPANEL)                                              |

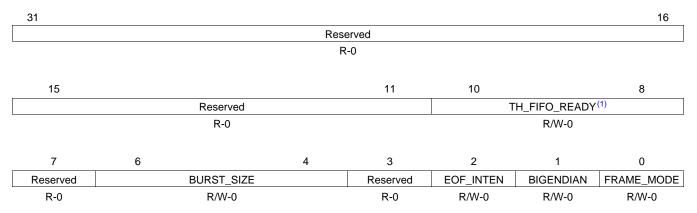

|       | 3.13    | LCD DMA Control Register (LCDDMA_CTRL)                                                              |

|       | 3.14    | LCD DMA Frame Buffer <i>n</i> Base Address Registers (LCDDMA_FB0_BASE and LCDDMA_FB1_BASE)          |

|       | 3.15    | LCD DMA Frame Buffer <i>n</i> Ceiling Address Registers (LCDDMA_FB0_CEILING and LCDDMA_FB1_CEILING) |

| Арре  | endix A | Revision History                                                                                    |

### List of Figures

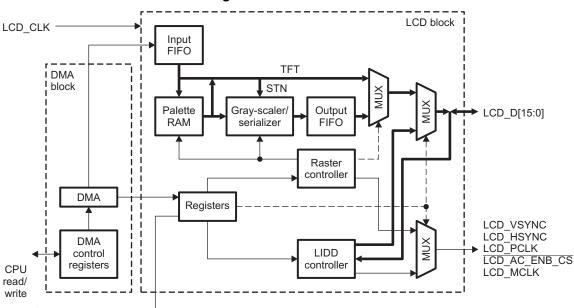

| 1               | LCD Controller                                                                 | . 9      |

|-----------------|--------------------------------------------------------------------------------|----------|

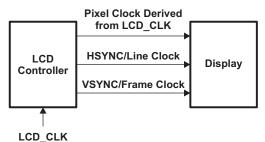

| 2               | Input and Output Clocks                                                        | 10       |

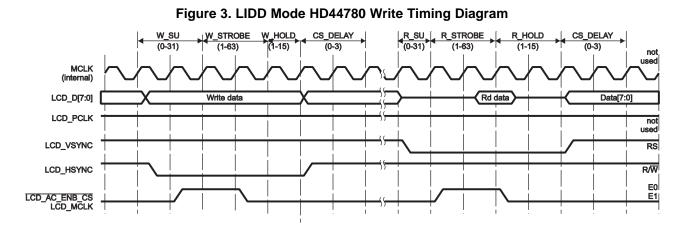

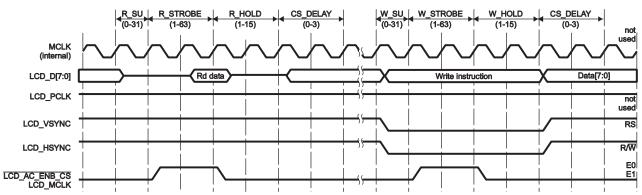

| 3               | LIDD Mode HD44780 Write Timing Diagram                                         | 16       |

| 4               | LIDD Mode HD44780 Read Timing Diagram                                          | 16       |

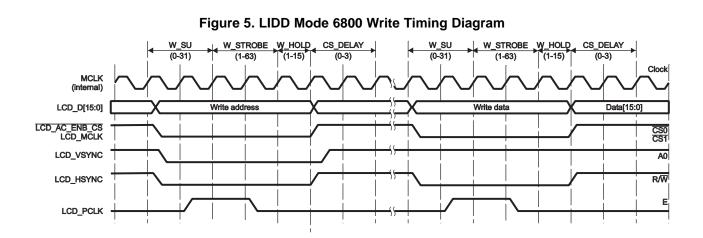

| 5               | LIDD Mode 6800 Write Timing Diagram                                            | 16       |

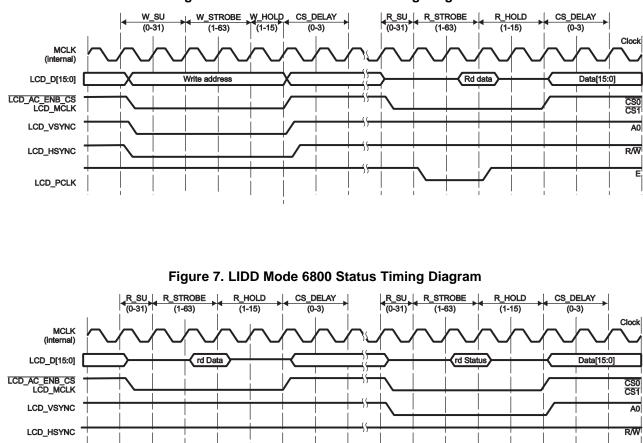

| 6               | LIDD Mode 6800 Read Timing Diagram                                             |          |

| 7               | LIDD Mode 6800 Status Timing Diagram                                           |          |

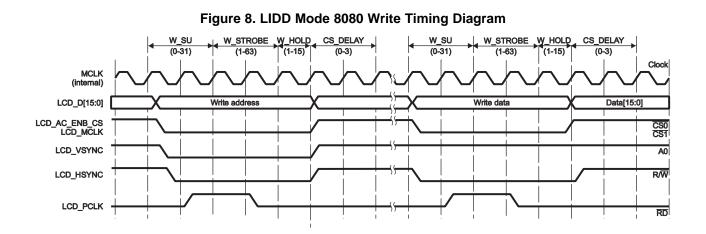

| 8               | LIDD Mode 8080 Write Timing Diagram                                            |          |

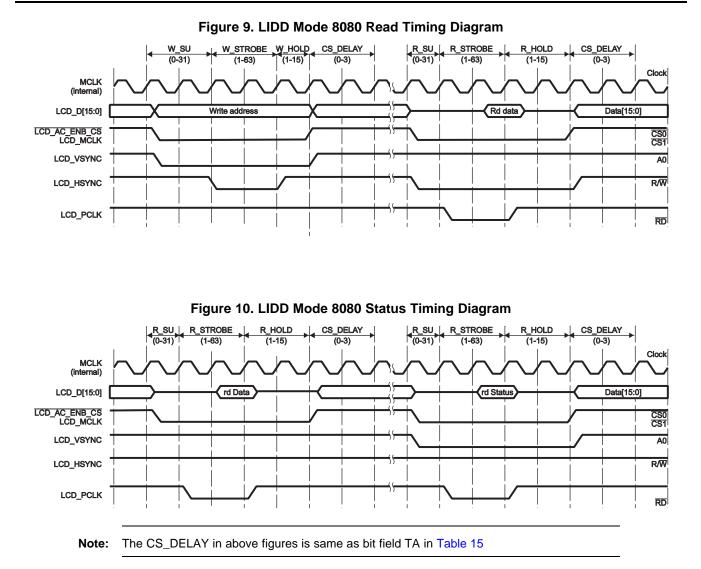

| 9               | LIDD Mode 8080 Read Timing Diagram                                             |          |

| 10              | LIDD Mode 8080 Status Timing Diagram                                           |          |

| 11              | Logical Data Path for Raster Controller                                        |          |

| 12              | Frame Buffer Structure                                                         |          |

| 13              | 16-Entry Palette/Buffer Format (1, 2, 4, 12, 16 BPP)                           |          |

| 14              | 256-Entry Palette/Buffer Format (8 BPP)                                        |          |

| 15              | 16-BPP Data Memory Organization (TFT Mode Only)—Little Endian                  |          |

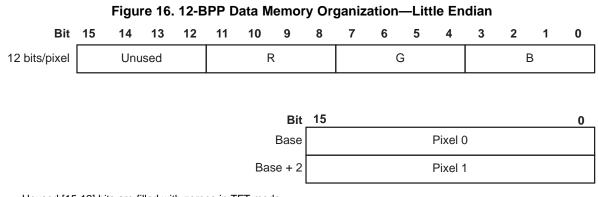

| 16              | 12-BPP Data Memory Organization—Little Endian                                  |          |

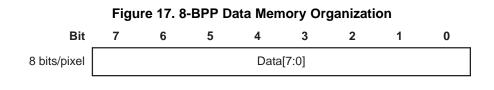

| 17              | 8-BPP Data Memory Organization                                                 |          |

| 18              | 4-BPP Data Memory Organization                                                 |          |

| 19              | 2-BPP Data Memory Organization                                                 |          |

| 20              | 1-BPP Data Memory Organization                                                 |          |

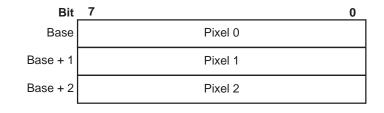

| 21              | Monochrome and Color Output                                                    |          |

| 22              | Raster Mode Display Format                                                     |          |

| 23              | Raster Mode Passive (STN) Timing Diagram                                       |          |

| 24              | Raster Mode Active (TFT) Timing Diagram                                        |          |

| 25              | LCD Revision Identification Register (REVID)                                   |          |

| 26              | LCD Control Register (LCD_CTRL)                                                |          |

| 27              | LCD Status Register (LCD_STAT)                                                 |          |

| 28              | LCD LIDD Control Register (LIDD_CTRL)                                          |          |

| 29              | LCD LIDD CS <i>n</i> Configuration Register (LIDD_CS <i>n</i> _CONF)           |          |

| 30              | LCD LIDD CS <i>n</i> Address Read/Write Register (LIDD_CS <i>n</i> _ADDR)      |          |

| 31              | LCD LIDD CS <i>n</i> Data Read/Write Register (LIDD_CS <i>n</i> _DATA)         |          |

| 32              | LCD Raster Control Register (RASTER_CTRL)                                      |          |

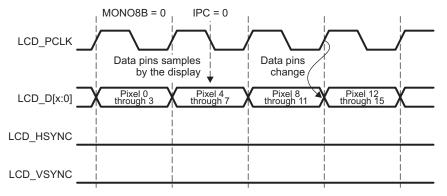

| 33              | Monochrome Passive Mode Pixel Clock and Data Pin Timing                        |          |

| 34              | Color Passive Mode Pixel Clock and Data Pin Timing                             |          |

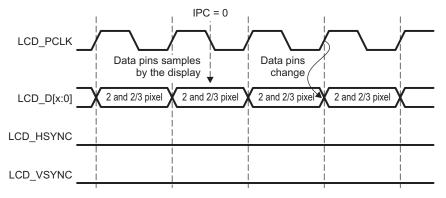

| 35              | Active Mode Pixel Clock and Data Pin Timing                                    |          |

| 36              | TFT Alternate Signal Mapping Output                                            |          |

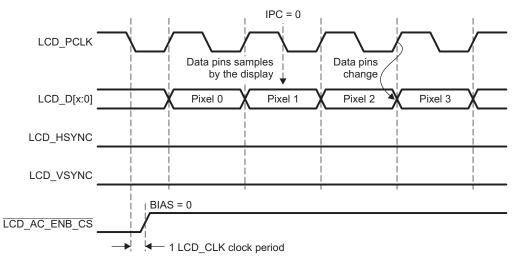

| 37              | 12-Bit STN Data in Frame Buffer                                                |          |

| 38              | 16-Bit STN Data in Frame Buffer                                                |          |

| 39              | 16-BPP STN Mode                                                                |          |

| 40              | LCD Raster Timing Register 0 (RASTER_TIMING_0)                                 |          |

| 41              | LCD Raster Timing Register 1 (RASTER_TIMING_1)                                 |          |

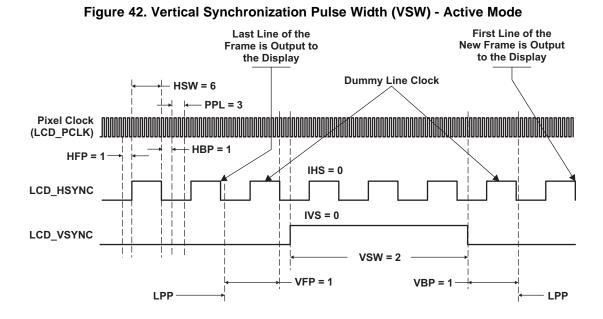

| 42              | Vertical Synchronization Pulse Width (VSW) - Active Mode                       |          |

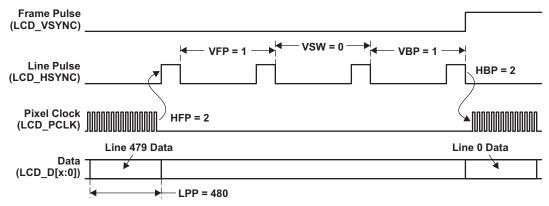

| 43              | Vertical Front Porch (VFP)                                                     |          |

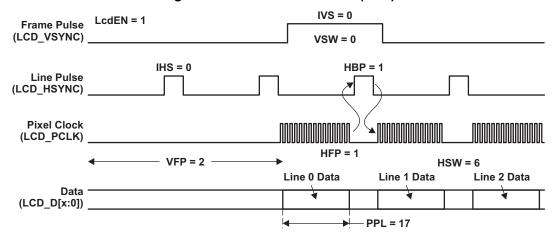

| 44              | Vertical Back Porch (VBP)                                                      |          |

| 45              | LCD Raster Timing Register 2 (RASTER_TIMING_2)                                 |          |

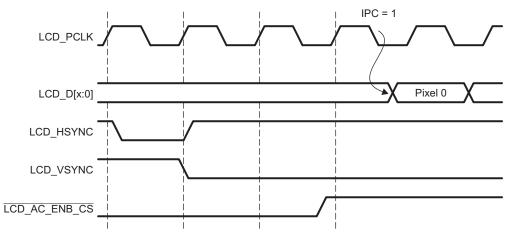

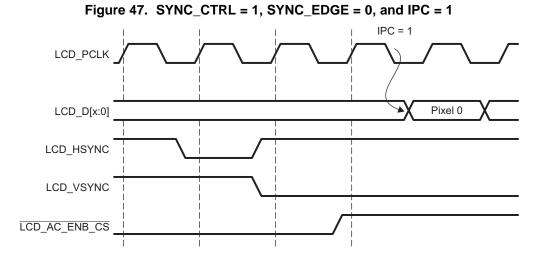

| 46              | SYNC_CTRL = 0, IPC = 1 in TFT Mode                                             |          |

| 47              | SYNC_CTRL = 1, SYNC_EDGE = 0, and IPC = 1                                      |          |

| 48              | LCD Raster Subpanel Display Register (RASTER_SUBPANEL)                         |          |

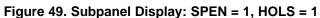

| 49              | Subpanel Display: SPEN = 1, HOLS = 1                                           |          |

| <del>-</del> 50 | Subpanel Display: SPEN = 1, HOLS = 0                                           |          |

| 51              | LCD DMA Control Register (LCDDMA_CTRL).                                        |          |

| 52              | LCD DMA Frame Buffer <i>n</i> Base Address Register (LCDDMA_FB <i>n</i> _BASE) |          |

|                 |                                                                                | <b>.</b> |

53

LCD DMA Frame Buffer *n* Ceiling Address Register (LCDDMA\_FB*n*\_CEILING) ......61

#### List of Tables

| 1   | LCD External I/O Signals                                                                                | 12 |

|-----|---------------------------------------------------------------------------------------------------------|----|

| 2   | Register Configuration for DMA Engine Programming                                                       | 13 |

| 3   | LIDD I/O Name Map                                                                                       | 15 |

| 4   | Operation Modes Supported by Raster Controller                                                          | 19 |

| 5   | Bits-Per-Pixel Encoding for Palette Entry 0 Buffer                                                      | 21 |

| 6   | Frame Buffer Size According to BPP                                                                      | 22 |

| 7   | Color/Grayscale Intensities and Modulation Rates                                                        | 26 |

| 8   | Number of Colors/Shades of Gray Available on Screen                                                     | 26 |

| 9   | LCD Controller (LCDC) Registers                                                                         | 31 |

| 10  | LCD Revision Identification Register (REVID) Field Descriptions                                         | 31 |

| 11  | LCD Control Register (LCD_CTRL) Field Descriptions                                                      | 32 |

| 12  | Pixel Clock Frequency Programming Limitations                                                           | 33 |

| 13  | LCD Status Register (LCD_STAT) Field Descriptions                                                       | 34 |

| 14  | LCD LIDD Control Register (LIDD_CTRL) Field Descriptions                                                | 36 |

| 15  | LCD LIDD CSn Configuration Register (LIDD_CSn_CONF) Field Descriptions                                  | 38 |

| 16  | LCD LIDD CSn Address Read/Write Register (LIDD_CSn_ADDR) Field Descriptions                             | 39 |

| 17  | LCD LIDD CSn Data Read/Write Register (LIDD_CSn_DATA) Field Descriptions                                | 40 |

| 18  | LCD Raster Control Register (RASTER_CTRL) Field Descriptions                                            | 41 |

| 19  | LCD Controller Data Pin Utilization for Mono/Color Passive/Active Panels                                | 43 |

| 20  | LCD Raster Timing Register 0 (RASTER_TIMING_0) Field Descriptions                                       | 48 |

| 21  | LCD Raster Timing Register 1 (RASTER_TIMING_1) Field Descriptions                                       | 50 |

| 22  | LCD Raster Timing Register 2 (RASTER_TIMING_2) Field Descriptions                                       | 54 |

| 23  | LCD Raster Subpanel Display Register (RASTER_SUBPANEL) Field Descriptions                               | 58 |

| 24  | LCD DMA Control Register (LCDDMA_CTRL) Field Descriptions                                               | 60 |

| 25  | LCD DMA Frame Buffer <i>n</i> Base Address Register (LCDDMA_FB <i>n</i> _BASE) Field Descriptions       | 61 |

| 26  | LCD DMA Frame Buffer <i>n</i> Ceiling Address Register (LCDDMA_FB <i>n</i> _CEILING) Field Descriptions | 61 |

| A-1 | Document Revision History                                                                               | 62 |

Preface SPRUFM0A–June 2009

#### About This Manual

This document describes the liquid crystal display controller (LCDC).

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320C674x Digital Signal Processors (DSPs) and OMAP-L1x Applications Processors. Copies of these documents are available on the Internet at <u>www.ti.com</u>. *Tip:* Enter the literature number in the search box provided at www.ti.com.

The current documentation that describes the DSP, related peripherals, and other technical collateral, is available in the C6000 DSP product folder at: <a href="http://www.ti.com/c6000">www.ti.com/c6000</a>.

<u>SPRUGM5</u> — TMS320C6742 DSP System Reference Guide. Describes the C6742 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

<u>SPRUGJ0</u> — *TMS320C6743 DSP System Reference Guide.* Describes the System-on-Chip (SoC) including the C6743 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

<u>SPRUFK4</u> — TMS320C6745/C6747 DSP System Reference Guide. Describes the System-on-Chip (SoC) including the C6745/C6747 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

SPRUGM6 — TMS320C6746 DSP System Reference Guide. Describes the C6746 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

SPRUGJ7 — TMS320C6748 DSP System Reference Guide. Describes the C6748 DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, and system configuration module.

<u>SPRUG84</u> — OMAP-L137 Applications Processor System Reference Guide. Describes the System-on-Chip (SoC) including the ARM subsystem, DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, ARM interrupt controller (AINTC), and system configuration module.

7

- SPRUGM7 OMAP-L138 Applications Processor System Reference Guide. Describes the System-on-Chip (SoC) including the ARM subsystem, DSP subsystem, system memory, device clocking, phase-locked loop controller (PLLC), power and sleep controller (PSC), power management, ARM interrupt controller (AINTC), and system configuration module.

- <u>SPRUFK9</u> *TMS320C674x/OMAP-L1x Processor Peripherals Overview Reference Guide.* Provides an overview and briefly describes the peripherals available on the TMS320C674x Digital Signal Processors (DSPs) and OMAP-L1x Applications Processors.

- <u>SPRUFK5</u> TMS320C674x DSP Megamodule Reference Guide. Describes the TMS320C674x digital signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access (IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth management, and the memory and cache.

- SPRUFE8 TMS320C674x DSP CPU and Instruction Set Reference Guide. Describes the CPU architecture, pipeline, instruction set, and interrupts for the TMS320C674x digital signal processors (DSPs). The C674x DSP is an enhancement of the C64x+ and C67x+ DSPs with added functionality and an expanded instruction set.

- SPRUG82 TMS320C674x DSP Cache User's Guide. Explains the fundamentals of memory caches and describes how the two-level cache-based internal memory architecture in the TMS320C674x digital signal processor (DSP) can be efficiently used in DSP applications. Shows how to maintain coherence with external memory, how to use DMA to reduce memory latencies, and how to optimize your code to improve cache efficiency. The internal memory architecture in the C674x DSP is organized in a two-level hierarchy consisting of a dedicated program cache (L1P) and a dedicated data cache (L1D) on the first level. Accesses by the CPU to the these first level caches can complete without CPU pipeline stalls. If the data requested by the CPU is not contained in cache, it is fetched from the next lower memory level, L2 or external memory.

## Liquid Crystal Display Controller (LCDC)

#### 1 Introduction

The liquid crystal display controller (LCDC) is capable of supporting an asynchronous (memory-mapped) LCD interface and a synchronous (raster-type) LCD interface.

#### 1.1 Purpose of the Peripheral

The LCD controller consists of two independent controllers, the Raster Controller and the LCD Interface Display Driver (LIDD) controller. Each controller operates independently from the other and only one of them is active at any given time.

- The Raster Controller handles the synchronous LCD interface. It provides timing and data for constant graphics refresh to a passive display. It supports a wide variety of monochrome and full-color display types and sizes by use of programmable timing controls, a built-in palette, and a gray-scale/serializer. Graphics data is processed and stored in frame buffers. A frame buffer is a contiguous memory block in the system. A built-in DMA engine supplies the graphics data to the Raster engine which, in turn, outputs to the external LCD device.

- The LIDD Controller supports the asynchronous LCD interface. It provides full-timing programmability of control signals (CS, WE, OE, ALE) and output data.

Figure 1 shows the LCD controller details. The raster and LIDD Controllers are responsible for generating the correct external timing. The DMA engine provides a constant flow of data from the frame buffer(s) to the external LCD panel via the Raster and LIDD Controllers. In addition, CPU access is provided to read and write registers.

The solid, thick lines in Figure 1 indicate the data path. The Raster Controller's data path is fairly complicated, for a thorough description of the Raster Controller data path, see Section 2.5.

Figure 1. LCD Controller

SPRUFM0A–June 2009 Submit Documentation Feedback

Texas Instruments

www.ti.com

Architecture

#### 1.2 Features

See your device-specific data manual to check the features supported by the LCD controller.

#### 1.3 Terminology Used in this Document

| Term                 | Meaning                                                                                                                          |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Passive (STN) device | Refers to the Super-Twisted Nematic (STN) display device.                                                                        |

| Active (TFT) device  | Refers to the Thin-Film Transistor (TFT) display device.                                                                         |

| BPP                  | Bits per pixel; that is, the number of bits used for each pixel. In some documentation, this is also referred to as color depth. |

| RGB                  | Red, Green, Blue                                                                                                                 |

| ALE                  | Address latch enable                                                                                                             |

| CS                   | Chip select                                                                                                                      |

| OE                   | Output enable                                                                                                                    |

| WE                   | Write enable                                                                                                                     |

#### 2 Architecture

#### 2.1 Clocking

This section details the various clocks and signals. Figure 2 shows input and output LCD controller clocks.

#### Figure 2. Input and Output Clocks

#### 2.1.1 Pixel Clock

The pixel clock (LCD\_PCLK) frequency is derived from LCD\_CLK, the reference clock to this LCD module (see Figure 2). The pixel clock is used by the LCD display to clock the pixel data into the line shift register.

$$LCD\_PCLK = \frac{LCD\_CLK}{CLKDIV}$$

where CLKDIV is a field in the LCD\_CTRL register and should not be 0 or 1.

- **Passive (STN) mode.** LCD\_PCLK only transitions when valid data is available for output. It does not transition when the horizontal clock is asserted or during wait state insertion.

- Active (TFT) mode. LCD\_PCLK continuously toggles as long as the Raster Controller is enabled.

#### 2.1.2 Horizontal Clock (LCD\_HSYNC)

LCD\_HSYNC toggles after all pixels in a horizontal line have been transmitted to the LCD and a programmable number of pixel clock wait states has elapsed both at the beginning and end of each line.

The RASTER\_TIMING\_0 register fully defines the behavior of this signal.

LCD\_HSYNC can be programmed to be synchronized with the rising or falling edge of LCD\_PCLK. The configuration field is bits 24 and 25 in the RASTER\_TIMING\_2 register.

Active (TFT) mode. The horizontal clock or the line clock is also used by TFT displays as the horizontal synchronization signal (LCD\_HSYNC).

The timings of the horizontal clock(line clock) pins are programmable to support:

- Delay insertion both at the beginning and end of each line

- Line clock polarity.

- Line clock pulse width, driven on rising or falling edge of pixel clock.

#### 2.1.3 Vertical Clock (LCD\_VSYNC)

LCD\_VSYNC toggles after all lines in a frame have been transmitted to the LCD and a programmable number of line clock cycles has elapsed both at the beginning and end of each frame.

The RASTER\_TIMING\_1 register fully defines the behavior of this signal.

LCD\_VSYNC can be programmed to be synchronized with the rising or falling edge of LCD\_PCLK. The configuration field is bits 24 and 25 in the RASTER\_TIMING\_2 register.

- **Passive (STN) mode.** The vertical clock; that is, the frame clock, toggles during the first line of the screen.

- Active (TFT) mode. The vertical clock, that is, the frame clock, is also used by TFT displays as the vertical synchronization signal (LCD\_VSYNC).

The timings of the vertical clock pins are programmable to support:

- Delay insertion both at the beginning and end of each frame

- Frame clock polarity

#### 2.1.4 LCD\_AC\_ENB\_CS

- **Passive (STN) mode.** To prevent a dc charge within the screen pixels, the power and ground supplies of the display are <u>periodically switched</u>. The Raster Controller signals the LCD to switch the polarity by toggling this pin (LCD\_AC\_ENB\_CS).

- Active (TFT) mode. This signal acts as an output enable (OE) signal. It is used to signal the external LCD that the data is valid on the data bus (LCD\_D[15:0]). (see Figure 24)

#### 2.2 LCD External I/O Signals

Table 1 shows the details of the LCD controller external signals.

| Signal        | Туре         | Description                                                                                                                                                                                                                                                                                                                                                             |

|---------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCD_VSYNC     | OUT          | Raster controller: Frame clock the LCD uses to signal the start of a new frame of pixels.<br>Also used by TFT displays as the vertical synchronization signal.                                                                                                                                                                                                          |

|               |              | LIDD character: Register select (RS) or address latch enable (ALE)                                                                                                                                                                                                                                                                                                      |

|               |              | LIDD graphics: Address bit 0 (A0) or command/data select (C/D)                                                                                                                                                                                                                                                                                                          |

| LCD_HSYNC     | OUT          | Raster controller: Line clock the LCD uses to signal the end of a line of pixels that transfers line data from the shift register to the screen and to increment the line pointer(s). Also used by TFT displays as the horizontal synchronization signal.                                                                                                               |

|               |              | LIDD character: not used.                                                                                                                                                                                                                                                                                                                                               |

|               |              | LIDD graphics:                                                                                                                                                                                                                                                                                                                                                          |

|               |              | <ul> <li>6800 mode = read or write enable</li> </ul>                                                                                                                                                                                                                                                                                                                    |

|               |              | <ul> <li>8080 mode = not write strobe</li> </ul>                                                                                                                                                                                                                                                                                                                        |

| LCD_PCLK      | OUT          | Raster controller: Pixel clock the LCD uses to clock the pixel data into the line shift register.<br>In passive mode, the pixel clock transitions only when valid data is available on the data<br>lines. In active mode, the pixel clock transitions continuously, and the ac-bias pin is used<br>as an output enable to signal when data is available on the LCD pin. |

|               |              | LIDD character: not used.                                                                                                                                                                                                                                                                                                                                               |

|               |              | LIDD graphics:<br>• 6800 mode = enable strobe                                                                                                                                                                                                                                                                                                                           |

|               |              | <ul> <li>8080 mode = not read strobe</li> </ul>                                                                                                                                                                                                                                                                                                                         |

| LCD_AC_ENB_CS | OUT          | Raster controller: ac-bias used to signal the LCD to switch the polarity of the power supplies to the row and column axis of the screen to counteract DC offset. Used in TFT mode as the output enable to signal when data is latched from the data pins using the pixel clock.                                                                                         |

|               |              | LIDD character: Primary enable strobe                                                                                                                                                                                                                                                                                                                                   |

|               |              | LIDD graphics: Chip select 0 (CS0)                                                                                                                                                                                                                                                                                                                                      |

| LCD_MCLK      | OUT          | Raster controller: not used.                                                                                                                                                                                                                                                                                                                                            |

|               |              | LIDD character: Secondary enable strobe                                                                                                                                                                                                                                                                                                                                 |

|               |              | LIDD graphics: Chip select 1 (CS1)                                                                                                                                                                                                                                                                                                                                      |

| LCD_D[15:0]   | Raster: OUT  | LCD data bus, providing a 4-, 8-, or 16-bit data path.                                                                                                                                                                                                                                                                                                                  |

|               | LIDD: OUT/IN | Raster controller: For monochrome displays, each signal represents a pixel; for passive color displays, groupings of three signals represent one pixel (red, green, and blue). LCD_D[3:0] is used for monochrome displays of 2, 4, and 8 BPP; LCD_D[7:0] is used for color STN displays and LCD_D[15:0] is used for active (TFT) mode.                                  |

|               |              | LIDD character: Read and write the command and data registers.                                                                                                                                                                                                                                                                                                          |

|               |              | LIDD graphics: Read and write the command and data registers.                                                                                                                                                                                                                                                                                                           |

#### 2.3 DMA Engine

The DMA engine provides the capability to output graphics data to constantly refresh LCDs, without burdening the CPU, via interrupts or a firmware timer. It operates on one or two frame buffers, which are set up during initialization. Using two frame buffers (ping-pong buffers) enables the simultaneous operation of outputting the current video frame to the external display and updating the next video frame. The ping-pong buffering approach is preferred in most applications.

When the Raster Controller is used, the DMA engine reads data from a frame buffer and writes it to the input FIFO (as shown in Figure 1). The Raster Controller requests data from the FIFO for frame refresh; as a result, the DMA's job is to ensure that the FIFO is always kept full.

When the LIDD Controller is used, the DMA engine accesses the LIDD Controller's address and/or data registers.

To program DMA engine, configure the following registers, as shown in Table 2.

| -                  |                                                                        |

|--------------------|------------------------------------------------------------------------|

| Register           | Configuration                                                          |

| LCDDMA_CTRL        | Configure DMA data format                                              |

| LCDDMA_FB0_BASE    | Configure frame buffer 0                                               |

| LCDDMA_FB0_CEILING |                                                                        |

| LCDDMA_FB1_BASE    | Configure frame buffer 1. (If only one frame buffer is used, these two |

| LCDDMA_FB1_CEILING | registers will not be used.)                                           |

#### Table 2. Register Configuration for DMA Engine Programming

In addition, the LIDD\_CTRL register (for LIDD Controller) or the RASTER\_CTRL register (for Raster Controller) should also be configured appropriately, along with all the timing registers.

To enable DMA transfers, the LIDD\_DMA\_EN bit (in the LIDD\_CTRL register) or the LCDEN bit (in the RASTER\_CTRL register) should be written with 1.

#### 2.3.1 Interrupts

Interrupts in this LCD module are related to DMA engine operation. Three registers are closely related to this subject:

- The LIDD\_CTRL and RASTER\_CTRL registers enable or disable each individual interrupt sources.

- The LCD\_STAT register collects all the interrupt status information.

#### 2.3.1.1 LIDD Mode

When operating in LIDD mode, the DMA engine generates one interrupt signal every time the specified frame buffer has been transferred completely.

- The DONE\_INT\_EN bit in the LIDD\_CTRL register specifies if the interrupt signal is delivered to the system interrupt controller, which in turn may or may not generate an interrupt to CPU.

- The EOF1, EOF0, and DONE bits in the LCD\_STAT register reflect the interrupt signal, regardless of being delivered to the system interrupt controller or not.

#### 2.3.1.2 Raster Mode

When operating in Raster mode, the DMA engine can generate the interrupts in the following scenarios:

Output FIFO under-run. This occurs when the DMA engine cannot keep up with the data rate consumed by the LCD (which is determined by the LCD\_PCLK.) This is likely due to a system memory throughput issue or an incorrect LCD\_PCLK setting. The FUF bit in LCD\_STAT is set when this error occurs. This bit is cleared by disabling the Raster Controller (i.e., clearing the LCDEN bit in RASTER\_CTRL). Architecture

- Frame synchronization lost. This error happens when the DMA engine attempts to read what it believes to be the first word of the video buffer but it cannot be recognized as such. This could be caused by an invalid frame buffer address or an invalid BPP value (for more details, see Section 2.5.2). The SYNC bit in the LCD\_STAT register is set when such an error is detected. This field is cleared by disabling the Raster Controller (clearing the LCDEN bit in the RASTER\_CTRL register).

- 3. **Palette loaded**. This interrupt can be generated when the palette is loaded into the memory by the DMA engine. At the same time, the PL bit in the LCD\_STAT register is set. In data-only (PLM = 2h) and palette-plus-data (PLM = 00) modes, writing 0 to this bit clears the interrupt. In the palette-only (PLM = 1) mode, this bit is cleared by disabling the Raster Controller (clearing the LCDEN bit in the RASTER\_CTRL register).

- 4. AC bias transition. If the ACB\_I bit in the RASTER\_TIMING\_2 register is programmed with a <u>non-zero value, an</u> internal counter will be loaded with this value and starts to decrement each time LCD\_AC\_ENB\_CS (AC-bias signal) switches its state. When the counter reaches zero, the ABC bit in the LCD\_STAT register is set, which will deliver an interrupt signal to the system interrupt controller (if the interrupt is enabled.) The counter reloads the value in field ACB\_I, but does not start to decrement until the ABC bit is cleared by writing 0 to this bit.

- 5. **Frame transfer completed**. When one frame of data is transferred completely, the DONE bit in the LCD\_STAT register is set. This bit is cleared by disabling the Raster Controller (i.e., clearing the LCDEN bit in the RASTER\_CTRL register). Note that the EOF0 and EOF1 bits in the LCD\_STAT register will be set accordingly.

Note that the interrupt enable bits are in the RASTER\_CTRL register. The corresponding enable bit must be set in order to generate an interrupt to the CPU. However, the LCD\_STAT register reflects the interrupt signal regardless of the interrupt enable bits settings.

#### 2.3.1.3 Interrupt Handling

Refer the device-specific data manual for information about LCD interrupt number to CPU. The interrupt service routine needs to determine the interrupt source by examining the LCD\_STAT register and clearing the interrupt properly.

#### 2.4 LIDD Controller

The LIDD Controller is designed to support LCD panels with a memory-mapped interface. The types of displays range from low-end character monochrome LCD panels to high-end TFT smart LCD panels.

LIDD mode (and the use of this logic) is enabled by clearing the MODESEL bit in the LCD control register (LCD\_CTRL).

LIDD Controller operation is summarized as follows:

- During initialization, the LCD LIDD CS0/CS1 configuration registers (LIDD\_CS0\_CONF and LIDD\_CS1\_CONF) are configured to match the requirements of the LCD panel being used.

- During normal operation, the CPU writes display data to the LCD data registers (LIDD\_CS0\_DATA and LIDD\_CS1\_DATA). The LIDD interface converts the CPU write into the proper signal transition sequence for the display, as programmed earlier. Note that the first CPU write should send the beginning address of the update to the LCD panel and the subsequent writes update data at display locations starting from the first address and continuing sequentially. Note that DMA may be used instead of CPU.

- The LIDD Controller is also capable of reading back status or data from the LCD panel, if the latter has this capability. This is set up and activated in a similar manner to the write function described above.

Note: If an LCD panel is not used, this interface can be used to control any MCU-like peripheral.

See your device-specific data manual to check the LIDD features supported by the LCD controller.

Table 3 describes how the signals are used to interface external LCD modules, which are configured by the LIDD\_CTRL register.

| Display Type                       | Interface<br>Type | Data<br>Bits | LIDD_CTRL<br>[2:0] | I/O Name      | Display I/O<br>Name | Comment                                   |

|------------------------------------|-------------------|--------------|--------------------|---------------|---------------------|-------------------------------------------|

| Character<br>Display               | HD44780<br>Type   | 4            | 100                | LCD_D[7:4]    | DATA[7:4]           | Data Bus (length defined by Instruction)  |

|                                    |                   |              |                    | LCD_PCLK      | E (or E0)           | Enable Strobe (first display)             |

|                                    |                   |              |                    | LCD_HSYNC     | R/W                 | Read/Write                                |

|                                    |                   |              |                    | LCD_VSYNC     | RS                  | Register Select (Data/not<br>Instruction) |

|                                    |                   |              |                    | LCD_MCLK      | E1                  | Enable Strobe (second display optional)   |

| Character<br>Display               | HD44780<br>Type   | 8            | 100                | LCD_D[7:0]    | DATA[7:0]           | Data Bus (length defined by Instruction)  |

|                                    |                   |              |                    | LCD_PCLK      | E (or E0)           | Enable Strobe (first display)             |

|                                    |                   |              |                    | LCD_HSYNC     | R/W                 | Read/Write                                |

|                                    |                   |              |                    | LCD_VSYNC     | RS                  | Register Select (Data/not<br>Instruction) |

|                                    |                   |              |                    | LCD_MCLK      | E1                  | Enable Strobe (second display optional)   |

| Micro Interface<br>Graphic Display | 6800<br>Family    | Up to<br>16  | 001                | LCD_D[7:0]    | DATA[7:0]           | Data Bus (16 bits always available)       |

|                                    |                   |              |                    | LCD_PCLK      | E                   | Enable Clock                              |

|                                    |                   |              |                    | LCD_HSYNC     | R/W                 | Read/Write                                |

|                                    |                   |              |                    | LCD_VSYNC     | A0                  | Address/Data Select                       |

|                                    |                   |              |                    | LCD_AC_ENB_CS | CS (or CS0)         | Chip Select (first display)               |

|                                    |                   |              |                    | LCD_MCLK      | CS1                 | Chip Select (second display optional)     |

|                                    |                   |              | 000                | LCD_MCLK      | None                | Synchronous Clock (optional)              |

| Micro Interface<br>Graphic Display | 8080<br>Family    | Up to<br>16  | 011                | LCD_D[7:0]    | DATA[7:0]           | Data Bus (16 bits always<br>available)    |

|                                    |                   |              |                    | LCD_PCLK      | RD                  | Read Strobe                               |

|                                    |                   |              |                    | LCD_HSYNC     | WR                  | Write Strobe                              |

|                                    |                   |              |                    | LCD_VSYNC     | A0                  | Address/Data Select                       |

|                                    |                   |              |                    | LCD_AC_ENB_CS | CS (or CS0)         | Chip Select (first display)               |

|                                    |                   |              |                    | LCD_MCLK      | CS1                 | Chip Select (second display optional)     |

|                                    |                   |              | 010                | LCD_MCLK      | None                | Synchronous Clock (optional)              |

Table 3. LIDD I/O Name Map

The timing parameters are defined by the LIDD\_CS0\_CONF and LIDD\_CS1\_CONF registers, which are described in Section 3.5.

The timing configuration is based on an internal reference clock, MCLK. MCLK is generated out of LCD\_CLK, which is determined by the CLKDIV bit in the CCD\_CTRL register.

$MCLK = LCD\_CLK \text{ when } CLKDIV = 0.$  $MCLK = \frac{LCD\_CLK}{CLKDIV} \text{ when } CLKDIV \neq 0.$

Architecture

www.ti.com

#### 2.4.1 LIDD Controller Timing

Е

Figure 6. LIDD Mode 6800 Read Timing Diagram

LCD\_PCLK

Architecture

#### 2.5 Raster Controller

Raster mode (and the use of this logic) is enabled by setting the MODESEL bit in the LCD control register (LCD\_CTRL). Table 4 shows the active external signals when this mode is active.

| Interface           | Data Bus<br>Width | Register Bits<br>RASTER_CTRL[9, 7, 1] | Signal Name   | Description                  |

|---------------------|-------------------|---------------------------------------|---------------|------------------------------|

| Passive (STN) Mono  | 4                 | 001                                   | LCD_D[3:0]    | Data bus                     |

| 4-bit               |                   |                                       | LCD_PCLK      | Pixel clock                  |

|                     |                   |                                       | LCD_HSYNC     | Horizontal clock(Line Clock) |

|                     |                   |                                       | LCD_VSYNC     | Vertical clock (Frame Clock) |

|                     |                   |                                       | LCD_AC_ENB_CS | AC Bias                      |

|                     |                   |                                       | LCD_MCLK      | Not used                     |

| Passive (STN) Mono  | 8                 | 101                                   | LCD_D[7:0]    | Data bus                     |

| 8-bit               |                   |                                       | LCD_PCLK      | Pixel clock                  |

|                     |                   |                                       | LCD_HSYNC     | Horizontal clock(Line Clock) |

|                     |                   |                                       | LCD_VSYNC     | Vertical clock (Frame Clock) |

|                     |                   |                                       | LCD_AC_ENB_CS | AC Bias                      |

|                     |                   |                                       | LCD_MCLK      | Not used                     |

| Passive (STN) Color | 8                 | 100                                   | LCD_D[7:0]    | Data bus                     |

|                     |                   |                                       | LCD_PCLK      | Pixel clock                  |

|                     |                   |                                       | LCD_HSYNC     | Horizontal clock(Line Clock) |

|                     |                   |                                       | LCD_VSYNC     | Vertical clock (Frame Clock) |

|                     |                   |                                       | LCD_AC_ENB_CS | AC Bias                      |

|                     |                   |                                       | LCD_MCLK      | Not used                     |

| Active (TFT) Color  | 16                | x10                                   | LCD_D[15:0]   | Data bus                     |

|                     |                   |                                       | LCD_PCLK      | Pixel clock                  |

|                     |                   |                                       | LCD_HSYNC     | Horizontal clock(Line Clock) |

|                     |                   |                                       | LCD_VSYNC     | Vertical clock (Frame Clock) |

|                     |                   |                                       | LCD_AC_ENB_CS | AC Bias                      |

|                     |                   |                                       | LCD_MCLK      | Not used                     |

#### 2.5.1 Logical Data Path

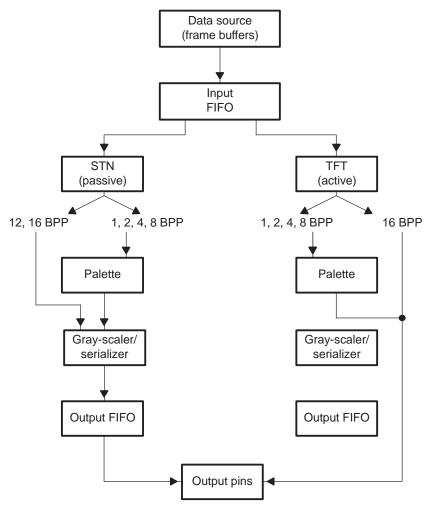

The block diagram of the Raster Controller is shown in Figure 1. Figure 11 illustrates its logical data path for various operation modes (passive (STN) versus active (TFT), various BPP size).

Figure 11 shows that:

- The gray-scaler/serializer and output FIFO blocks are bypassed in active (TFT) modes.

- The palette is bypassed in both 12- and 16-BPP modes.

Figure 11. Logical Data Path for Raster Controller

In summary:

- The display image is stored in frame buffers.

- The built-in DMA engine constantly transfers the data stored in the frame buffers to the Input FIFO.

- The Raster Controller relays data to the external pins according to the specified format.

The remainder of this section describes the functioning blocks in Figure 11, including frame buffers, palette, and gray-scaler/serializer. Their operation and programming techniques are covered in detail. The output format is also described in Section 2.5.5.

#### 2.5.2 Frame Buffer

A frame buffer is a contiguous memory block, storing enough data to fill a full LCD screen. It can be any memory in the system (external SDRAM or internal RAM). The data in the frame buffer consists of pixel values as well as a look-up palette. Figure 12 shows the frame buffer structure.

#### Figure 12. Frame Buffer Structure

#### 1, 2, 4, 12, 16 BPP Modes

| Palette  | Pixel Data |

|----------|------------|

| 32 bytes | x bytes    |

#### 8 BPP Mode

| Palette   | Pixel Data |

|-----------|------------|

| 512 bytes | x bytes    |

#### Notes:

- 8-BPP mode uses the first 512 bytes in the frame buffer as the palette while the other modes use 32 bytes.

- 12- and 16-BPP modes do not need a palette; i.e., the pixel data is the desired RGB value. However, the first 32 bytes are still considered a palette. The first entry should be 4000h (bit 14 is 1) while the remaining entries must be filled with 0. (For details, see Table 5.)

- Each entry in a palette occupies 2 bytes. As a result, 8-BPP mode palette has 256 color entries while the other palettes have up to 16 color entries.

- 4-BPP mode uses up the all the 16 entries in a palette.

- 1-BPP mode uses the first 2 entries in a palette while 2-BPP mode uses the first 4 entries. The remaining entries are not used and must be filled with 0.

- In 12- and 16-BPP modes, pixel data is RGB data. For all the other modes, pixel data is actually an index of the palette entry.

| Bit   | Name | Value | Description <sup>(1)(2)</sup>                                       |

|-------|------|-------|---------------------------------------------------------------------|

| 14-12 | BPP  |       | Bits-per-pixel.                                                     |

|       |      | 000   | 1 BPP                                                               |

|       |      | 001   | 2 BPP                                                               |

|       |      | 010   | 4 BPP                                                               |

|       |      | 011   | 8 BPP                                                               |

|       |      | 1xx   | 12 BPP in passive mode (TFT_STN = 0 and STN_565 = 0 in RASTER_CTRL) |

|       |      |       | 16 BPP in passive mode (TFT_STN = 0 and STN_565 = 1 in RASTER_CTRL) |

|       |      |       | 16 BPP in active mode (TFT_STN = 1 in RASTER_CTRL)                  |

#### Table 5. Bits-Per-Pixel Encoding for Palette Entry 0 Buffer

<sup>(1)</sup> Eight 1-bit pixels, four 2-bit pixels, and two 4-bit pixels are packed into each byte, and 12-bit pixels are right justified on (16-bit) word boundaries (in the same format as palette entry).

<sup>(2)</sup> For STN565, see the 16 BPP STN mode bit (Section 3.8.8).

The equations shown in Table 6 are used to calculate the total frame buffer size (in bytes) based on varying pixel size encoding and screen sizes.

| Table 6. Fram | e Buffer Size According to BPP           |

|---------------|------------------------------------------|

| BPP           | Frame Buffer Size                        |

| 1             | 32 + (Lines × Columns)/8                 |

| 2             | 32 + (Lines × Columns)/4                 |

| 4             | 32 + (Lines × Columns)/2                 |

| 8             | 512 + (Lines × Columns)                  |

| 12/16         | 32 + 2 $\times$ (Lines $\times$ Columns) |

|               |                                          |

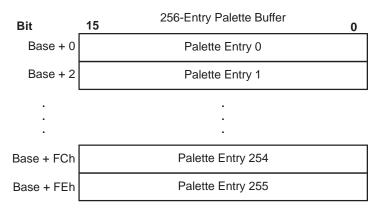

Figure 13 and Figure 14 show more detail of the palette entry organization.

|       | Individual Palette Entry |    |                    |    |    |         |   |   |           |          |   |   |          |   |   |   |

|-------|--------------------------|----|--------------------|----|----|---------|---|---|-----------|----------|---|---|----------|---|---|---|

| Bit   | 15                       | 14 | 13                 | 12 | 11 | 10      | 9 | 8 | 7         | 6        | 5 | 4 | 3        | 2 | 1 | 0 |

| Color | Unused                   |    | BPP <sup>(A)</sup> | )  |    | Red (R) |   |   | Green (G) |          |   |   | Blue (B) |   |   |   |

| Bit   | 15                       | 14 | 13                 | 12 | 11 | 10      | 9 | 8 | 7         | 6        | 5 | 4 | 3        | 2 | 1 | 0 |

| Mono  | Unused                   |    | BPP <sup>(A)</sup> | )  |    | Unused  |   |   |           | Mono (M) |   |   |          |   |   |   |

| Bit        | 15 | 16-Entry Palette Buffer <b>0</b> |   |

|------------|----|----------------------------------|---|

| Base + 0   |    | Palette Entry 0                  |   |

| Base + 2   |    | Palette Entry 1                  |   |

|            |    |                                  |   |

| •          |    |                                  |   |

| Base + 1Ch |    | Palette Entry 14                 | 7 |

| Base + 1Eh |    | Palette Entry 15                 |   |

A. Bits-per-pixels (BPP) is only contained within the first palette entry (palette entry 0).

|       |                          |    | - 3-               |    |    |         | <b>,</b> |   |           |     | (-    |   | ,        |   |   |   |

|-------|--------------------------|----|--------------------|----|----|---------|----------|---|-----------|-----|-------|---|----------|---|---|---|

|       | Individual Palette Entry |    |                    |    |    |         |          |   |           |     |       |   |          |   |   |   |

| Bi    | t 15                     | 14 | 13                 | 12 | 11 | 10      | 9        | 8 | 7         | 6   | 5     | 4 | 3        | 2 | 1 | 0 |

| Color | Unused                   |    | BPP <sup>(A)</sup> | )  |    | Red (R) |          |   | Green (G) |     |       |   | Blue (B) |   |   |   |

| Bi    | t 15                     | 14 | 13                 | 12 | 11 | 10      | 9        | 8 | 7         | 6   | 5     | 4 | 3        | 2 | 1 | 0 |

| Mono  | Unused                   |    | BPP <sup>(A)</sup> | )  |    | Unused  |          |   |           | Mon | o (M) |   |          |   |   |   |

A. Bits-per-pixels (BPP) is only contained within the first palette entry (palette entry 0).

Bits 12, 13, and 14 of the first palette entry select the number of bits-per-pixel to be used in the following frame and thus the number of palette RAM entries. The palette entry is used by the Raster Controller to correctly unpack pixel data.

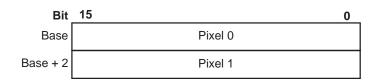

The following figures show the memory organization within the frame buffer for each pixel encoding size.

| Figure 15. 16-BPP Data Memory Organization (TFT Mode Only)—Little Endian |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|--------------------------------------------------------------------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit                                                                      | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 16 bits/pixel                                                            |    |    | R  |    |    |    |   | Ģ | 6 |   |   |   |   | В |   |   |

| SPRUFM0A-June 2009            |  |

|-------------------------------|--|

| Submit Documentation Feedback |  |

Unused [15-12] bits are filled with zeroes in TFT mode.

| Figure 18. | . 4-BPP Data | Memory | Organization |

|------------|--------------|--------|--------------|

|------------|--------------|--------|--------------|

| Bit          | 3 | 2    | 1      | 0 |

|--------------|---|------|--------|---|

| 4 bits/pixel |   | Data | a[3:0] |   |

| Bit      | 7       | 4 | 3 |         | 0 |

|----------|---------|---|---|---------|---|

| Base     | Pixel 0 |   |   | Pixel 1 |   |

| Base + 1 | Pixel 2 |   |   | Pixel 3 |   |

| Base + 2 | Pixel 4 |   |   | Pixel 5 |   |

| Bit      | 7       | 6    | 5       | 4    | 3    | 2     | 1        | 0 |  |

|----------|---------|------|---------|------|------|-------|----------|---|--|

| Base     | Pixel 0 |      | Pix     | el 1 | Pix  | el 2  | Pixel 3  |   |  |

| Base + 1 | Pixel 4 |      | Pix     | el 5 | Pix  | el 6  | Pixel 7  |   |  |

| Base + 2 | Pix     | el 8 | Pixel 9 |      | Pixe | el 10 | Pixel 11 |   |  |

#### Figure 19. 2-BPP Data Memory Organization

#### Figure 20. 1-BPP Data Memory Organization

| Bit      | 7  | 6  | 5   | 4   | 3   | 2   | 1   | 0   |

|----------|----|----|-----|-----|-----|-----|-----|-----|

| Base     | P0 | P1 | P2  | P3  | P4  | P5  | P6  | P7  |

| Base + 1 | P8 | P9 | P10 | P11 | P12 | P13 | P14 | P15 |

#### 2.5.3 Palette

As explained in the previous section, the pixel data is an index of palette entry (when palette is used). The number of colors supported is given by 2<sup>number of BPP</sup>. However, due to a limitation of the gray-scaler/serializer block, fewer grayscales or colors may be supported.

The PLM field (in RASTER\_CTRL) affects the palette loading:

- If PLM is 00b (palette-plus-data mode) or 01b (palette-only mode), the palette is loaded by the DMA engine at the very beginning, which is followed by the loading of pixel data.

- If PLM is 10b (data-only mode), the palette is not loaded. Instead, the DMA engine loads the pixel data immediately.

#### 2.5.4 Gray-Scaler/Serializer

#### 2.5.4.1 Passive (STN) Mode

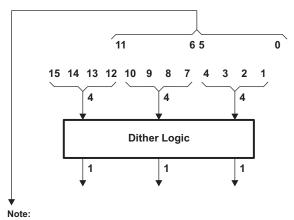

Once a palette entry is selected from the look-up palette by the pixel data, its content is sent to the gray-scaler/serializer. If it is monochrome data, it is encoded as 4 bits. If it is color data, it is encoded as 4 bits (Red), 4 bits (Green), and 4 bits (Blue).

These 4-bit values are used to select one of the 16 intensity levels, as shown in Table 7. A patented algorithm is used during this processing to provide an optimized intensity value that matches the eye's visual perception of color/gray gradations.

#### 2.5.4.2 Active (TFT) Mode

The gray-scaler/serializer is bypassed.

| Dither Value<br>(4-Bit Value from Palette) | Intensity<br>(0% is White) | Modulation Rate<br>(Ratio of ON to ON+OFF Pixels) |

|--------------------------------------------|----------------------------|---------------------------------------------------|

| 0000                                       | 0.0%                       | 0                                                 |

| 0001                                       | 11.1%                      | 1/9                                               |

| 0010                                       | 20.0%                      | 1/5                                               |

| 0011                                       | 26.7%                      | 4/15                                              |

| 0100                                       | 33.3%                      | 3/9                                               |

| 0101                                       | 40.0%                      | 2/5                                               |

| 0110                                       | 44.4%                      | 4/9                                               |

| 0111                                       | 50.0%                      | 1/2                                               |

| 1000                                       | 55.6%                      | 5/9                                               |

| 1001                                       | 60.0%                      | 3/5                                               |

| 1010                                       | 66.6%                      | 6/9                                               |

| 1011                                       | 73.3%                      | 11/15                                             |

| 1100                                       | 80.0%                      | 4/5                                               |

| 1101                                       | 88.9%                      | 8/9                                               |

| 1110                                       | 100.0%                     | 1                                                 |

| 1111                                       | 100.0%                     | 1                                                 |

#### 2.5.4.3 Summary of Color Depth

#### Table 8. Number of Colors/Shades of Gray Available on Screen

| Number of<br>BPP | Passive Mode                                                                                                 | Active Mode (TFT_STN = 1)                                |                                                           |  |

|------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|--|

|                  | Monochrome (MONO_COLOR = 1)                                                                                  | Color (MONO_COLOR = 0)                                   | Color Only (MONO_COLOR = 0)                               |  |

| 1                | 2 palette entries to select within<br>15 grayscales                                                          | 2 palette entries to select within 3375 possible colors  | 2 palette entries to select within 4096 possible colors   |  |

| 2                | 4 palette entries to select within 15 grayscales                                                             | 4 palette entries to select within 3375 possible colors  | 4 palette entries to select within 4096 possible colors   |  |

| 4                | 16 palette entries to select within 15 grayscales                                                            | 16 palette entries to select within 3375 possible colors | 16 palette entries to select within 4096 possible colors  |  |

| 8                | Not relevant since it would consist in 256 palette entries to select within 15 grayscales, but exists anyway | 256 palette entries to select 3375 possible colors       | 256 palette entries to select within 4096 possible colors |  |

| 12               | x                                                                                                            | 3375 possible colors                                     | 4096 possible colors                                      |  |

| 16               | x                                                                                                            | 3375 possible colors (STN_565 = 1)                       | Up to 65536 possible colors                               |  |

www.ti.com

#### 2.5.5 Output Format

#### 2.5.5.1 Passive (STN) Mode

As shown in Figure 11, the pixel data stored in frame buffers go through palette (if applicable) and gray-scaler/serializer before reaching the Output FIFO. As a result, it is likely that the data fed to the Output FIFO is numerically different from the data in the frame buffers. (However, they represent the same color or grayscale.)

The output FIFO formats the received data according to display modes (see Table 4). Figure 21 shows the actual data output on the external pins.

#### 2.5.5.2 Active (TFT) Mode

As shown in Figure 11, the gray-scaler/serializer and output FIFO are bypassed in active (TFT) mode. Namely, at each pixel clock, one pixel data (16 bits) is output to the external LCD.

Architecture

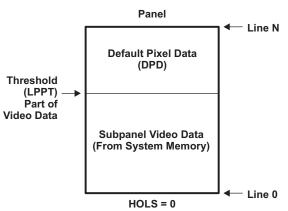

#### 2.5.6 Subpanel Feature

In some applications, it is desired to display only the first or last few lines of the LCD panel. This is mainly used for power saving.

This is supported by the Raster Controller via its subpanel feature. The RASTER\_SUBPANEL register fully defines its behavior, that is, the following parameters are defined:

- Whether the first or last few lines will be refreshed.

- A line number, which is the last (or first) line to be refreshed.

- The pixel data to be loaded to the refresh area.

Note that there is only one pixel value for all the pixels in the refresh area. As a result, frame buffers and DMA engine are not used in this case, which leads to power saving.

#### 2.5.7 Raster Controller Timing

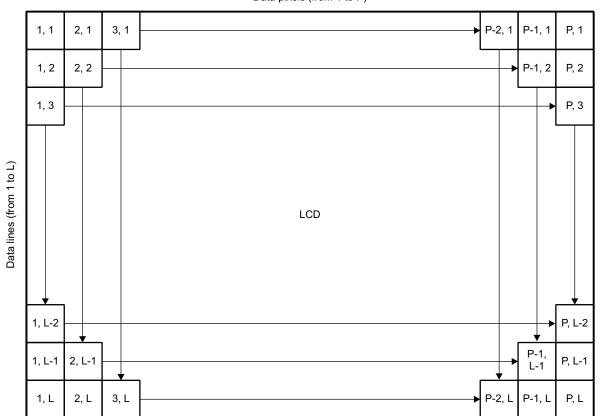

Figure 22. Raster Mode Display Format Data pixels (from 1 to P)

Architecture

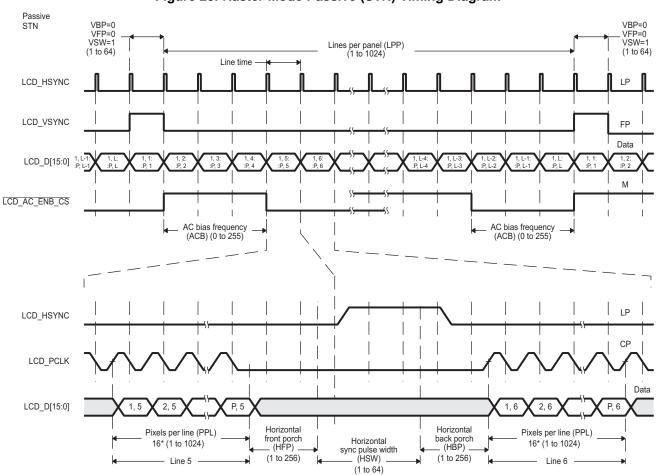

Figure 23. Raster Mode Passive (STN) Timing Diagram

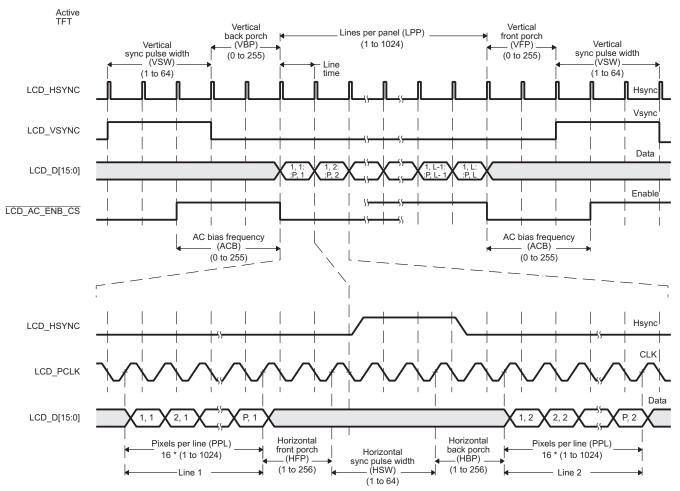

#### Figure 24. Raster Mode Active (TFT) Timing Diagram

#### 3 Registers

Table 9 lists the memory-mapped registers for the LCD module.

| Address |                    |                                                 |              |

|---------|--------------------|-------------------------------------------------|--------------|

| Offset  | Acronym            | Register Description                            | Section      |

| 0h      | REVID              | LCD Revision Identification Register            | Section 3.1  |

| 4h      | LCD_CTRL           | LCD Control Register                            | Section 3.2  |

| 8h      | LCD_STAT           | LCD Status Register                             | Section 3.3  |

| Ch      | LIDD_CTRL          | LCD LIDD Control Register                       | Section 3.4  |

| 10h     | LIDD_CS0_CONF      | LCD LIDD CS0 Configuration Register             | Section 3.5  |

| 14h     | LIDD_CS0_ADDR      | LCD LIDD CS0 Address Read/Write Register        | Section 3.6  |

| 18h     | LIDD_CS0_DATA      | LCD LIDD CS0 Data Read/Write Register           | Section 3.7  |

| 1Ch     | LIDD_CS1_CONF      | LCD LIDD CS1 Configuration Register             | Section 3.5  |

| 20h     | LIDD_CS1_ADDR      | LCD LIDD CS1 Address Read/Write Register        | Section 3.6  |

| 24h     | LIDD_CS1_DATA      | LCD LIDD CS1 Data Read/Write Register           | Section 3.7  |

| 28h     | RASTER_CTRL        | LCD Raster Control Register                     | Section 3.8  |

| 2Ch     | RASTER_TIMING_0    | LCD Raster Timing 0 Register                    | Section 3.9  |

| 30h     | RASTER_TIMING_1    | LCD Raster Timing 1 Register                    | Section 3.10 |

| 34h     | RASTER_TIMING_2    | LCD Raster Timing 2 Register                    | Section 3.11 |

| 38h     | RASTER_SUBPANEL    | LCD Raster Subpanel Display Register            | Section 3.12 |

| 40h     | LCDDMA_CTRL        | LCD DMA Control Register                        | Section 3.13 |

| 44h     | LCDDMA_FB0_BASE    | LCD DMA Frame Buffer 0 Base Address Register    | Section 3.14 |

| 48h     | LCDDMA_FB0_CEILING | LCD DMA Frame Buffer 0 Ceiling Address Register | Section 3.15 |

| 4Ch     | LCDDMA_FB1_BASE    | LCD DMA Frame Buffer 1 Base Address Register    | Section 3.14 |

| 50h     | LCDDMA_FB1_CEILING | LCD DMA Frame Buffer 1 Ceiling Address Register | Section 3.15 |

#### Table 9. LCD Controller (LCDC) Registers

#### 3.1 LCD Revision Identification Register (REVID)

The LCD revision identification register (REVID) is shown in Figure 25 and described in Table 10.

#### Figure 25. LCD Revision Identification Register (REVID)

| 31 | C            | ) |

|----|--------------|---|

|    | REV          |   |

|    | R-4C10 0100h |   |

LEGEND: R = Read only; -n = value after reset

#### Table 10. LCD Revision Identification Register (REVID) Field Descriptions

| Bit  | Field | Value      | Description                      |  |

|------|-------|------------|----------------------------------|--|

| 31-0 | REV   | 4C10 0100h | Peripheral Identification Number |  |

#### 3.2 LCD Control Register (LCD\_CTRL)

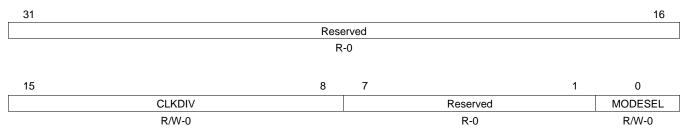

The LCD control register (LCD\_CTRL) contains the fundamental mode select bit for the LCD controller. The LCD\_CTRL is shown in Figure 26 and described in Table 11.

#### Figure 26. LCD Control Register (LCD\_CTRL)

LEGEND: R/W = Read/Write; R = Read only; -*n* = value after reset

#### Table 11. LCD Control Register (LCD\_CTRL) Field Descriptions

| Bit   | Field    | Value | Description                                                                                                                                                                                                                                                                                                                                                        |

|-------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-16 | Reserved | 0     | Reserved                                                                                                                                                                                                                                                                                                                                                           |

| 15-8  | CLKDIV   | 0-FFh | Clock Divisor. Value (from 0 to 255) is used to specify the frequency of the pixel clock (in Raster mode) or MCLK (in LIDD mode) based on the LCD_CLK frequency. Pixel clock frequency can range from LCD_CLK/2 to LCD_CLK/255 (CLKDIV = 0 or CLKDIV = 1 are not valid). MCLK can vary from LCD_CLK to LCD_CLK/255 (CLKDIV = 0 or CLKDIV = 1 sets MCLK = LCD_CLK). |

| 7-1   | Reserved | 0     | Reserved                                                                                                                                                                                                                                                                                                                                                           |

| 0     | MODESEL  |       | LCD Mode Select                                                                                                                                                                                                                                                                                                                                                    |

|       |          | 0     | LCD Controller in LIDD mode                                                                                                                                                                                                                                                                                                                                        |

|       |          | 1     | LCD Controller in Raster mode                                                                                                                                                                                                                                                                                                                                      |

The 8-bit clock divider (CLKDIV) field is used to select the frequency of the pixel clock. CLKDIV can generate a range of pixel clock frequencies from LCD\_CLK/2 to LCD\_CLK/255. The pixel clock frequency must be adjusted to meet the required screen refresh rate.

The refresh rate depends on:

- The number of pixels for the target display.

- Whether monochrome or color mode is selected.

- The number of pixel clock delays programmed at the beginning and end of each line.

- The number of line clocks inserted at the beginning and end of each frame.

- The width of the frame clock (LCD\_VSYNC) signal in active mode or VSW line clocks inserted in passive mode.

- The width of the line clock (LCD\_HSYNC) signal.

All of these factors alter the time duration from one frame transmission to the next. Different display manufacturers require different frame refresh rates, depending on the physical characteristics of the display. CLKDIV is used to alter the pixel clock frequency in order to meet these requirements. Pixel clock is used to synchronously signal the device to drive data to the LCD data pins, and to signal the output FIFO to latch the data from the pins. The frequency of the pixel clock for a set CLKDIV value or the required CLKDIV value to yield a target pixel clock frequency can be calculated using the following equation:

$\mathsf{LCD\_PCLK} = \frac{\mathsf{LCD\_CLK}}{\mathsf{CLKDIV}}$

The pixel clock frequency is programmed taking into account the limitations shown in Table 12.

If CLKDIV equals 0 or 1, the effect is undefined. Dividing the pixel clock frequency by an odd number distorts the duty cycle.

| Type of Screen                           | Output (In Bits) | Minimum Pixel Clock Divider |

|------------------------------------------|------------------|-----------------------------|

| TFT 1,2,4,8 BPP                          | 12 ( 1 pixel)    | 2                           |

| TFT 16 BPP                               | 16 (1 pixel)     | 2                           |

| STN monochrome(4 output lines per panel) | 4 (4 pixel)      | 4                           |

| STN monochrome(8 output lines per panel) | 8 (8 pixel)      | 8                           |

| STN color                                | 8 (2 2/3 pixel)  | 3                           |

#### Table 12. Pixel Clock Frequency Programming Limitations

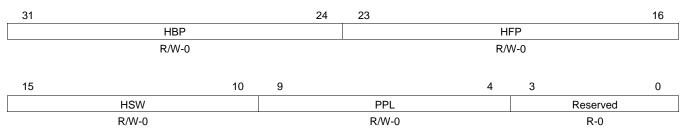

#### Registers