# OMAP5910/5912 Multimedia Processor DSP Subsystem Reference Guide

Literature Number: SPRU890A May 2005

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated

## Preface

# **Read This First**

### About This Manual

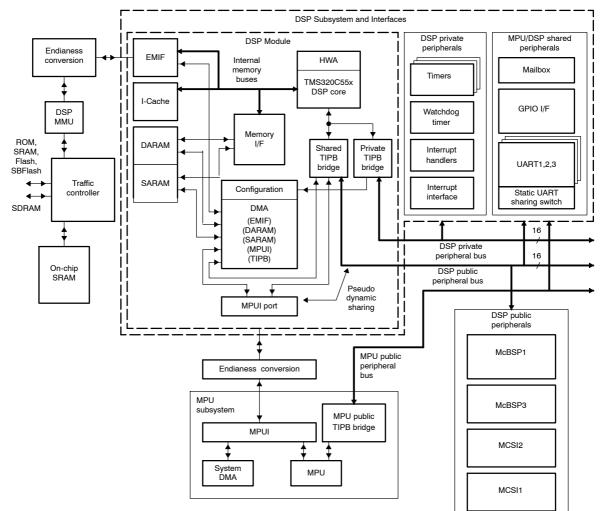

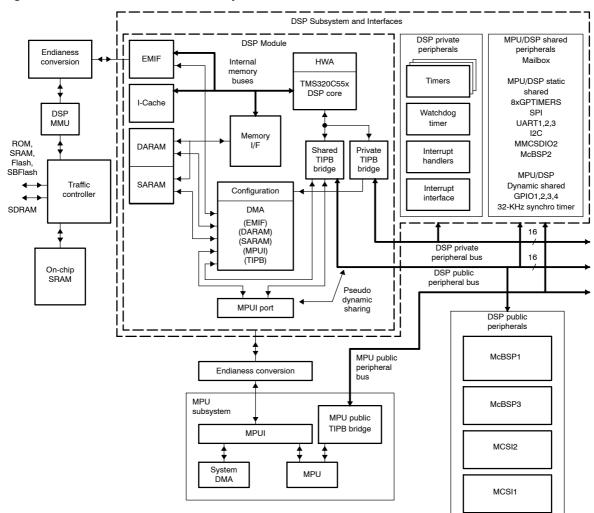

This document describes the OMAP5910/5912 multimedia processor DSP subsystem.

## Notational Conventions

This document uses the following conventions.

□ Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

## **Related Documentation From Texas Instruments**

Documentation that describes the OMAP5910/5912 devices, related peripherals, and other technical collateral, is available in the OMAP5910 Product Folder on TI's website: www.ti.com/omap5910, and in the OMAP5912 Product Folder on TI's website: www.ti.com/omap5912.

## Trademarks

OMAP and the OMAP symbol are trademarks of Texas Instruments.

3

4 DSP Subsystem

SPRU890A

# Contents

| 1 | <b>Digita</b><br>1.1<br>1.2<br>1.3<br>1.4 | Archite<br>Feature<br>Differe                                                                       | I Processor Subsystem Overview                                                                                                                                                                                                                                                                                           | 17<br>17<br>19                                     |

|---|-------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

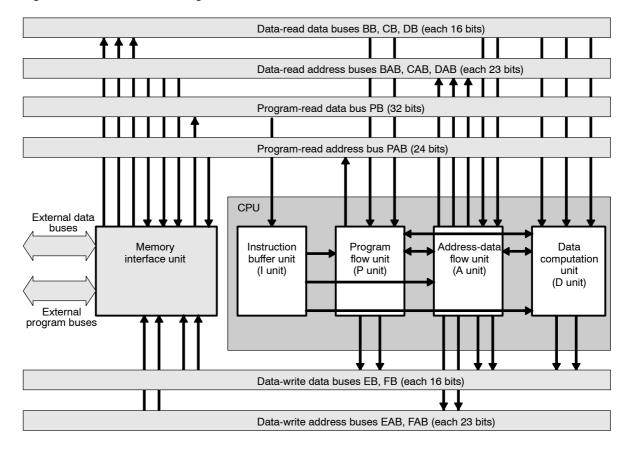

| 2 | <b>C55x</b><br>2.1<br>2.2<br>2.3          | DSP C<br>Introdu                                                                                    | ore Overview                                                                                                                                                                                                                                                                                                             | 21<br>22                                           |

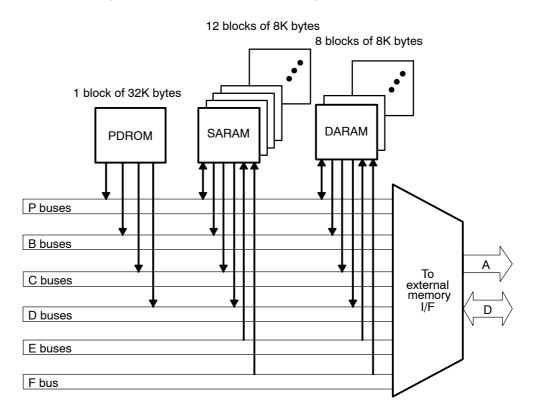

| 3 | <b>DSP</b><br>3.1<br>3.2<br>3.3<br>3.4    | Interna<br>DSP E<br>I/O Me                                                                          | t <b>em Memory</b><br>I Memory Space<br>xternal Memory Space<br>mory Space<br>y Maps                                                                                                                                                                                                                                     | 26<br>28<br>28                                     |

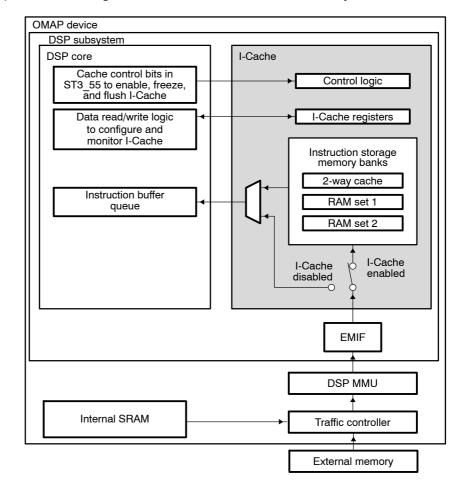

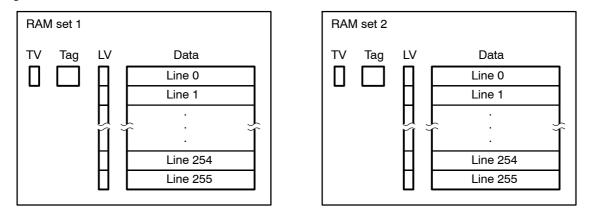

| 4 | Instru<br>4.1                             |                                                                                                     | ache<br>ction<br>Features<br>Functional Block Diagram<br>Supported Cache Configurations                                                                                                                                                                                                                                  | 30<br>30<br>30                                     |

|   | 4.2                                       | Instruct<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8<br>4.2.9<br>4.2.10 | tion Cache Architecture .<br>Introduction to the I-Cache .<br>Instruction Cache Blocks .<br>Instruction Cache Operation .<br>DSP Core Bits for Controlling the I-Cache .<br>Initialization .<br>Reset Considerations .<br>Clock Control .<br>Power Management .<br>Emulation Considerations .<br>Timing Considerations . | 32<br>32<br>35<br>39<br>41<br>41<br>41<br>42<br>42 |

|   | 4.3                                       |                                                                                                     | uring the I-Cache With the 2-Way Cache and No RAM Set Blocks         Architectural/Operational Description         Software Configuration         System Traffic Considerations                                                                                                                                          | 44<br>44<br>44                                     |

5

|   | 4.4   | Config         | uring the I-Cache With the 2-Way Cache and One RAM Set                      | 45 |

|---|-------|----------------|-----------------------------------------------------------------------------|----|

|   |       | 4.4.1          | Architectural/Operational Description                                       |    |

|   |       | 4.4.2          | Software Configuration                                                      |    |

|   |       | 4.4.3          | System Traffic Considerations                                               |    |

|   | 4.5   | Config         | uring the I-Cache With the 2-Way Cache and Two RAM Sets                     |    |

|   |       | 4.5.1          | Architectural/Operational Description                                       |    |

|   |       | 4.5.2          | Software Configuration                                                      |    |

|   |       | 4.5.3          | System Traffic Considerations                                               | 47 |

|   | 4.6   | Instruc        | tion Cache Registers                                                        | 48 |

|   |       | 4.6.1          | Overview                                                                    | 48 |

|   |       | 4.6.2          | I-Cache Global Control Register (GCR)                                       | 49 |

|   |       | 4.6.3          | I-Cache Line Flush Registers (FLR0, FLR1)                                   | 51 |

|   |       | 4.6.4          | I-Cache N-Way Control Register (NWCR)                                       | 52 |

|   |       | 4.6.5          | I-Cache RAM Set Control Registers (RCR1 and RCR2)                           | 53 |

|   |       | 4.6.6          | I-Cache RAM Set Tag Registers (RTR1 and RTR2)                               | 55 |

|   |       | 4.6.7          | I-Cache Status Register (ISR)                                               | 57 |

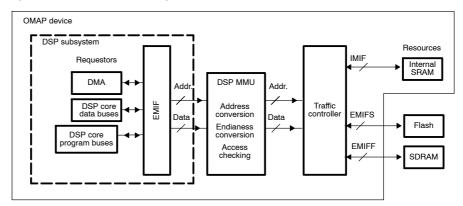

| 5 | ופסו  | Evtorno        | I Memory Interface                                                          | 50 |

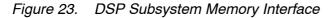

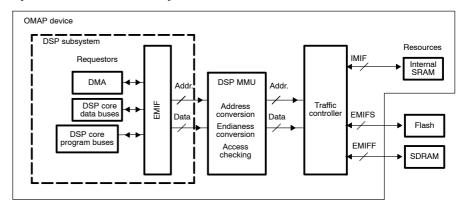

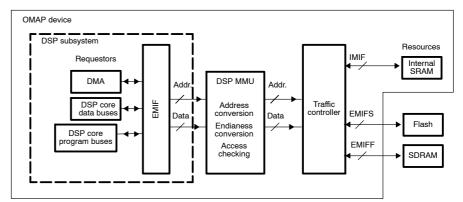

| 5 | 5.1   |                | ew                                                                          |    |

|   | 5.2   |                | eral Architecture                                                           |    |

|   | 5.2   | 5.2.1          |                                                                             |    |

|   |       | 5.2.1          | Memory Map                                                                  |    |

|   |       | 5.2.2          | DSP External Memory Accesses                                                |    |

|   |       | 5.2.3          | EMIF Requests                                                               |    |

|   |       | 5.2.4<br>5.2.5 | Write Posting: Buffering Write to DSP External Memory                       |    |

|   |       | 5.2.5          | Reset Considerations                                                        |    |

|   |       | 5.2.0<br>5.2.7 | Power Management                                                            |    |

|   | 5.3   |                | Registers                                                                   |    |

|   | 5.5   | 5.3.1          | Overview                                                                    |    |

|   |       | 5.3.1          |                                                                             |    |

|   |       | 5.3.2<br>5.3.3 | EMIF Global Control Register (GCR)         EMIF Global Reset Register (GRR) |    |

|   |       | 5.5.5          |                                                                             | 04 |

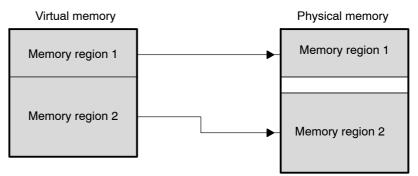

| 6 | DSP I | Memory         | Management Unit                                                             | 65 |

|   | 6.1   | Overvi         | ew                                                                          |    |

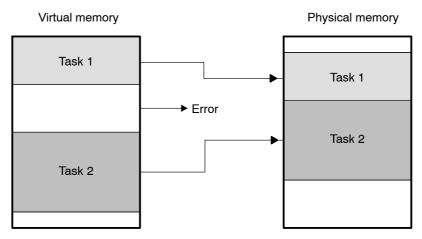

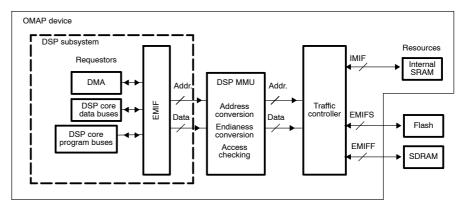

|   |       | 6.1.1          | Purpose of the MMU                                                          | 65 |

|   |       | 6.1.2          | Features                                                                    | 66 |

|   |       | 6.1.3          | Functional Block Diagram                                                    | 67 |

|   |       | 6.1.4          | Supported Usage of the DSP MMU                                              | 67 |

| 6.2 | MMU A   | rchitecture                                                      |

|-----|---------|------------------------------------------------------------------|

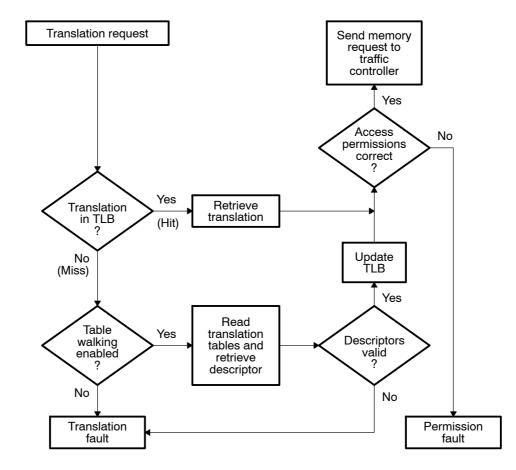

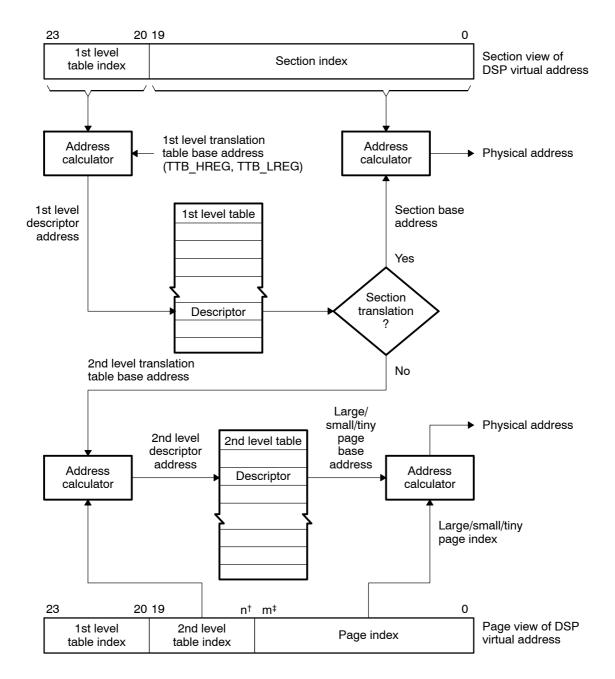

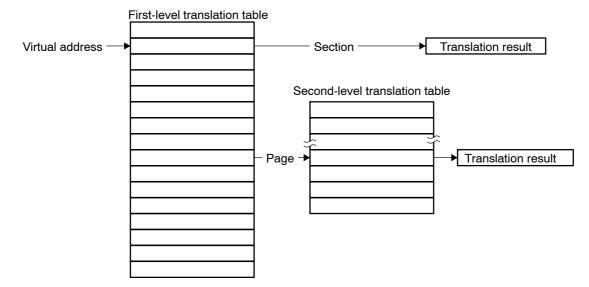

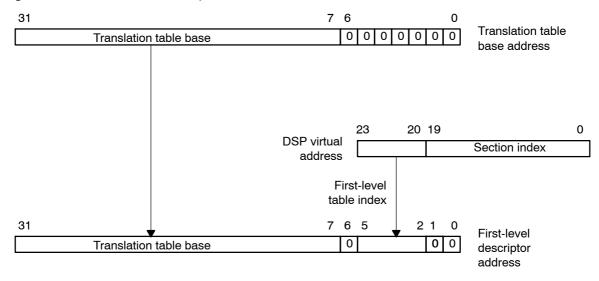

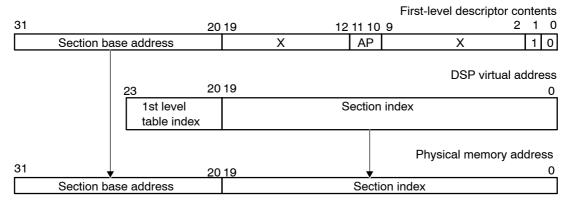

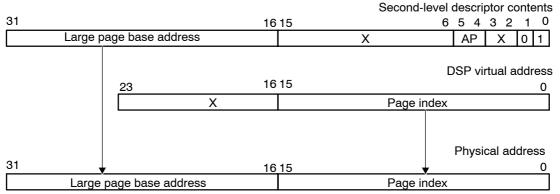

|     | 6.2.1   | Summary of Address Translation Process                           |

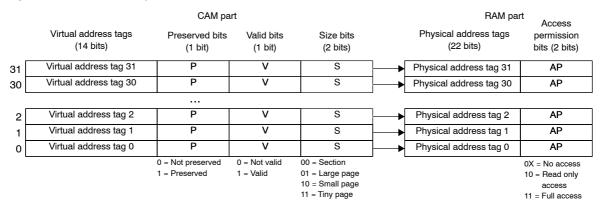

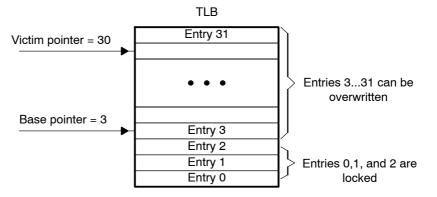

|     | 6.2.2   | Translation Look-Aside Buffer (TLB) 69                           |

|     | 6.2.3   | Table Walking Logic    79                                        |

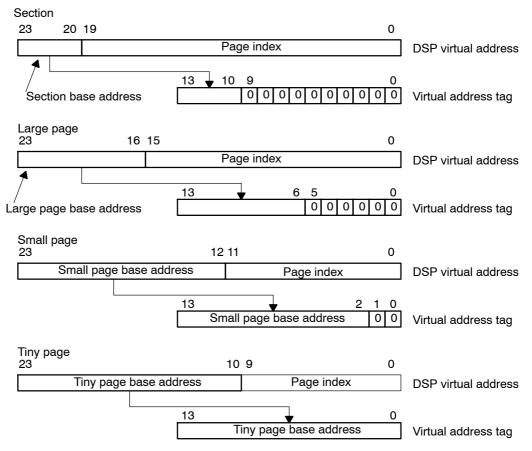

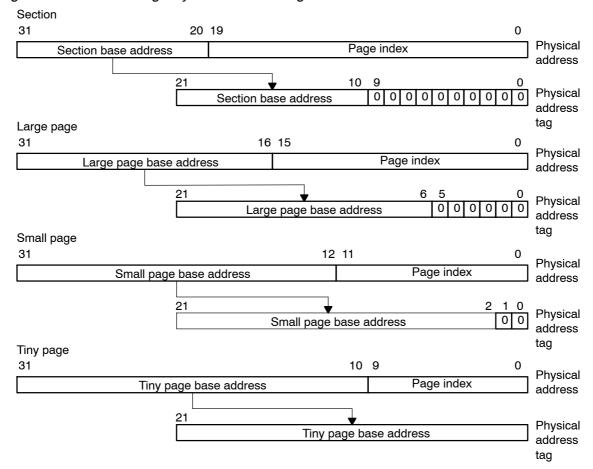

|     | 6.2.4   | Memory Address Translation                                       |

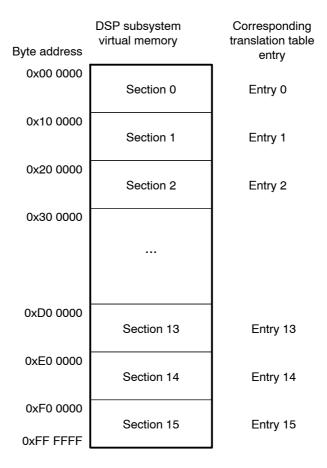

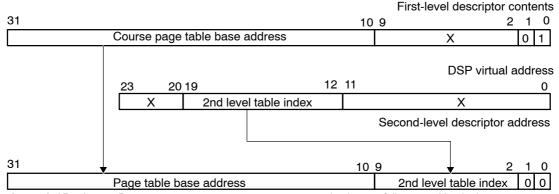

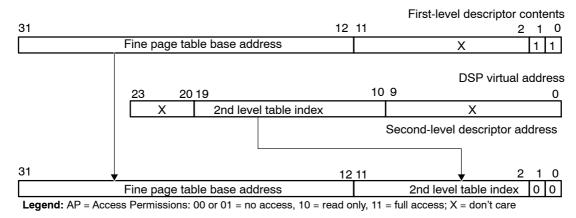

|     | 6.2.5   | First-Level Translation Table                                    |

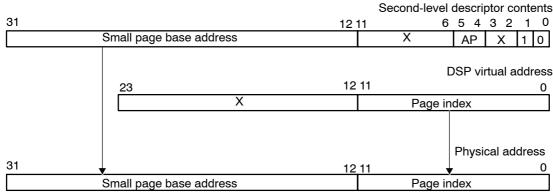

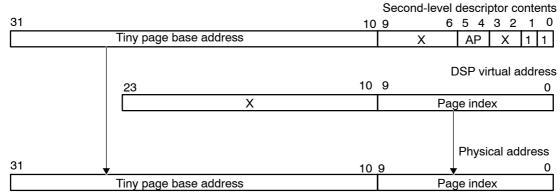

|     | 6.2.6   | Second-Level Translation Tables                                  |

|     | 6.2.7   | MMU Error Handling                                               |

|     | 6.2.8   | Reset Considerations                                             |

|     | 6.2.9   | Clock Control                                                    |

|     | 6.2.10  | Initialization                                                   |

|     | 6.2.11  | Interrupt Support                                                |

|     | 6.2.12  | Power Management                                                 |

| 6.3 | Using t | he MPU to Manage the TLB                                         |

|     | 6.3.1   | Architectural/Operational Description                            |

|     | 6.3.2   | Software Configuration                                           |

|     | 6.3.3   | System Traffic Considerations                                    |

| 6.4 | Using T | able Walking Logic to Manage the TLB                             |

|     | 6.4.1   | Architectural/Operational Description                            |

|     | 6.4.2   | Software Configuration                                           |

|     | 6.4.3   | System Traffic Considerations 100                                |

| 6.5 | DSP M   |                                                                  |

|     | 6.5.1   | Overview                                                         |

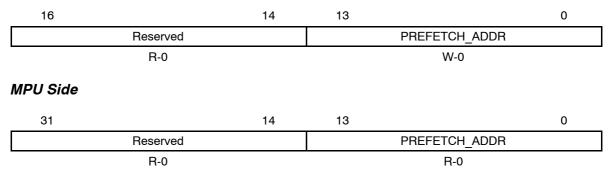

|     | 6.5.2   | MMU Pre-Fetch Register (PREFETCH_REG) 102                        |

|     |         | DSP Side                                                         |

|     |         | MPU Side                                                         |

|     | 6.5.3   | MMU Pre-Fetch Status Register (WALKING_ST_REG) 103               |

|     | 6.5.4   | MMU Control Register (CNTL REG) 104                              |

|     | 6.5.5   | MMU Fault Address Registers (FAULT_AD_H_REG, FAULT_AD_L_REG) 105 |

|     | 6.5.6   | MMU Fault Status Register (FAULT ST REG)                         |

|     | 6.5.7   | MMU Interrupt Acknowledge Register (IT ACK REG) 108              |

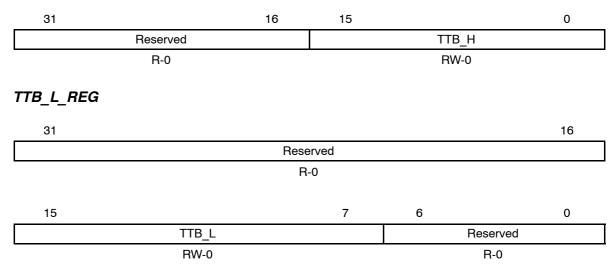

|     | 6.5.8   | MMU Translation Table Registers (TTB H REG, TTB L REG) 109       |

|     | 6.5.9   | MMU Lock/Protect Entry Register (LOCK REG) 110                   |

|     | 6.5.10  | MMU Read/Write TLB Entry Register (LD TLB REG) 111               |

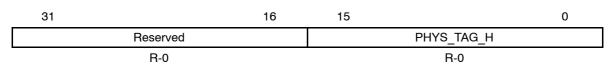

|     | 6.5.11  | MMU CAM Entry Registers (CAM_H_REG, CAM_L_REG) 112               |

|     | 6.5.12  | MMU RAM Entry Registers (RAM_H_REG, RAM_L_REG) 114               |

|     | 6.5.13  | MMU TLB Global Flush Register (GFLUSH REG)                       |

|     |         | MMU TLB Entry Flush Register (FLUSH ENTRY REG)                   |

|     |         | MMU Read CAM Entry Registers                                     |

|     |         | (READ_CAM_H_REG, READ_CAM_L_REG)                                 |

|     | 6.5.16  | MMU Read RAM Entry Registers                                     |

|     |         | (READ_RAM_H_REG, READ_RAM_L_REG) 119                             |

|     | 6.5.17  | MMU Idle Control Register (DSPMMU_IDLE_CTRL) 120                 |

|     |         |                                                                  |

DSP Subsystem 7

| 7 | DSP [ | ОМА     |                                                                          | 121 |

|---|-------|---------|--------------------------------------------------------------------------|-----|

|   | 7.1   | Overvie | ew                                                                       | 121 |

|   |       | 7.1.1   | Purpose of the DSP DMA                                                   | 121 |

|   |       | 7.1.2   | Features                                                                 | 121 |

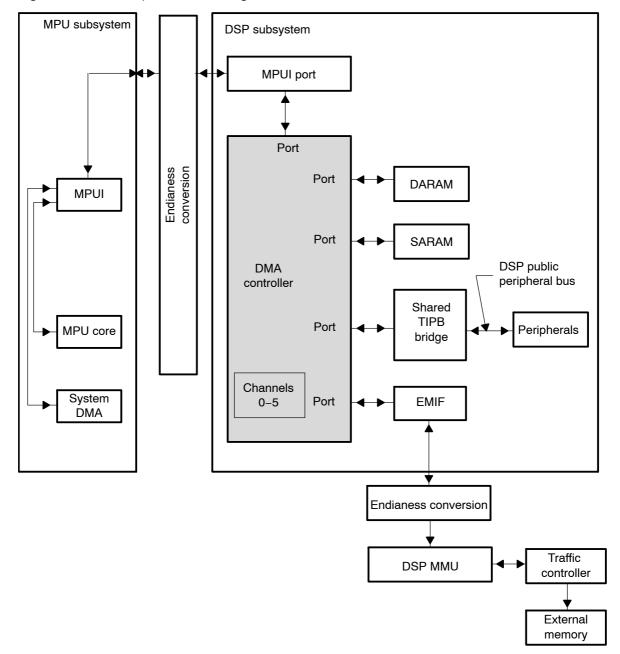

|   |       | 7.1.3   | Block Diagram of the DMA Controller                                      | 122 |

|   | 7.2   | DSP DI  | MA Controller Architecture                                               |     |

|   |       | 7.2.1   | Clock Control                                                            | 124 |

|   |       | 7.2.2   | Memory Map                                                               | 124 |

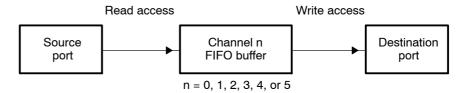

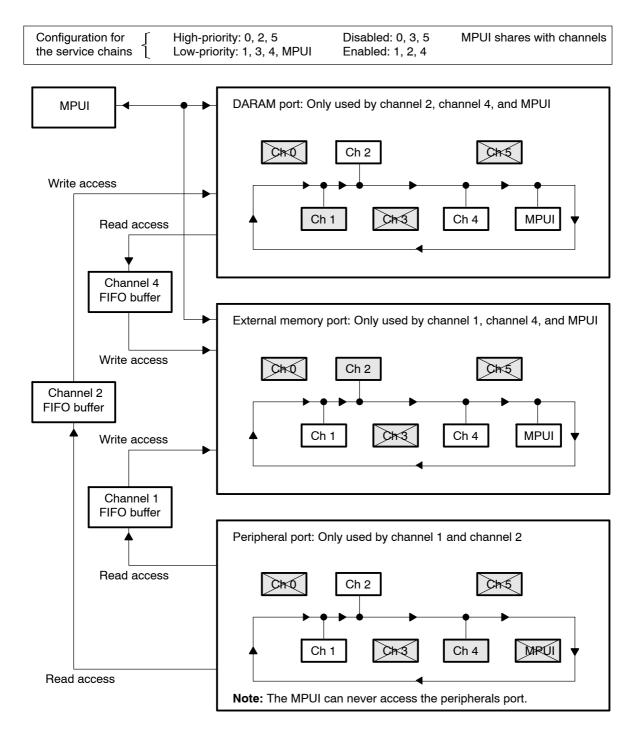

|   |       | 7.2.3   | Channels and Port Accesses                                               | 125 |

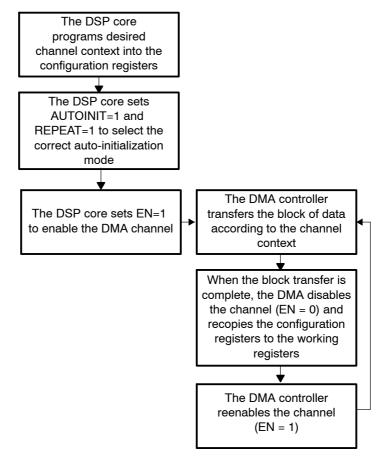

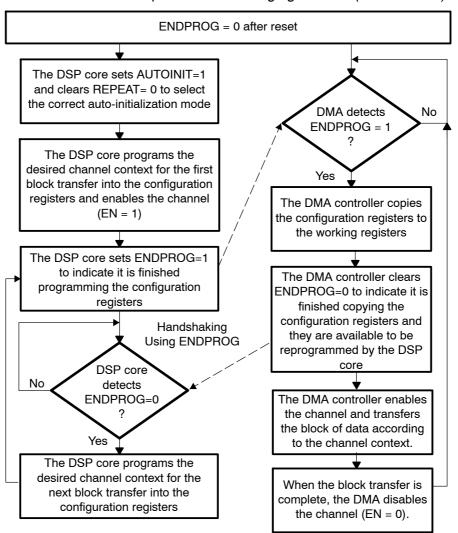

|   |       | 7.2.4   | Channel Auto-Initialization Capability                                   | 127 |

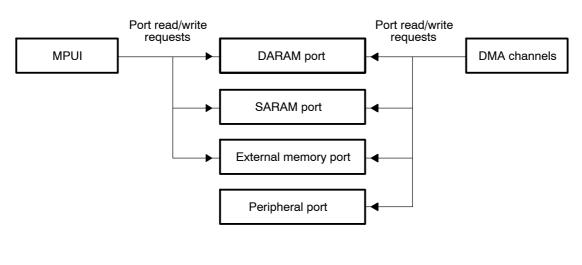

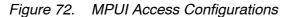

|   |       | 7.2.5   | MPUI Access Configurations                                               | 131 |

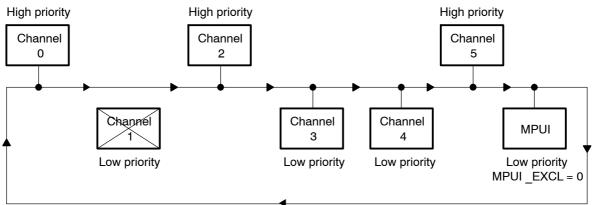

|   |       | 7.2.6   | Service Chain                                                            | 132 |

|   |       | 7.2.7   | Units of Data: Byte, Element, Frame, and Block                           | 137 |

|   |       | 7.2.8   | Start Address in a Channel                                               | 137 |

|   |       | 7.2.9   | Updating Addresses in a Channel                                          | 139 |

|   |       | 7.2.10  | Data Packing Capability                                                  | 139 |

|   |       | 7.2.11  | Data Burst Capability                                                    | 141 |

|   |       | 7.2.12  | Synchronizing Channel Activity                                           | 142 |

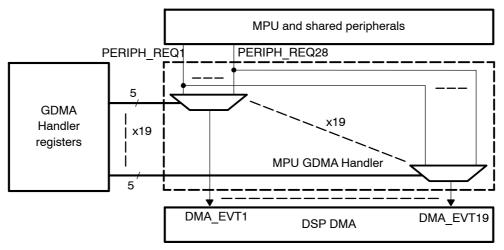

|   |       | 7.2.13  | DSP GDMA Handler (OMAP5912 Only)                                         | 146 |

|   |       |         | Functional Multiplexing DSP DMA Register A<br>(FUNC_MUX_DSP_DMA_A)       | 149 |

|   |       |         | Functional Multiplexing DSP DMA Register B<br>(FUNC_MUX_DSP_DMA_B)       | 151 |

|   |       |         | Functional Multiplexing DSP DMA Register C<br>(FUNC_MUX_DSP_DMA_C)       | 152 |

|   |       |         | Functional Multiplexing DSP DMA Register D<br>(FUNC_MUX_DSP_DMA_D)       | 154 |

|   |       | 7.2.14  | Reset Considerations                                                     | 154 |

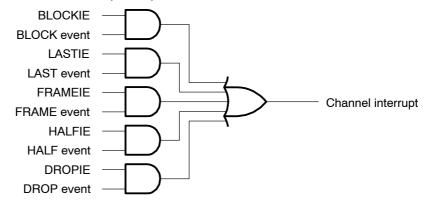

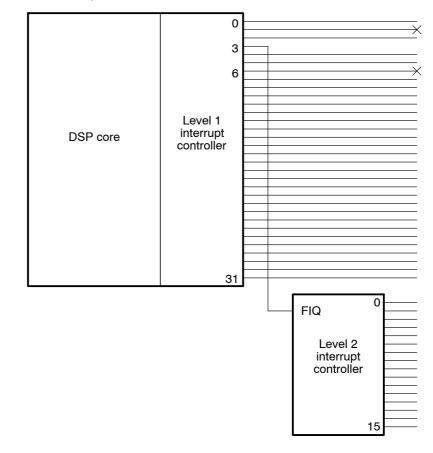

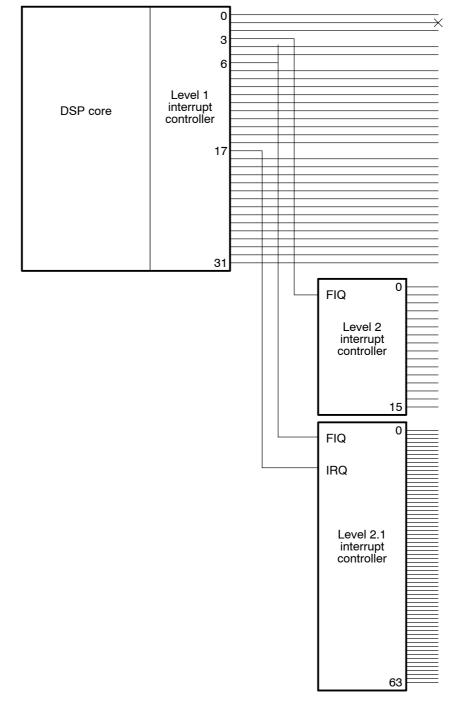

|   |       | 7.2.15  | Interrupt Support                                                        | 155 |

|   |       | 7.2.16  | Power Management                                                         | 158 |

|   |       | 7.2.17  | Emulation Considerations                                                 | 158 |

|   |       | 7.2.18  | Latency in DMA Transfers                                                 | 159 |

|   | 7.3   | DSP DI  | MA Controller Registers                                                  |     |

|   |       | 7.3.1   | Overview                                                                 |     |

|   |       | 7.3.2   | DMA Global Control Register (DMAGCR)                                     | 161 |

|   |       | 7.3.3   | DMA Global Software Compatibility Register (DMAGSCR)                     | 162 |

|   |       | 7.3.4   | DMA Global Timeout Control Register (DMAGTCR)                            |     |

|   |       | 7.3.5   | DMA Channel Control Register (DMACCR)                                    | 164 |

|   |       | 7.3.6   | DMA Interrupt Control Register (DMACICR) and Status<br>Register (DMACSR) | 170 |

|   |       | 7.3.7   | DMA Source and Destination Parameters Register (DMACSDP)                 | 174 |

|   |       | 7.3.8   | DMA Source Start Address Registers (DMACSSAU and DMACSSAL)               | 179 |

|   |       | 7.3.9   | DMA Destination Start Address Registers (DMACDSAU and DMACDSAL)          | 180 |

8

SPRU890A

|    |                                                  | 7.3.10                                                                                                                          | DMA Element Number Register (DMACEN) and Frame Number Register (DMACFN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 181 |

|----|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    |                                                  | 7.3.11                                                                                                                          | DMA Element Index Registers (DMACSEI, DMACDEI) and Frame<br>Index Registers (DMACSFI, DMACDFI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|    |                                                  | 7.3.12                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 8  | TI Pe                                            | ripheral                                                                                                                        | Bus Bridges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|    | 8.1                                              | -                                                                                                                               | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|    | 8.2                                              |                                                                                                                                 | rivate Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|    | 8.3                                              |                                                                                                                                 | ublic Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|    | 8.4                                              |                                                                                                                                 | IPU Shared Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|    | 8.5                                              |                                                                                                                                 | eral Access Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|    | 8.6                                              | •                                                                                                                               | eral Access Timeout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|    | 8.7                                              | •                                                                                                                               | Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|    |                                                  | 8.7.1                                                                                                                           | Överview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|    |                                                  | 8.7.2                                                                                                                           | TIPB Control Mode Register (CMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|    |                                                  |                                                                                                                                 | DSP Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|    |                                                  |                                                                                                                                 | MPU Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|    |                                                  |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 9  | MPU                                              | Interfac                                                                                                                        | e Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 9  | <b>MPU</b><br>9.1                                |                                                                                                                                 | e Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 9  |                                                  | Introdu                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 9  | 9.1                                              | Introdu                                                                                                                         | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 9  | 9.1                                              | Introdu<br>MPUI a                                                                                                               | ctionand MPUI Port Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| -  | 9.1<br>9.2                                       | Introdu<br>MPUI a<br>9.2.1<br>9.2.2                                                                                             | and MPUI Port Overview<br>MPUI Port Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| -  | 9.1<br>9.2                                       | Introdu<br>MPUI a<br>9.2.1<br>9.2.2<br><b>Subsys</b> t                                                                          | and MPUI Port Overview<br>MPUI Port Modes<br>HOM/SAM Change Outside of Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| -  | 9.1<br>9.2<br><b>DSP</b>                         | Introdu<br>MPUI a<br>9.2.1<br>9.2.2<br><b>Subsys</b> t<br>Endian                                                                | and MPUI Port Overview<br>MPUI Port Modes<br>HOM/SAM Change Outside of Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |