## AdvancedTCA\* Modular Communications Platform Design Guide

**Guidelines for Modular Communications Platform Building-Block and System Interoperability**

Version 2.0 Release 1.0 October 29, 2004

THIS SPECIFICATION DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. The Authors (as described below) disclaim all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein, except that a license is hereby granted to copy and reproduce this specification document for internal use only.

Intel, Intel logo, PENTIUM, Intel® IXA are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. Motorola and Motorola logo are the trademarks or registered trademarks of Motorola Inc. Siemens and Siemens logo are the trademarks or registered trademarks of Siemens AG. HP and HP logo are the trademarks or registered trademarks of Hewlett Packard Development Company Continuous Computing and Continuous Computing logo are the trademarks or registered trademarks of Continuous Computing Corporation. Kontron and Kontron logo are the trademarks or registered trademarks of Kontron GmbH. DTI and DTI logo are the trademarks or registered trademarks of Diversified Technologies Inc.; CG Mupac and CG Mupac logo are the trademarks or registered trademarks of Carlo Gavazzi Mupac Inc. Radisys and Radisys logo are the trademarks or registered trademarks of Radisys Corporation. Schroff and Schroff logo are the trademarks or registered trademarks of Schroff Development Corporation. ELMA and ELMA logo are the trademarks or registered trademarks of ELMA Electronics Inc. Pigeon Point Systems and Pigeon Point Systems logo are the trademarks or registered trademarks of Pigeon Point Systems Corporation, Mellanox Technologies and Mellanox Technologies logo are the trademarks or registered trademarks of Mellanox Technologies. Inc. Performance Tech and Performance Tech logo are the trademarks or registered trademarks of Performance Tech Inc. Marconi and Marconi logo are the trademarks or registered trademarks of Marconi Corporation plc. IP Fabrics and IP Fabrics logo are the trademarks or registered trademarks of IP Fabrics Corporation. ADLink and ADLink logo are the trademarks or registered trademarks of ADLink Corporation. SBS Technologies and SBS Technologies logo are the trademarks or registered trademarks of SBS Technologies Inc. OSA Technologies and OSA Technologies logo are the trademarks or registered trademarks of OSA Technologies Corporation. Littelfuse and Littelfuse logo are the trademarks or registered trademarks of Littelfuse Inc. Advantech and Advantech logo are the trademarks or registered trademarks of Advantech Company Ltd. PICMG and the PICMG logo and AdvancedTCA and the AdvancedTCA logo are the registered trademarks of the PCI Industrial Computers Manufacturers Group. ATCA is a trademark of the PCI Industrial Computers Manufacturers Group.

\* Other names and brands may be claimed as the property of others.

Copyright © 2004 Intel Corporation; PCI Industrial Computer Manufacturers Group; Marconi Corporation plc; PUTIAN, China; EMC, Corporation; Hewlett Packard Development Company; Siemens AG; Continuous Computing Corporation; Pigeon Point Systems Corporation; Performance Tech. Inc.; IP Fabrics Corporation; ADLink Corporation; SBS Technologies, Inc.; OSA Technologies, Inc.; Littelfuse, Inc.; Huawei Technologies Co., Ltd; LANGCHAO Group; ThinkEngine Networks, Inc.; Carlo Gavazzi Mupac, Inc.; Motorola, Inc; Rittal Corporation; ELMA Electronic, Inc.; Force Computers, Inc.; RadiSys Corporation; Mellanox Technologies; Kontron AG; Schroff GmbH; Diversified Technologies, Inc.; Advantech Co., Ltd.; RedSwitch, Inc. (collectively, the "Authors"). All rights reserved.

## **Contents**

| 1 | INTRODUCTION                                     | 13 |

|---|--------------------------------------------------|----|

|   | 1.1 Audience for this Guide                      | 13 |

|   | 1.2 Purpose of this Guide                        | 13 |

|   | 1.3 Sections of this Guide                       | 14 |

|   | 1.4 Guideline Compliance                         | 15 |

|   | 1.4.1 Required Compliance                        | 15 |

|   | 1.4.2 Recommended Compliance                     | 16 |

|   | 1.4.3 Optional Compliance                        |    |

|   | 1.4.4 Tables of Requirements                     | 16 |

|   | 1.5 Terminology use                              | 16 |

| 2 | MODULAR COMMUNICATIONS PLATFORM ARCHITECTURE     | 17 |

|   | 2.1 Architecture Overview                        |    |

|   | 2.1.1 Server                                     |    |

|   | 2.1.2 Switch                                     |    |

|   | 2.1.3 Interconnect                               |    |

|   | 2.1.4 Physical Configuration                     | 19 |

|   | 2.2 Server Architecture                          |    |

|   | 2.2.1 Control Blade                              |    |

|   | 2.2.2 Protocol Processing Blade                  |    |

|   | 2.2.3 Storage Blade                              |    |

|   | 2.3 Switch Architecture                          |    |

|   | 2.3.1 Control Blade                              |    |

|   | 2.3.2 Line Card (Blade)                          |    |

|   | 2.3.3 Service Blade                              |    |

|   | 2.4 Server and Switch Software Architecture      |    |

|   | 2.4.1 Control Plane to Data Plane Interaction    |    |

|   | 2.4.2 Control Plane                              |    |

|   | 2.4.2.1 Carrier Grade OS                         |    |

|   | 2.4.2.2 Shell Management                         |    |

|   | 2.4.2.4 Middleware                               |    |

|   | 2.4.2.5 Interface Management                     |    |

|   | 2.4.2.6 Application Services                     |    |

|   | 2.4.3 Data Plane                                 |    |

|   | 2.5 Network Element Management                   | 40 |

| 3 | ADVANCEDTCA OVERVIEW                             | 43 |

| _ |                                                  |    |

| 4 | MCP BACKPLANE FARRIC TOPOLOGIES AND TECHNOLOGIES | 45 |

|   | 4.1 | Com                    | munications Fabric Technologies for MCP                   | .45  |

|---|-----|------------------------|-----------------------------------------------------------|------|

|   | 4.2 | Fabri                  | ic Topologies for MCP                                     | .45  |

|   | 4.3 | Base                   | Interface (PICMG 3.0)                                     | .46  |

|   | 4.4 | Ethe                   | rnet (PICMG 3.1)                                          | .46  |

|   | 4.5 | Adva                   | nnced Switching (PICMG 3.4)                               | .46  |

|   | 4.6 |                        | age Fabrics                                               |      |

|   | 4.7 |                        | Operation                                                 |      |

|   |     |                        |                                                           |      |

| 5 | TH  | E AD\                  | VANCEDTCA SHELF                                           | 51   |

|   | 5.1 | Shelf                  | f Design                                                  | .52  |

|   |     | 5.1.1                  | Connectors                                                |      |

|   |     | 5.1.2                  | Accessibility                                             |      |

|   |     | 5.1.3                  | Rack Mounting                                             |      |

|   |     | 5.1.4                  | Backplane Support                                         |      |

|   |     | 5.1.5                  | Fasteners                                                 |      |

|   |     | 5.1.6                  | Handling                                                  |      |

|   |     | 5.1.0<br>5.1.7         | Surface Finish                                            |      |

|   |     | 5.1. <i>1</i><br>5.1.8 | EMI/EMC Design Guidelines                                 |      |

|   |     |                        |                                                           |      |

|   |     | 5.1.9                  | Power Connections                                         |      |

|   |     | 5.1.10                 | Internal Wiring                                           |      |

|   |     | 5.1.11                 | Cable Management                                          |      |

|   | ;   |                        | Subrack                                                   |      |

|   | 5.2 | Shelf                  | f FRU Device                                              | .55  |

|   | 5.3 | Telco                  | o Alarm Module                                            | .55  |

|   | 5.4 | Back                   | plane                                                     | .56  |

|   |     | 5.4.1                  | Logical versus Physical slot mapping                      |      |

|   |     | 5.4.2                  | Update Ports                                              |      |

|   |     | 5.4.3                  | Synchronization Clocks                                    |      |

|   |     | 5.4.4                  | Backplane Routing Requirements                            |      |

|   | ,   | 0                      | 5.4.4.1 Zone 2 Routing Guidelines                         |      |

|   |     |                        | · · · · · · · · · · · · · · · · · · ·                     |      |

|   | 5.5 | Shelf                  | f Power Subsystem                                         |      |

|   |     | 5.5.1                  | Operating Voltage Range                                   |      |

|   |     | 5.5.2                  | Sample Feed Capacity Calculation                          |      |

|   | ;   | 5.5.3                  | PEM Block Diagram                                         | .62  |

|   |     |                        | 5.5.3.1 Over Current Protection                           | . 64 |

|   |     |                        | 5.5.3.2 Feed Cable Inductance Compensation                | .64  |

|   |     |                        | 5.5.3.3 Contact Sequencing                                |      |

|   |     |                        | 5.5.3.4 Decoupling of backplane power planes              |      |

|   | F C | Hand                   |                                                           |      |

|   | 5.6 |                        | ware Management Interface                                 |      |

|   | ;   | 5.6.1                  | Hardware Addresses for Slots other than Front Board Slots |      |

|   | 5.7 | Shelf                  | f Management                                              | .66  |

|   |     | 5.7.1                  | Intelligent Platform Management Bus (IPMB)                |      |

|   |     | 5.7.2                  | Shelf Manager                                             |      |

|   | ,   | <b>-</b>               | 5.7.2.1 Dedicated Shelf Manager                           |      |

|   |     |                        | 5.7.2.2 Non-Dedicated Shelf Manager                       |      |

|   |     | _                      | · ·                                                       |      |

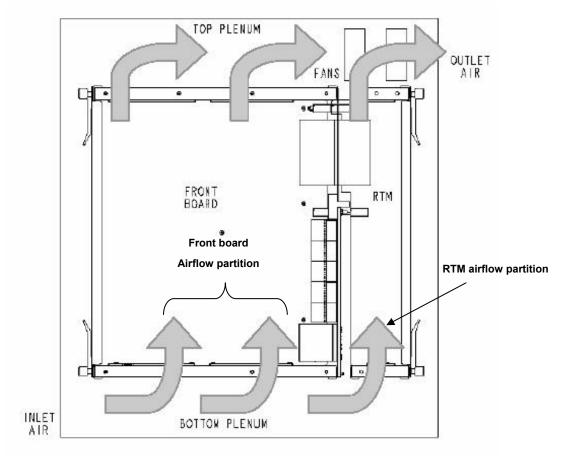

|   | 5.8 |                        | f Cooling Subsystem                                       |      |

|   | ,   | 5.8.1                  | Shelf Airflow Management                                  | . 69 |

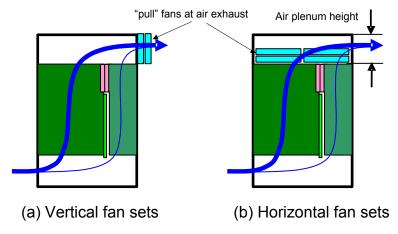

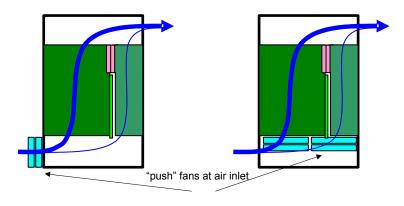

|    |          | 5.8.1.1 Fan design     | 1                                             |     |

|----|----------|------------------------|-----------------------------------------------|-----|

|    |          | 5.8.1.1.1              |                                               |     |

|    |          | 5.8.1.1.2              | Redundancy requirement                        |     |

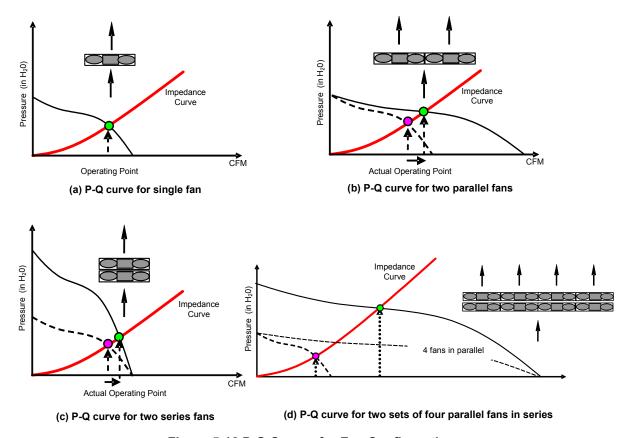

|    |          | 5.8.1.1.3              | Fan configurations                            |     |

|    | 5.8.2    | Cooling Requireme      | ents                                          | /4  |

|    | 5.9 Reg  | ulatory, Environme     | ntal, Reliability and Compliance Requirements | 76  |

| _  |          |                        |                                               |     |

| 6  |          |                        | OS                                            |     |

|    | 6.1 From | nt Board Assembly      | Common Requirements                           | 78  |

|    | 6.1.1    |                        | ret                                           |     |

|    |          |                        | et                                            |     |

|    | 6.1.2    |                        |                                               |     |

|    | 0.1.2    |                        | Labels                                        |     |

|    |          |                        |                                               |     |

|    | 6.1.3    |                        | S                                             |     |

|    | 6.1.4    |                        |                                               |     |

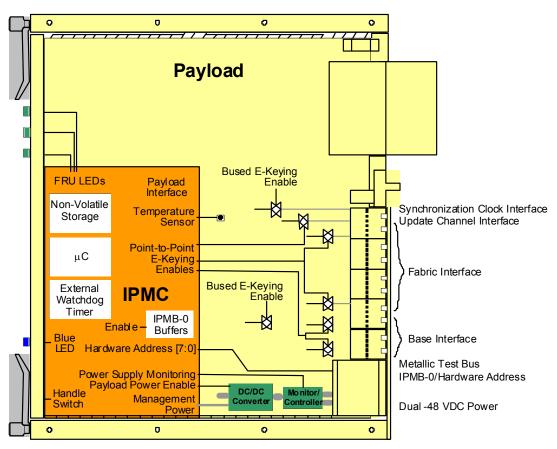

|    | 6.1.5    | Management Circu       | itry                                          | 80  |

|    |          |                        | rent Log (SEL)                                |     |

|    |          |                        | terface                                       |     |

|    |          |                        | ors                                           |     |

|    |          | 6.1.5.3.1              | Terminology                                   |     |

|    |          | 6.1.5.3.2              | False Errors vs. Missed Errors                |     |

|    |          | 6.1.5.3.3<br>6.1.5.3.4 | Raw Values, Errors and Hysteresis             |     |

|    |          | 6.1.5.3.5              | Temperature Limits                            |     |

|    |          | 6.1.5.3.6              | Fan Speed                                     |     |

|    | 6.1.6    |                        | 1 an opecu.                                   |     |

|    | 0.1.0    |                        | ization                                       |     |

|    |          |                        | or                                            |     |

|    |          | 6.1.6.2.1              | Power-On Self Test (POST)                     |     |

|    |          | 6.1.6.2.2              | Boot Manager                                  | 99  |

|    |          | 6.1.6.2.3              | Boot Monitor Console                          |     |

|    |          | 6.1.6.2.4              | Security                                      |     |

|    | 6.1.7    | Debug Interfaces       |                                               | 100 |

|    | 6.2 Con  | ımon Front Board T     | ypes                                          | 100 |

|    |          |                        |                                               |     |

| 7. |          |                        |                                               |     |

|    |          |                        |                                               |     |

|    |          | •                      | 3)                                            |     |

|    |          | •                      | on handling                                   |     |

|    | 7.4 Self | Test Support           |                                               | 104 |

|    | 7.5 Sen  | sor Support            |                                               | 104 |

|    | 7.6 Sys  | tem Event Log (SEL     | .)                                            | 104 |

|    | 7.7 Har  | dware Platform Inte    | rface (HPI)                                   | 105 |

|    | 7.8 Hea  | lth Status Reportinເ   | ]                                             | 105 |

|    | 7.9 Red  | undancy                |                                               | 106 |

|            | 7.10 Fail | safe Upgrades                                                                                                               | 106 |

|------------|-----------|-----------------------------------------------------------------------------------------------------------------------------|-----|

|            |           | ernal Interfaces                                                                                                            |     |

|            | 7.11.1    | Front Panel Serial Port (RS232)                                                                                             | 108 |

|            | 7.11.2    | System Management Interface                                                                                                 |     |

|            |           | 7.11.2.1 Command Line Interface (CLI)                                                                                       | 109 |

|            |           | 7.11.2.2 Simple Network Management Protocol (SNMP)                                                                          |     |

|            |           | 7.11.2.2.1 Platform Event Trap (PET) support                                                                                |     |

|            |           | 7.11.2.3 Remote Management and Configuration Protocol (RMCP)                                                                |     |

|            |           | 7.11.2.4.1 CIM Object Manager                                                                                               |     |

|            |           | 7.11.2.4.2 CIM Schema/ Profile                                                                                              |     |

|            | 7.12 Star | ndards Interaction/Linkage                                                                                                  | 111 |

| 8.         | ADVAN     | CEDTCA STRATUM CLOCK DISTRIBUTION                                                                                           | 113 |

|            | 8.1 Sys   | tem Issues                                                                                                                  | 113 |

|            | 8.2 Net   | work Reference Clock                                                                                                        | 113 |

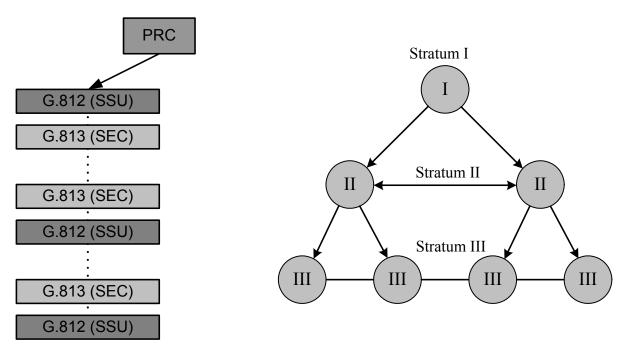

|            | 8.3 Stra  | tum Clock Network                                                                                                           | 113 |

|            | 8.3.1     | Applicable GR and ETSI Standards                                                                                            |     |

|            |           | • •                                                                                                                         |     |

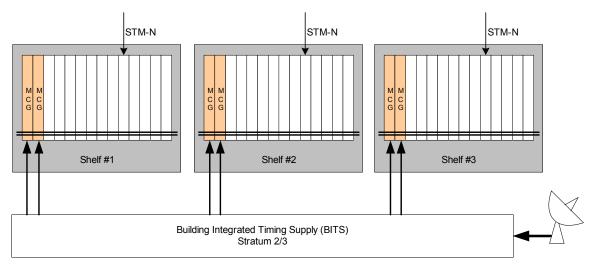

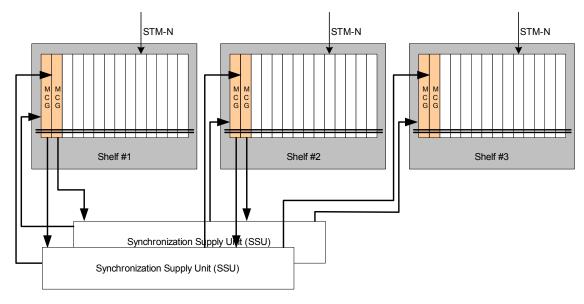

|            | 8.4 Exte  | ernal Timing Reference Connection Models                                                                                    | 114 |

|            | 8.4.2     | External Timing Mode - A Building Integrated Timing Supply (BITS)  External Timing Mode - Synchronization Supply Unit (SSU) |     |

|            | 8.4.3     | Line Timing Mode                                                                                                            |     |

|            | 8.4.4     | Redundant Connections                                                                                                       |     |

|            | 8.5 Adv   | ancedTCA Synchronization Clock Interface                                                                                    | 117 |

|            | 8.5.1     | Clock Signaling                                                                                                             | 118 |

|            | 8.5.2     | CLK 1                                                                                                                       |     |

|            | 8.5.3     | CLK 2                                                                                                                       |     |

|            | 8.5.4     | CLK 3                                                                                                                       |     |

|            | 8.5.5     | Clock Distribution Models                                                                                                   |     |

|            | 8.5.6     | Redundant Clock Usage                                                                                                       |     |

|            |           | ancedTCA Bused Electronic Keying Mechanism                                                                                  |     |

|            |           | dular Clock Synchronization                                                                                                 |     |

|            | 8.7.1     | System Master Clock Generator Design Requirements                                                                           |     |

|            |           | 8.7.1.1 Advanced Mezzanine Card Clock Support                                                                               |     |

|            |           | 8.7.1.3 Primary / Secondary Select and Synchronization                                                                      |     |

|            | 8.7.2     | Base Board Requirements                                                                                                     |     |

|            | 0.7.2     | 8.7.2.1 Baseboard Clock Interface Design Requirements                                                                       |     |

|            |           | 8.7.2.2 Control of Clock Interfaces                                                                                         |     |

|            | 8.8 Sun   | nmary                                                                                                                       | 126 |

| 0          | 4 D\/ 4 N | CEDTCA AUTOMATIC PROTECTION SWITCHING                                                                                       | 407 |

| <b>J</b> . |           | erence Documents                                                                                                            |     |

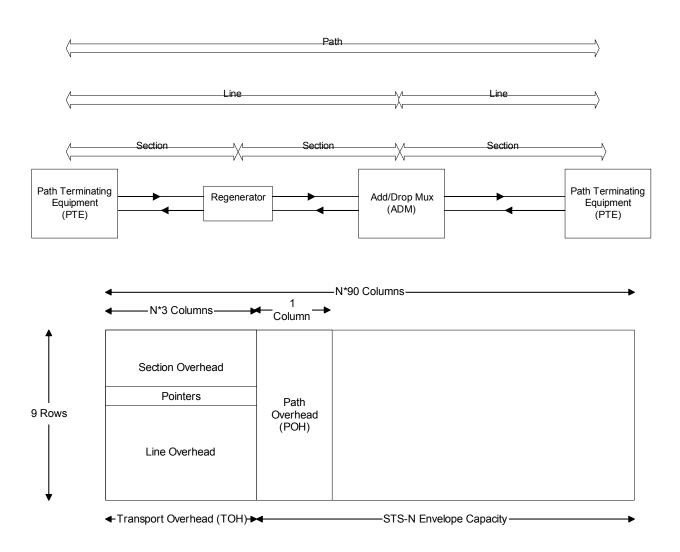

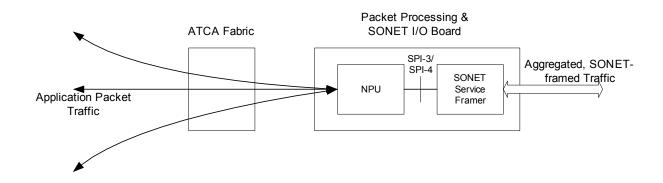

|            |           | NET and APS                                                                                                                 |     |

|            |           | Target Application                                                                                                          |     |

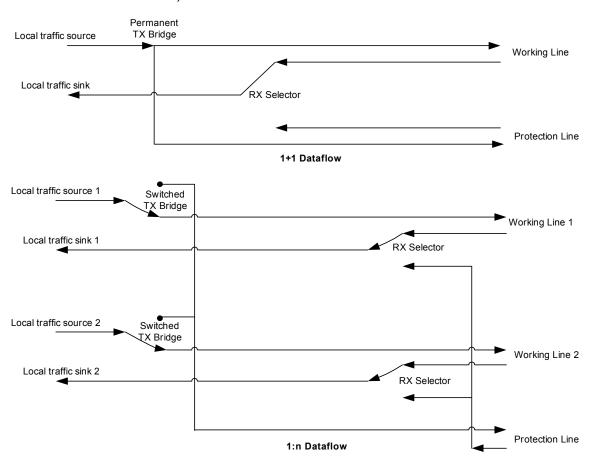

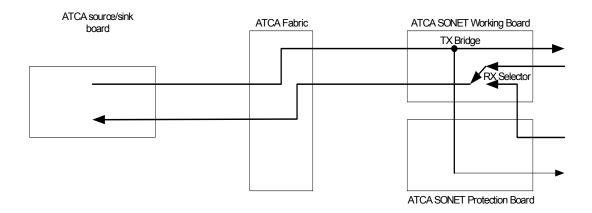

|            |           | Linear APS Equipment Protection                                                                                             |     |

|     | 9.5        | Desi                       | gn Scope                                             | 131 |

|-----|------------|----------------------------|------------------------------------------------------|-----|

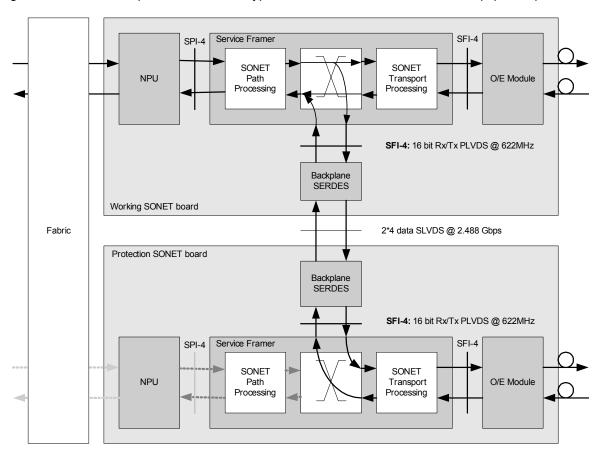

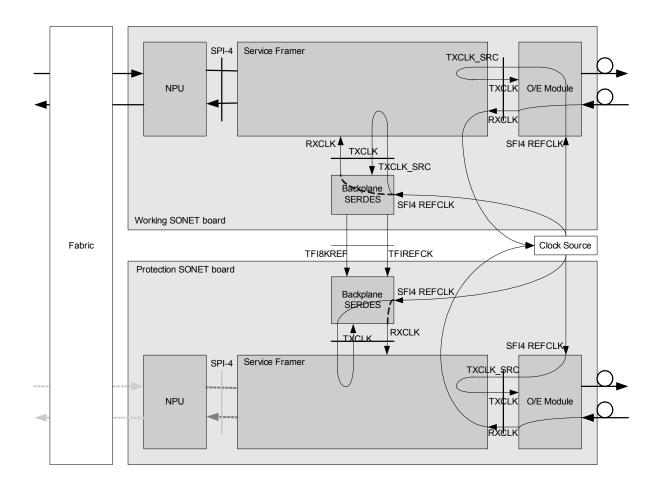

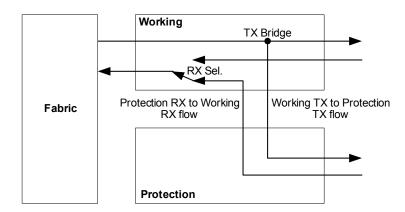

|     | 9.6        | APS                        | Dataflow, Interfaces and Clocking                    | 132 |

|     | 9          | 9.6.1                      | Data Flow                                            |     |

|     |            | 9.6.2                      | Interfaces                                           |     |

|     |            | 9.6.3                      | SONET Clocking                                       |     |

|     |            |                            | incedTCA APS Systems                                 | 136 |

|     |            | 9.7.1                      | The Update Channel Interface                         |     |

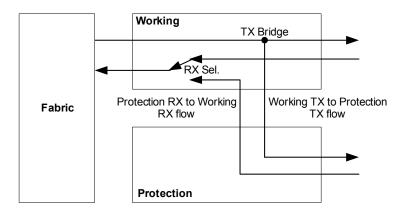

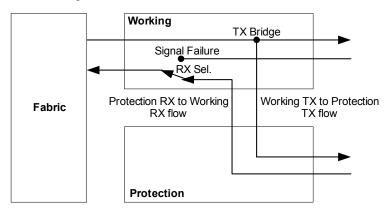

|     |            | 9.7.2<br>9.7.3             | ScenariosInitialization                              |     |

|     |            | 9.7.3<br>9.7.4             | Working Line Failure                                 |     |

|     |            | 9.7. <del>5</del><br>9.7.5 | Update Channel Failure                               |     |

|     | 9          | 9.7.6                      | Protection Line Failure                              |     |

|     | !          | 9.7.7                      | Card Failure                                         |     |

|     | 9.8        | Oper                       | n Questions                                          | 140 |

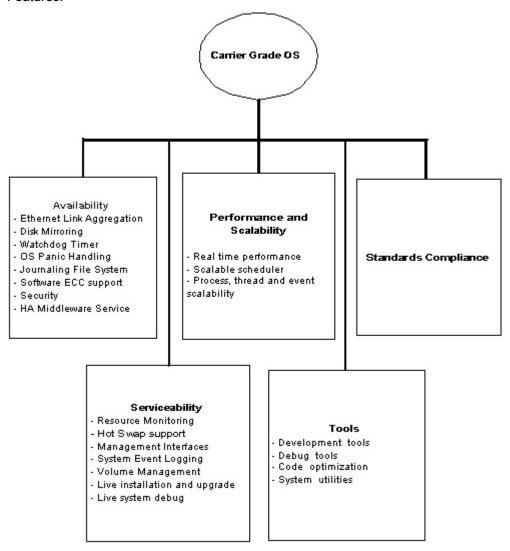

| 10. | CA         | RRIE                       | R GRADE OS                                           | 143 |

| 44  | <b>0</b> E | DTIFI                      | CATION AND DDAOTIOEO                                 | 445 |

| 11. |            |                            | CATION AND PRACTICES                                 |     |

|     |            | -                          | em Power                                             |     |

|     | 11.2       | Syste                      | em Grounding                                         | 145 |

|     |            |                            | atic Requirements                                    |     |

|     |            |                            | Storage Temperature and Humidity                     |     |

|     |            |                            | Transport Temperature and Humidity                   |     |

|     |            |                            | Operation Temperature and Humidity                   |     |

|     |            |                            | mics Requirements                                    |     |

|     |            |                            | Transport                                            |     |

|     |            |                            | Storage Operation                                    |     |

|     |            |                            | romagnetic Interference (Emissions)                  |     |

|     |            |                            | romagnetic Compatibility (Immunity)                  |     |

|     |            |                            | istics                                               |     |

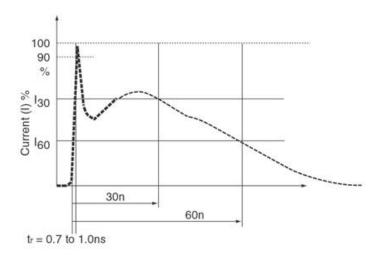

|     |            |                            | sients and Electrical Noise                          |     |

|     |            |                            |                                                      |     |

|     |            |                            | iy                                                   |     |

|     |            |                            | mability                                             |     |

|     |            |                            | bility                                               |     |

|     |            |                            | ıde                                                  |     |

|     | 11.1       | 3 Airbo                    | orne Contaminants                                    | 149 |

| 12  | DE         | SIGN                       | PRACTICES                                            | 151 |

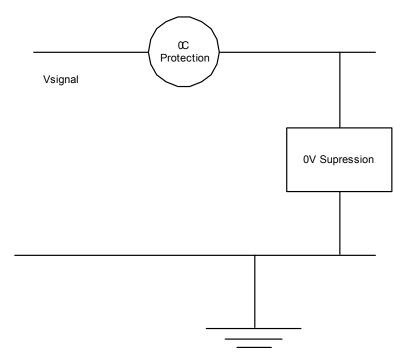

|     | 12.1       | Over                       | Voltage Transients                                   | 151 |

|     |            |                            | Power Cross Transients                               | 151 |

|     |            |                            | 12.1.1.1 Transient Protection Devices                |     |

|     |            | 12.1.2                     | Electro Static Discharge (ESD) Design Considerations |     |

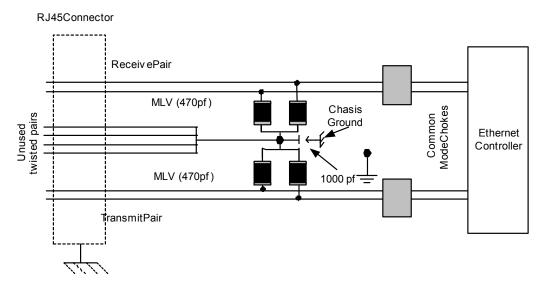

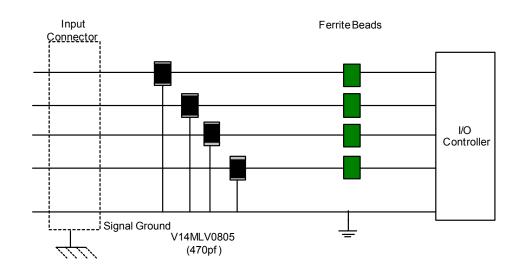

|     |            |                            | 12.1.2.1 Copper Ethernet Port                        | 153 |

| 12.1.3           | Air Discharge                                                                                                | 154         |

|------------------|--------------------------------------------------------------------------------------------------------------|-------------|

| 12.1.4           | Contact Discharge                                                                                            | 155         |

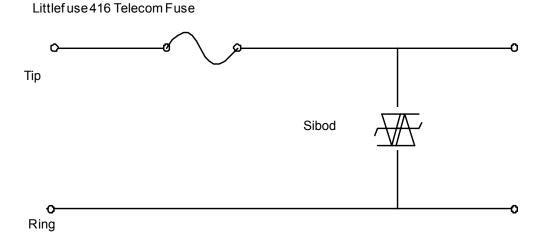

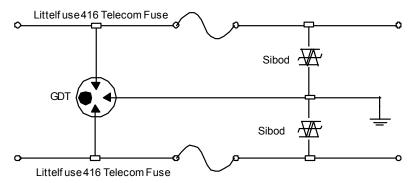

| <b>12.2 Typi</b> | cal Telecom Protection Circuit for Primary and Secondary Protection  Grounding Guidelines for Boards/Modules | 1 <b>55</b> |

|                  | 12.2.1.1 PCB Grounding Guidelines                                                                            |             |

|                  | 12.2.1.2 Clock Generator Design Guidelines                                                                   |             |

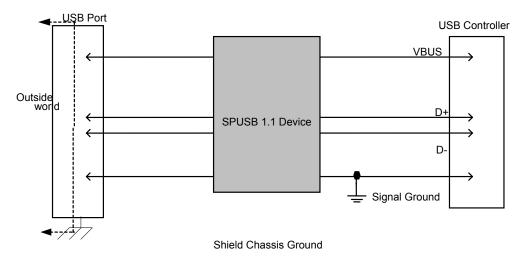

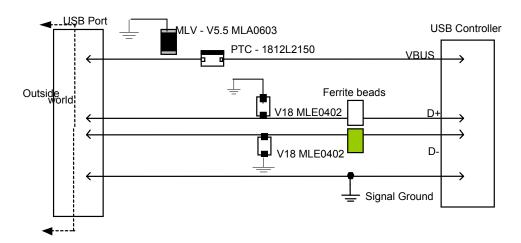

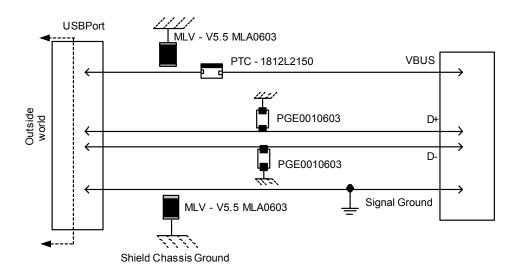

|                  | 12.2.1.3 USB Port (1.1 and 2.0)                                                                              | 157         |

|                  | 12.2.1.4 Keyboard/Mouse Port                                                                                 | 159         |

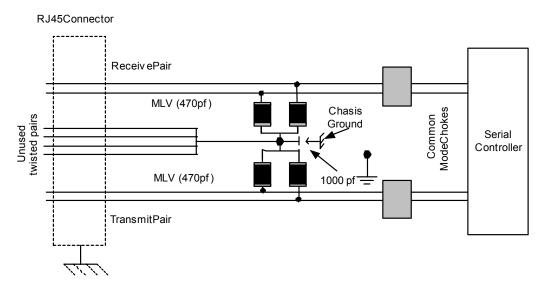

|                  | 12.2.1.5 RJ 45 Serial Port                                                                                   |             |

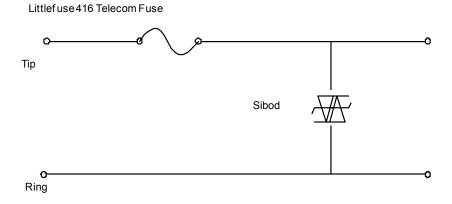

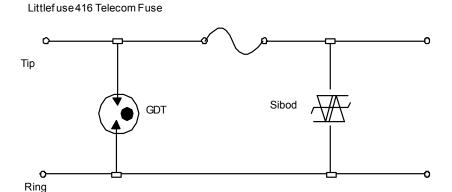

|                  | 12.2.1.6 Phone/Modem Circuits                                                                                |             |

|                  | 12.2.1.7 Primary and Secondary Protection Circuit                                                            |             |

| 10.00            | 12.2.1.7.1 Longitudinal and Metallic Protection Circuit                                                      |             |

|                  | Grounding Guidelines for the BP                                                                              |             |

| 12.3 Fron        | t Panel Connectors and Pin Assignments                                                                       | 163         |

| 12.3.1           | Serial Port                                                                                                  | 163         |

| 12.3.2           |                                                                                                              | _           |

| 12.3.3           | Ethernet Ports                                                                                               |             |

|                  | 12.3.3.1 Gigabit Ethernet                                                                                    |             |

| 10.0.4           | 12.3.3.2 Fast Ethernet                                                                                       |             |

| 12.3.4           | Telco Alarm Connector                                                                                        |             |

|                  |                                                                                                              |             |

|                  | com Protection Circuit for Grounded Systems                                                                  |             |

| 12.4.1           | Creepage and Clearance                                                                                       | 166         |

| 12.5 Svm         | bols                                                                                                         | 168         |

|                  |                                                                                                              |             |

| APPENDIX A       | A: REQUIREMENT NAMING CONVENTION                                                                             | 169         |

| APPENDIX I       | B: CARRIER GRADE OS                                                                                          | 171         |

| APPENDIX (       | C: GLOSSARY                                                                                                  | 181         |

# **Figures**

| Figure 2-1 Network Element Structure                                                                                                     | 17   |

|------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2-2 Network Element Configurations: Distinct Server and Switch Chassis                                                            | 20   |

| Figure 2-3 Network Element Configurations: Server and Switch functionality integrated into a Chassis.                                    | 20   |

| Figure 2-4 Network Element Configurations: Server and Switch Control Plane functionality integrated of a single Control Blade in chassis |      |

| Figure 2-5 Server Architecture                                                                                                           | 22   |

| Figure 2-6 Control Blade                                                                                                                 | 23   |

| Figure 2-7 Protocol Processing Blade                                                                                                     | 24   |

| Figure 2-8 Internal Storage Storage Controller and Storage on same Blade                                                                 | 25   |

| Figure 2-9 Internal Storage Storage Controller Blade and Storage Blades                                                                  | 26   |

| Figure 2-10 External Storage                                                                                                             | 26   |

| Figure 2-11 Switch Architecture                                                                                                          | 27   |

| Figure 2-12 Control Blade                                                                                                                | 29   |

| Figure 2-13 Line Card (Blade)                                                                                                            | 30   |

| Figure 2-14 Service Blade: Hardware Building Blocks                                                                                      | 31   |

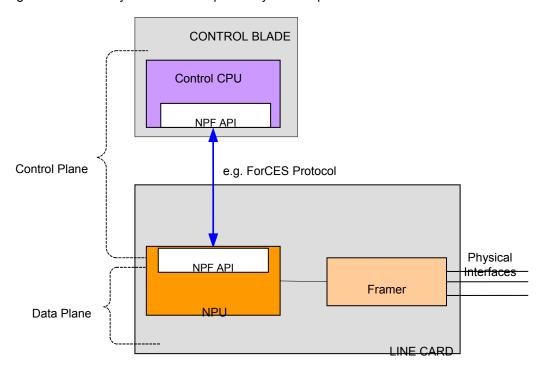

| Figure 2-15 Centralized versus Distributed Control Plane: Case I                                                                         | 32   |

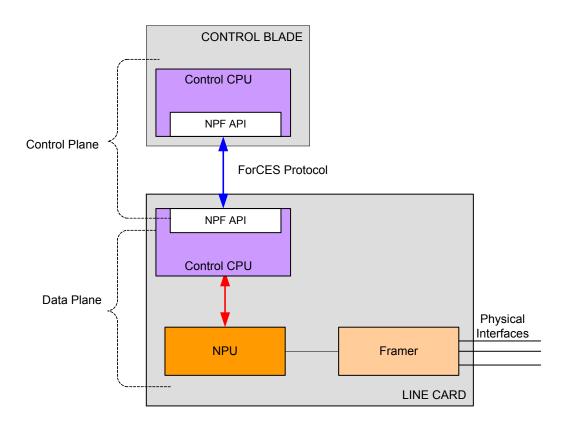

| Figure 2-16 Centralized versus Distributed Control Plane: Case II                                                                        | 33   |

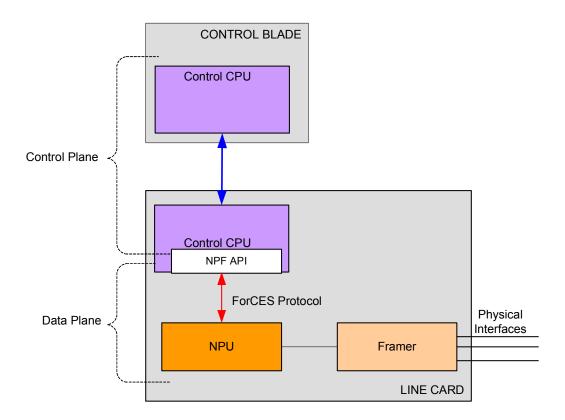

| Figure 2-17 Centralized versus Distributed Plane: Case III                                                                               | 34   |

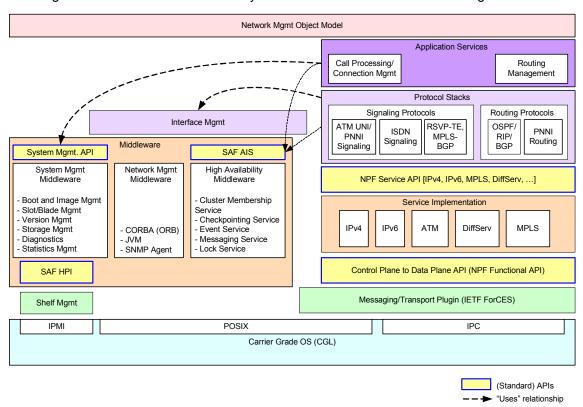

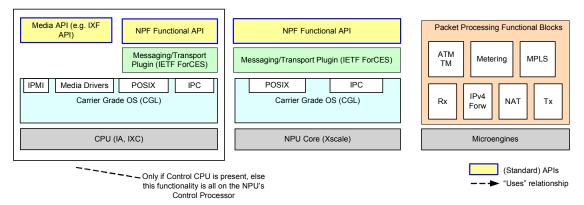

| Figure 2-18 Control Plane: Example of software building blocks                                                                           | 35   |

| Figure 2-19 Data Plane: Software building blocks                                                                                         | 39   |

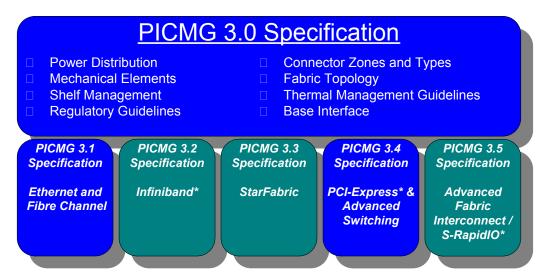

| Figure 3-1 AdvancedTCA Family of Specifications                                                                                          | 44   |

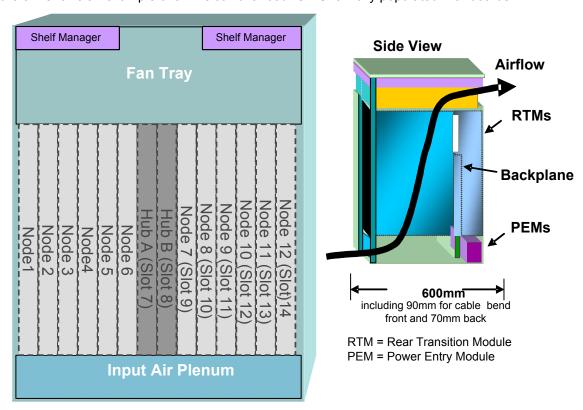

| Figure 5-1 Example of a 14 slot AdvancedTCA Shelf and components                                                                         | 52   |

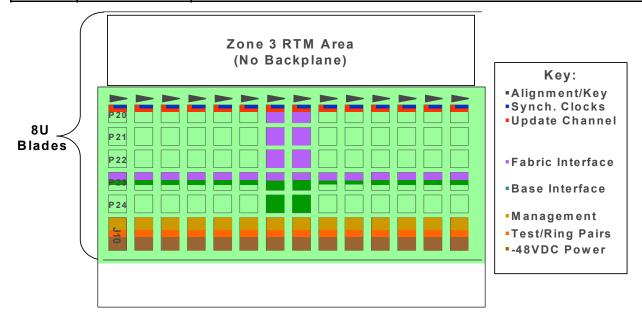

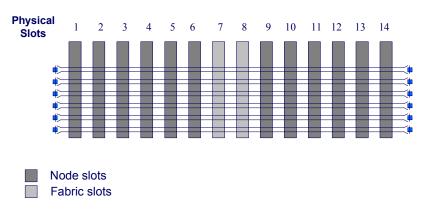

| Figure 5-2 AdvancedTCA Backplane                                                                                                         | 56   |

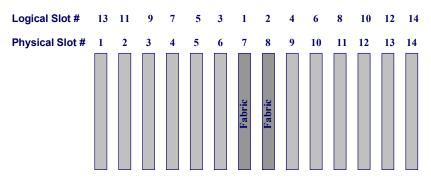

| Figure 5-3 Logical and Physical Slot Mapping                                                                                             | 57   |

| Figure 5-4 Synchronization Clock Terminations                                                                                            | 58   |

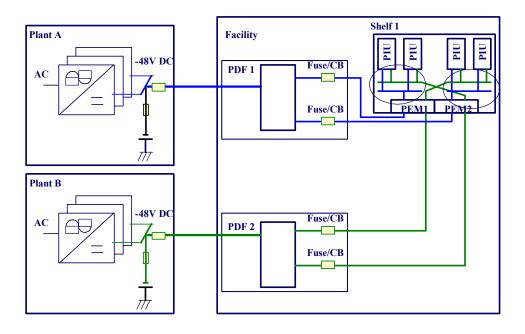

| Figure 5-5 AdvancedTCA Shelf Power Distribution                                                                                          |      |

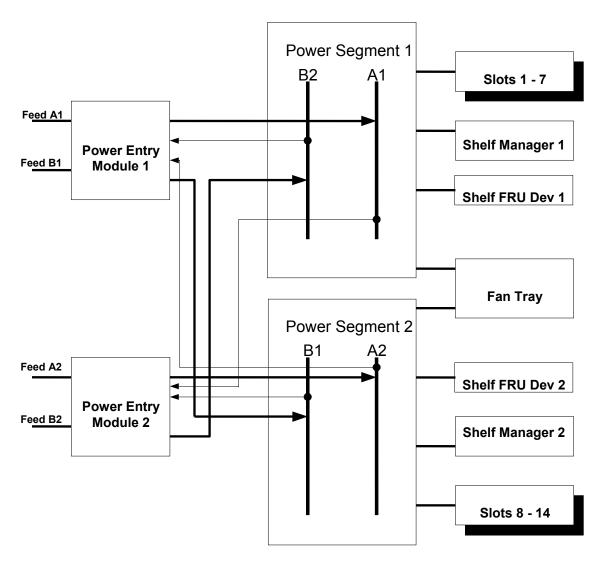

| Figure 5-6 Backplane power distribution with two power domains for large shelf with more than 7 slots                                    | . 60 |

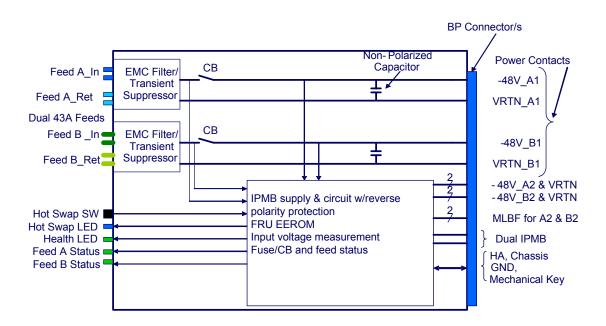

| Figure 5-7 Typical PEM Implementation                                                                                                    | 63   |

| Figure 5-8 Power Supply System Source Impedance                                                                                          | 64   |

| Figure 5-9 Hybrid IPMB Topology using Dedicated Shelf Managers                                                                           | 67   |

| Figure 5-10 Non-Dedicated Shelf Manager                                                                                                  | 68   |

| Figure 5-11 Airflow partition in the Shelf                                                                                               | 70   |

| Figure 5-12 P-Q Curves for Fan Configurations                                                                                            | 71   |

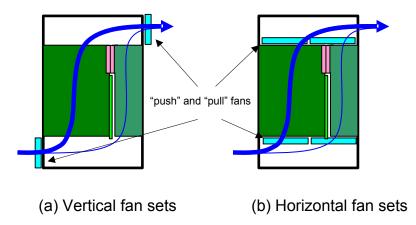

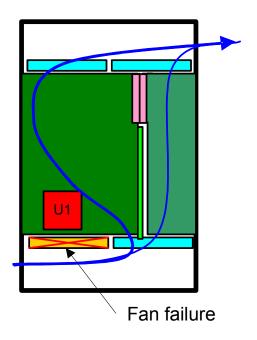

| Figure 5-13 Fan at air exhaust plenum ("pull")                                                                                           | 73   |

| Figure 5-14 Fan at air inlet plenum ("push")                                  | 73  |

|-------------------------------------------------------------------------------|-----|

| Figure 5-15 Fan at both air inlet/exhaust plenums ("push and pull")           | 73  |

| Figure 5-16 Airflow path change leaves airflow dead zone                      | 74  |

| Figure 6-1 AdvancedTCA Front Board Assembly (not to scale)                    | 77  |

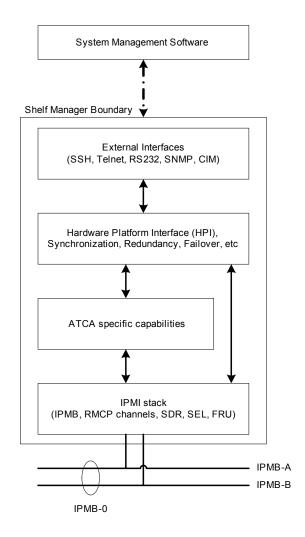

| Figure 7-1 Shelf Manager Architecture                                         | 102 |

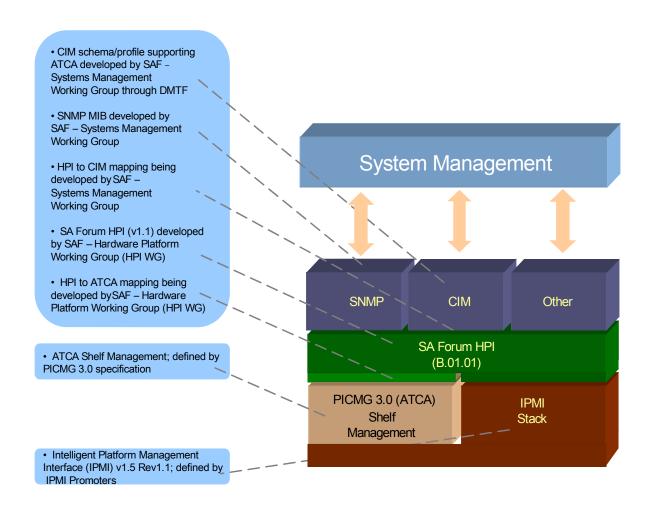

| Figure 7-2 Shelf Management Architecture                                      | 112 |

| Figure 8-1 ITU and North American Synchronization Structure                   | 114 |

| Figure 8-2 BITS Signal Distribution                                           | 115 |

| Figure 8-3 SSU Reference Signal Distribution                                  | 116 |

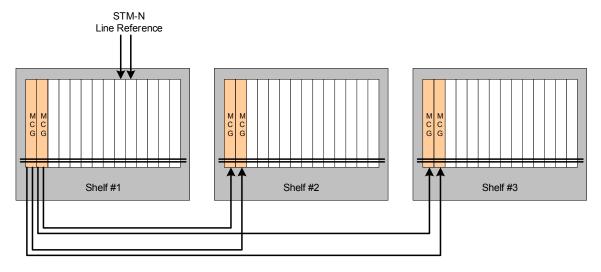

| Figure 8-4 Parent/child Reference Clock Distribution                          | 116 |

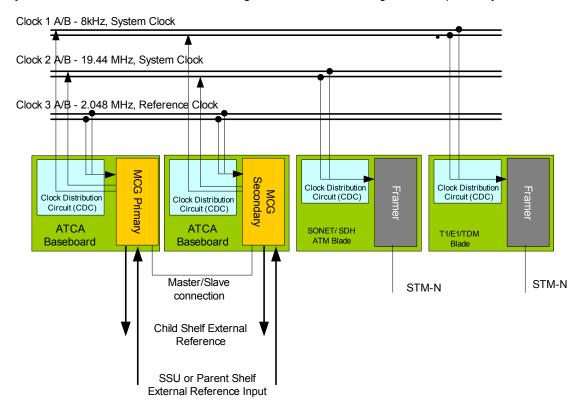

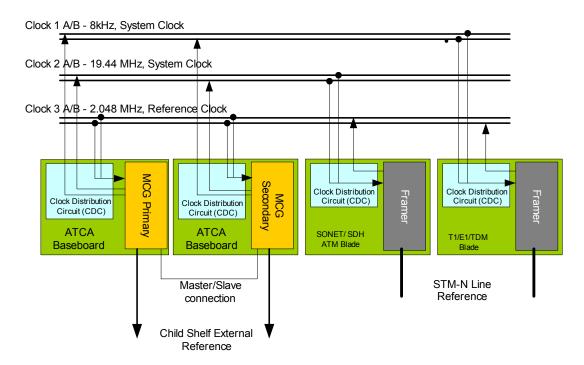

| Figure 8-5 Centralized System Clock Distribution with External Line Reference | 121 |

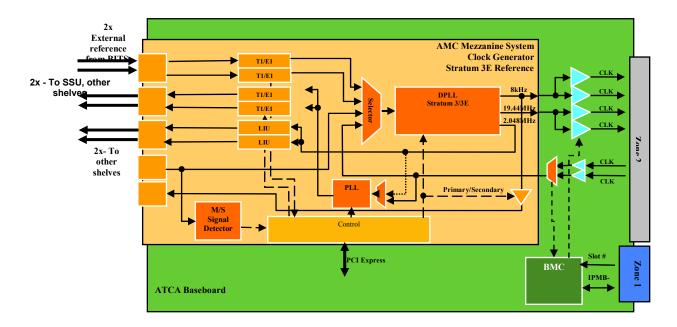

| Figure 8-6 Centralized System Clock Distribution with Line Reference          | 122 |

| Figure 8-7 Mezzanine based System Clock Generator                             | 124 |

| Figure 9-1 SONET Section, Line, and Path                                      | 128 |

| Figure 9-2 APS Dataflow (protection not switched in)                          | 129 |

| Figure 9-3 SONET End System Architecture                                      | 130 |

| Figure 9-4 AdvancedTCA 1+1 Equipment Protection                               | 131 |

| Figure 9-5 APS Dataflow                                                       | 132 |

| Figure 9-6 Clock Distribution                                                 | 135 |

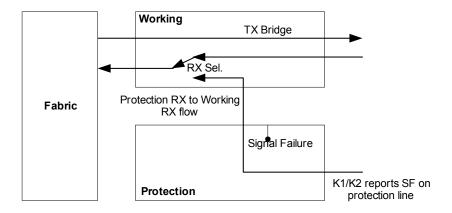

| Figure 9-7 Steady State Data flows                                            | 137 |

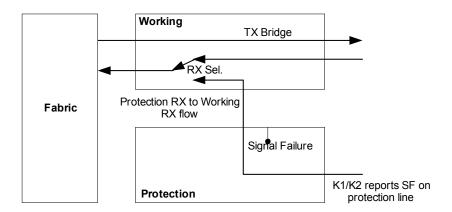

| Figure 9-8 Working RX Line Failure                                            | 137 |

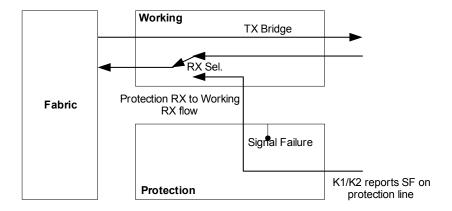

| Figure 9-9 Update Channel Failure (TX Direction)                              | 138 |

| Figure 9-10 Update Channel Failure (RX Direction)                             | 138 |

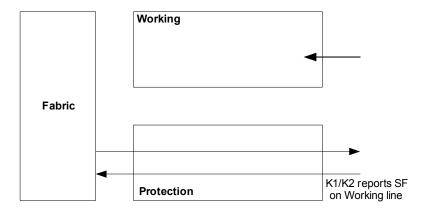

| Figure 9-11 Working Card Failure                                              | 139 |

| Figure 9-12 APS Switch to Protection Card                                     | 140 |

| Figure 9-13 Working Card Repair                                               | 140 |

| Figure 12-1 Typical Circuit Protection Configurations                         | 152 |

| Figure 12-2 Typical Protection for Telecom Circuits                           | 152 |

| Figure 12-3 IEC 61000 - 4 Waveform                                            | 153 |

| Figure 12-4 Typical Intrabuilding Ethernet Circuit Protection Configuration   | 154 |

| Figure 12-5 SPUSB1 Protection Circuit for USB 1.1 Interfaces                  | 157 |

| Figure 12-6 Alternate Protection Circuit for USB 1.1 Interfaces               | 158 |

| Figure 12-7 USB 2.0 Circuit Protection Configuration                          | 159 |

| Figure 12-8 EMI/ESD Circuit for USB 1.1 and Keyboard/Mouse Circuits           | 160 |

| Figure 12-9 Intrabuilding RJ-45 Protection Circuit                            | 161 |

| Figure 12-10 Phone Line/Modem Port Protection Circuit                         | 161 |

| Figure 12-11 Primary and Secondary Protection Telecom Circuits | 162 |

|----------------------------------------------------------------|-----|

| Figure 12-12 Telecom Protection for Grounded Systems           | 162 |

| Figure B-1 Carrier Grade OS Features                           | 171 |

## **Tables**

| Table 5-1 Typical Hardware Addresses Slots other than Front Boards | 66  |

|--------------------------------------------------------------------|-----|

| Table 6-1 Board Operating Voltage Range                            | 80  |

| Table 6-2 Payload Interface IPMI Commands                          | 81  |

| Table 6-3 Temperature Threshold Settings                           | 96  |

| Table 12-1 Example of Transients and Magnitudes                    | 151 |

| Table 12-2 8-pin Serial RJ-45 Pin Assignments                      | 163 |

| Table 12-3 10 Pin, Serial RJ-45 Pin Assignments                    | 163 |

| Table 12-4 Gb Ethernet in Assignments                              | 164 |

| Table 12-5 Pin Assignments for the Cable Interface                 | 165 |

| Table 12-6 Telco Alarm Connector Pin Assignments                   | 165 |

| Table 12-7 Creepage and Clearance Guidelines                       | 166 |

| Table B-1 Requirements for Carrier Grade Linux                     | 178 |

## 1 Introduction

Modular Communications Platforms (MCP) are industry standards-based communications infrastructure platforms and building blocks that enable efficiencies through the entire value chain including solution flexibility, faster time-to-market, vendor choice, and cost benefits. Through a growing ecosystem of standards-based suppliers, Modular Communications Platforms provide Network Equipment Providers (NEPs) with reusable development and deployment platforms, and an avenue to revive innovative product design in a climate of severe resource restraint.

Advanced Telecommunications Computing Architecture or AdvancedTCA® is a new series of industry-standard specifications for the next generation of carrier grade communications equipment. These specifications, driven by over 100 companies within the PCI Industrial Computers Manufacturing Group (PICMG\*), incorporate the latest trends in high speed interconnect technologies, next generation processors, and improved reliability, manageability and serviceability, resulting in a new blade (board) and chassis (shelf) form factor optimized for communications. The principal objective of AdvancedTCA has been to provide standardized platform architecture for carrier-grade telecommunication applications, with support for carrier-grade features.

The primary benefits of this platform are:

- Improved price-to-performance ratio with significant cost savings

- Open architecture and standard interfaces that provide a choice of vendors at various levels of integration (in contrast to being captive to a single vendor solution)

- Robust hardware and software components that incorporate redundancy, failover, hardware failure prediction, and that prevent problems for end-users

- Customized system that is optimized to run vertical stacks of applications

This chapter introduces the audience and purpose of the AdvancedTCA Modular Communications Platform Design Guide. Additionally, this chapter summarizes the content of the guide and defines guideline compliance.

#### 1.1 Audience for this Guide

This guide is for OEM hardware and software designers, architects and system integrators to develop, implement, and advantageously use systems built around the AdvancedTCA Modular Communications Platform for the telecommunications equipment market. This guide assumes that the reader understands the AdvancedTCA family of specifications.

#### 1.2 Purpose of this Guide

The AdvancedTCA MCP Design Guide is intended as a companion to the AdvancedTCA specifications and serves as a tool to aid designers in developing a common, interoperable communications platform. This document contains a set of preferred implementation guidelines for promoting building block interoperability on the base AdvancedTCA specification. This Design Guide targets communications network elements.

The AdvancedTCA family of specifications has a number of options that enable the support of a large variety of applications. However, this could increase the likelihood that AdvancedTCA building blocks may not interoperate. Key success factors for wide scale deployments of a technology include; standardization and interoperability among various implementations. This document offers guidance to AdvancedTCA equipment manufacturers on elements/building blocks that are compliant with the specifications and also interoperable with components from other vendors.

The AdvancedTCA family of specifications does not define how to implement some features that are essential for carrier grade network elements, such as, network clocks, automatic protection, and shelf management. This guide provides guidelines on implementing some of these gaps in the specification. By

following the guidelines in this guide, vendors can ensure that their components will interoperate with other complying systems.

Telecommunications systems are currently dominated by proprietary hardware systems that also have a huge investment in software. For NEPs to take advantage of cheaper Commercial Off The Shelf (COTS) hardware, it is important that the underlying features and interfaces of the modular hardware facilitate an easy migration of the NEP's software onto modular hardware. This guide offers guidance to the NEPs on how to build systems adhering to the Design Guide.

#### 1.3 Sections of this Guide

This second edition of the AdvancedTCA MCP Design Guide has been reorganized and expanded to provide clearer guidelines on how to build AdvancedTCA components and systems that are driven by the need for strong interoperability.

| Chapter                                                  | Description                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                          | Section 1: Overview                                                                                                                                                                                                                                                                                                                            |

| 1 Introduction                                           | Read this chapter for an introduction and an overview of the document.                                                                                                                                                                                                                                                                         |

| 2 Modular<br>Communications Platform<br>Architecture     | Read this chapter for a high level architectural overview of the AdvancedTCA Modular Communications Platform (MCP). This is a general model that will be used as the framework to derive specific architectures for different Network Elements (NE).                                                                                           |

|                                                          | Section 2: Building Blocks                                                                                                                                                                                                                                                                                                                     |

| 3 AdvancedTCA<br>Overview                                | Read this chapter for an overview of the AdvancedTCA specifications.                                                                                                                                                                                                                                                                           |

| 4 MCP Backplane Fabric<br>Topologies and<br>Technologies | The AdvancedTCA family of specifications has a rich set of options and configurations for backplane fabric. Read this chapter to understand the fabric options that are recommended for building MCP systems.                                                                                                                                  |

| 5 The AdvancedTCA<br>Shelf                               | Read this chapter to learn the essential requirements of an AdvancedTCA Shelf that allows it to be used by modules from multiple vendors. It is expected that the shelf will normally be sourced from a single vendor. Therefore it must be able to interoperate with multiple vendors' AdvancedTCA boards and Rear Transition Modules (RTMs). |

| 6 AdvancedTCA Boards                                     | Read this chapter for guidelines on building AdvancedTCA boards and the features that should be present in various board types.                                                                                                                                                                                                                |

| 7 Shelf Management                                       | Read this chapter to understand the architecture of the shelf manager and the standard interface to the system manager. The interface between the shelf manager and the system manager is not covered in great detail in the AdvancedTCA specifications.                                                                                       |

| 8 AdvancedTCA Stratum<br>Clock Distribution              | Read this chapter to understand the usage of the AdvancedTCA synchronization clock interfaces to properly support and distribute a Stratum 3/3E external reference within and between AdvancedTCA shelves.                                                                                                                                     |

| Chapter                                            | Description                                                                                                                                                            |  |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 9 AdvancedTCA<br>Automatic Protection<br>Switching | Read this chapter to understand the support for Automatic Protection Switching (APS) in SONET end systems such as Routers, Media Gateways, and Multi Service Switches. |  |  |

| 10 Carrier Grade OS                                | Read this chapter for the requirements of a carrier grade operating system used in MCP systems.                                                                        |  |  |

| s                                                  | ection 3: Certification and Design Practices                                                                                                                           |  |  |

| 11 Certification and Practices                     | Read this chapter to understand the certifications and practices that should be followed when developing AdvancedTCA MCPs.                                             |  |  |

| 12 Design Practices                                | Read this chapter to understand the common design practices that should be followed when building AdvancedTCA building blocks.                                         |  |  |

|                                                    | Appendices                                                                                                                                                             |  |  |

| Appendix A: Requirement Naming Convention          | Read this appendix to understand the two-letter naming convention used in the creation of the Requirement Ids in this document.                                        |  |  |

| Appendix B: Carrier<br>Grade OS                    | Read this appendix to understand the CG OS features.                                                                                                                   |  |  |

| Appendix C: Glossary                               | Read this appendix for the abbreviations and unique terms used in this document.                                                                                       |  |  |

#### 1.4 Guideline Compliance

To ensure they receive the benefits of standardization and interoperability, equipment purchasers will look for Modular Communications Platform Design Guide compliance as an attribute of modular communications hardware. The following sub-sections describe the levels of guideline compliance.

Individual vendors are responsible for ensuring their products meet the requirements of the design guide before identifying a product as Modular Platform Design Guide Version 2.0 Compliant. Modular platform adopters shall be provided with tools, such as test suites, that will aid in determining adherence to the requirements, as well as opportunities to test interoperability between products from multiple vendors.

To see the latest version of the AdvancedTCA MCP Design Guide, go to:

http://www.intel.com/go/atcadg

#### 1.4.1 Required Compliance

If a feature is *required*, the feature must be implemented to comply with the guidelines. Other architectural layers assume the presence of a required feature.

**Note:** Some required features might be nested under parent features marked as recommended or optional. In this situation, the nested *required* feature must be implemented for compliance only if implementers include the recommended or optional feature. These nested features are marked as *required if* or *recommended if*.

When a feature is defined as required, the term shall is used in the wording of the requirement.

#### 1.4.2 Recommended Compliance

If a feature is **recommended**, the feature does not need to be implemented. Implementation is, however, encouraged. The presence of a recommended feature is not to be assumed nor precluded by other architectural levels.

An implementation, which does not include a **recommended** feature, must be prepared to operate with another implementation, which does include the feature, though perhaps with reduced functionality. Similarly, an implementation, which does include the feature, must be prepared to operate with another implementation, which does not include the feature (except, of course, for the functionality the feature provides).

When a feature is **recommended**, the term **should** is used in the wording of the requirement.

### 1.4.3 Optional Compliance

If a feature is **optional**, the feature does not need to be implemented. There should be no dependencies on optional features by other architectural levels. Omitting an optional feature should have no impact on other required features or proper operation of the system.

Operating systems are not required to support optional features, but must operate in the presence or absence of those features.

When a feature is **optional**, the term **may** is used in the wording of the requirement.

#### 1.4.4 Tables of Requirements

This document lists requirements in a tabular format. Each table contains the following columns:

- ID: This column refers to an alphanumeric identifier. Each requirement has a unique identifier. The identifier comprises a 2-letter feature name followed by a sequential numbering system starting with 001. Refer to Appendix A: Requirement Naming Convention for a list of the 2-letter feature names.

- Feature Name: This column lists the feature to which this requirement corresponds.

- Requirements: This column contains the requirements to be met for required, recommended or optional compliance. Whether a requirement is required, recommended or optional can be determined by use of terminology in the requirement.

#### For example:

| ID     | Feature Name         | Requirements                                                                                                  |

|--------|----------------------|---------------------------------------------------------------------------------------------------------------|

| TC-001 | Table<br>Conventions | All requirements <b>shall</b> be listed in a table with associated ID, Feature Name and Requirements columns. |

#### 1.5 Terminology use

This document uses the terms *blades* and *boards* interchangeably. Use of the terms *MCP* system or *MCP* component indicate compliance to the requirements of the Design Guide.

## 2 Modular Communications Platform Architecture

This chapter provides a high-level architectural overview of the AdvancedTCA Modular Communications Platform (MCP). This is a general model that will be used as the framework to derive specific architectures for different Network Elements (NEs) focusing on converged communications and compute systems in carrier networks.

#### 2.1 Architecture Overview

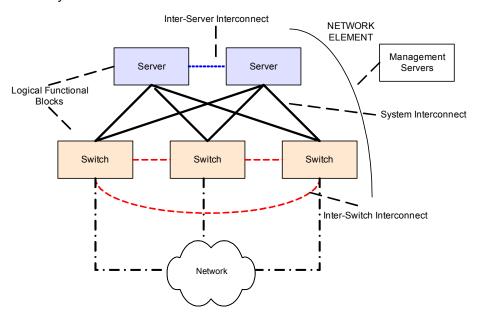

A Network Element (NE) is an entity that is configured to provide support for an application such as a multi-service switch, voice switch, edge router, Radio Network Controller (RNC) and so on in a carrier's communications network.

An NE is typically composed of one or more chassis, each of which in turn is composed of multiple blades for specific functionalities. The architecture is described in terms of such modular building blocks.

At the highest level, an MCP NE consists of the following elements:

- One or more Servers

- One or more Switches

- System (Server-Switch) Interconnects

- Network Management Server (external to the NE)

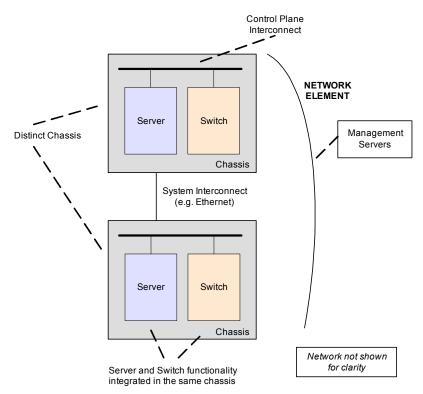

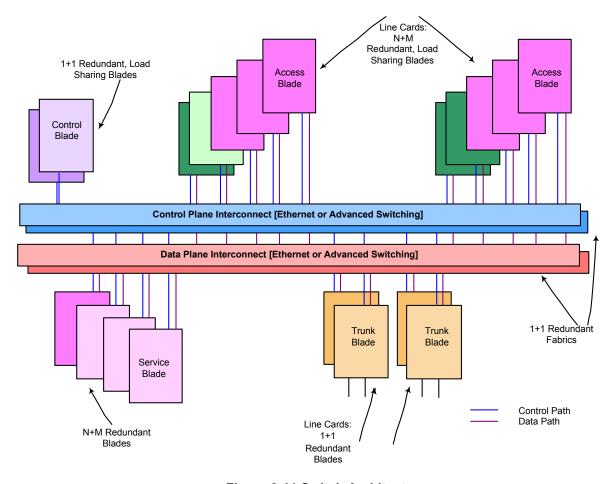

Figure 2-1 depicts a high-level block diagram of such a Network Element. Note that in all further discussions, a reference to a Server or a Switch indicates the logical function represented by each rather than to a physical entity.

**Figure 2-1 Network Element Structure**

The following sub-sections discuss the functionality associated with each of the high-level building blocks and variations of their configurations within a Network Element.

There is substantial commonality across board types between network elements allowing large amounts of reuse. Additionally, customizing the boards using standard mezzanines based on the Advanced

Mezzanine Card form factor further reduces the number of total cards needed and allows for scalability over a wide performance range.

#### 2.1.1 Server

A server (or Telecommunications Server) is the component of an NE that is primarily responsible for application-level software. The application-level software depends on the type of NE. It may support a softswitch for VOIP networks, Home Location Register (HLR), the Mobile Switching Center server including the Visiting Location Register (VLR), billing, provisioning, SLA management and so on. It generally interfaces with one or more switches and provides resource management and control capabilities across the components of the Network Element.

A server provides services in the following three planes:

| Plane            | Services                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control plane    | The Control Plane is responsible for the real-time control of the data plane. This includes signaling protocols that determine the structure of the user information data flow.                                                                                                                                                                                                                                                                                                                                                                            |

| Management plane | The Management Plane supports the management of faults, configuration, accounting, performance and security (FCAPS). Configuration may include application software parameters, configuration of addresses (IP, SS7 Point Codes etc.), signaling and routing protocols, physical and service interfaces, redundancy etc. It also supports the human interface needed to manage the server.                                                                                                                                                                 |

| Data plane       | The (user) Data Plane is the functionality associated with the transfer of user or protocol data from an ingress port (or internal data source) to an egress port (or internal data sink). In a server, Protocol Processing Blades (compute cards) support application processing for the Data Plane functionality. The Data Plane traffic in this case is associated with the protocol stacks and application software. The Data Path requirements in terms of Quality of Service are generally not as stringent for a Server as in the case of a Switch. |

Servers may also have storage resources. The various blades that constitute the server are connected by the control plane, data plane, and management plane interconnects.

#### 2.1.2 Switch

A switch is the component of an NE that is primarily responsible for data (bearer) path processing. As in the case of a server, a switch also provides service in three planes:

| Plane            | Services                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control plane    | The Control Plane is responsible for the real-time control of the data plane. This includes signaling protocols that determine the structure of the user information data flow.                                                                                                                                                                                                            |

| Management plane | The Management Plane supports the management of faults, configuration, accounting, performance and security (FCAPS). Configuration may include application software parameters, configuration of addresses (IP, SS7 Point Codes etc.), signaling and routing protocols, physical and service interfaces, redundancy etc. It also supports the human interface needed to manage the switch. |

| Data plane       | The Data Plane in a switch is also referred to as the User or Forwarding Plane. It differs from the Data Plane in a Server in that it typically supports                                                                                                                                                                                                                                   |

| Plane | Services                                                                                                                                                                                                                                                                                                                                                            |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | the transport of bearer/user data as opposed to the transport of protocol or application data. Line and Service Blades support the Data Plane functionality. The data path in a Switch comprises the physical interfaces, framers and network processors, DSPs etc. involved in packet and media processing including providing support for data path interworking. |

Additionally, a Switch might have a separate Storage Card or may have some storage capabilities on the Control blade itself.

Depending on the physical configuration of the Server and the Switch, the three planes of functionality may be shared among the servers and switches or they may be independent. Refer to Section 2.1.4 for the possible physical configurations.

#### 2.1.3 Interconnect

| Name                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Interconnect       | The interconnect between the servers and the switches depends on their physical configuration. If the server and the switch are in distinct chassis, they may be connected via Ethernet with an application-defined protocol for communication. For example, in a media-gateway communicating with a server (softswitch), MGCP is typically used as the protocol for communication. If the server and switch are integrated within a chassis, the Control Plane Interconnect (and optionally the Data Plane Interconnect) functions as the interconnect between the two. |

| Inter-Server Interconnect | The interconnect between servers depends on their physical configuration. For example, if multiple servers are in distinct chassis, then they may be connected via Ethernet. If, on the other hand, they are integrated into a single chassis (that is, functionality is distributed over multiple server blades in the chassis), the Control Plane Interconnect and optionally the Data Plane Interconnect functions as the interface between them.                                                                                                                     |

| Inter-Switch Interconnect | The interconnect between switches is similar to that between servers. In addition, switches may be interconnected using user/subscriber interfaces. For example, an ATM over SONET trunk interface on a Line Card on each switch may be used to connect two switches, thus providing increased switch capacity and user ports across the two switches.                                                                                                                                                                                                                   |

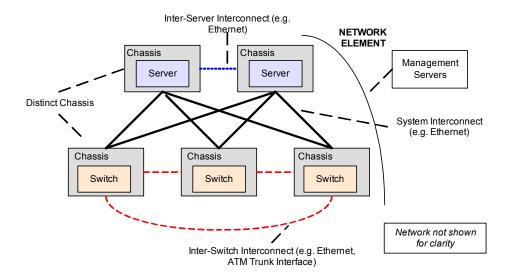

## 2.1.4 Physical Configuration

Multiple options exist for configuring Server and Switch Building Blocks comprising a NE. Although the physical configurations might vary, the functionality associated with a server and a switch remains unchanged.

Figure 2-2 Network Element Configurations: Distinct Server and Switch Chassis

Figure 2-2 shows Server and Switch functionality in distinct chassis interconnected via the System Interconnect.

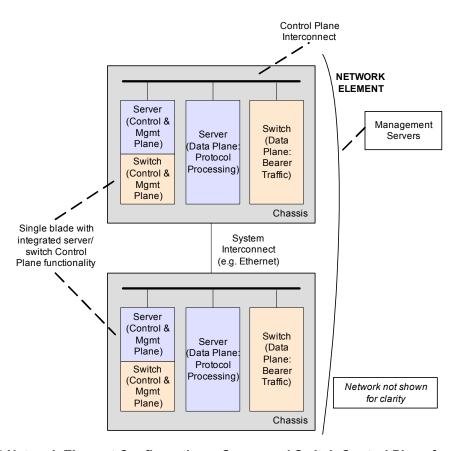

Figure 2-3 Network Element Configurations: Server and Switch functionality integrated into a Chassis

Figure 2-3 depicts Server and Switch functionality integrated into the same chassis, interconnected via the Control Plane Interconnect and optionally via the Data Plane Interconnect.

Figure 2-4 Network Element Configurations: Server and Switch Control Plane functionality integrated onto a single Control Blade in chassis

Figure 2-4 depicts the Control and Management Plane functionality of the Server and Switch integrated into one or more Control Blades in the same chassis.

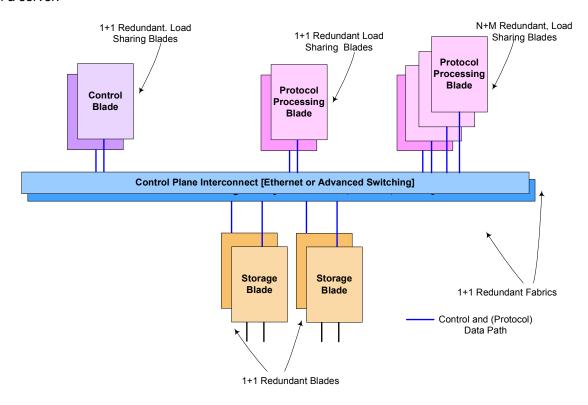

#### 2.2 Server Architecture

This section provides an overview of the architecture of a server. Figure 2-5 depicts the key components of a server.

**Figure 2-5 Server Architecture**

The high-level hardware building blocks included in a Server are as follows:

| <b>Building Block</b>        | Description                                                                                                                                                                                                                                                                                     |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control blade                | The Control Blade executes middleware software such as management of blades, event and alarm management, fault management, resource management etc. It also provides redundant access for external management, typically via Ethernet and additionally a serial port.                           |

| Protocol<br>Processing blade | Protocol Processing Blade functionality is application dependent. In a softswitch, the blades may perform SS7 call processing, provisioning, billing etc. In an RNC, the blades implement the Transport Network Layer components, providing SCCP support using Broadband SS7 or SIGTRAN.        |

| Storage blade                | A server may comprise Storage Blades. If separate ones are not present, the Control Blade could include storage capabilities. The Protocol Processing Blades may also include some storage. For example, a Protocol Processing Blade involved in billing may store billing-related data.        |

| Control plane interconnect   | All of the blades are connected via the Control Plane Interconnect which may be Ethernet or Advanced Switching. Details of this interconnect and specific technologies and topologies supported by MCP platforms are in Chapter 4. Note that there is no direct correlation between the control |

| Building Block | Description                                                                                                                                                                                                              |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | plane interconnect and the AdvancedTCA base and fabric interfaces. The control plane interconnect may use either the AdvancedTCA base or fabric interfaces depending on the needs of the particular NE being considered. |

Other than the components shown in Figure 2-5, all servers have power supplies, fans/ fan trays and management access. A server may optionally possess a Data Plane Interconnect.

The following sections expand the Server Building Blocks from a hardware and software perspective and identify the next level of modular building blocks.

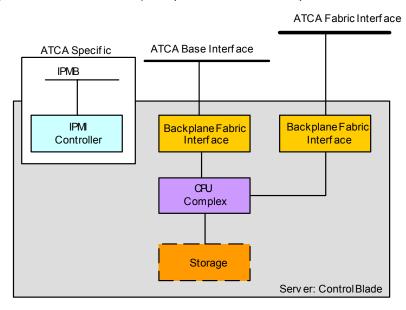

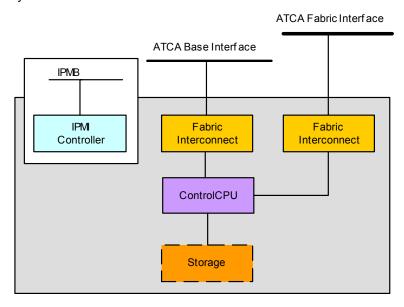

#### 2.2.1 Control Blade

A Control Blade, as depicted in Figure 2-6, consists of primarily one or more Control CPUs which support middleware functionalities such as resource management, alarm/event management etc. It may optionally have some storage such as a flash disk to store configuration information, logs, statistics etc. The Control Blade is connected to the Control Plane Interconnect via the Base or Backplane Fabric Interface. It may additionally interface with the Data Plane Interconnect also, if one exists in the server.

Additionally, in an AdvancedTCA chassis, there is a bus, referred to as the Intelligent Platform Management Bus (IPMB) over which the Intelligent Platform Management Interface (IPMI) protocol runs. IPMI provides support for autonomous monitoring, logging and recovery control functions (status of blades, ability to power-on/off blades etc.) independent on the main processors.

Figure 2-6 Control Blade

#### 2.2.2 Protocol Processing Blade

A Protocol Processing Blade, as depicted in Figure 2-7 is similar to a Control Blade. The main difference lies in the software that executes on the Protocol Processing Blades. In most cases, the same hardware can be used for Control Blades and Protocol Processing Blades.

Protocol Processing Blades may also have access to line interfaces. For example, they may have T1/E1 interfaces if they are involved in SS7 processing. To retain a lot of commonality with the Control Blade, these interfaces may be on a mezzanine card.

Figure 2-7 Protocol Processing Blade

#### 2.2.3 Storage Blade

There are several options for Storage Blades:

- Internal Storage: Storage Controller and Storage are integrated on the same blade

- Internal Storage: Storage Controller and Storage are on distinct blades

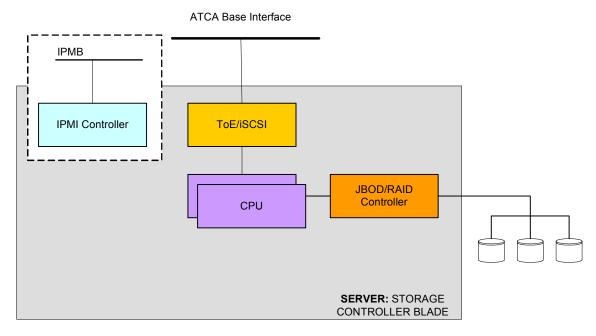

- External Storage: Storage Controller Blade in chassis interfaces with external storage such as JBOD or RAID. This blade may also be used to control storage on a Storage Blade within the chassis.

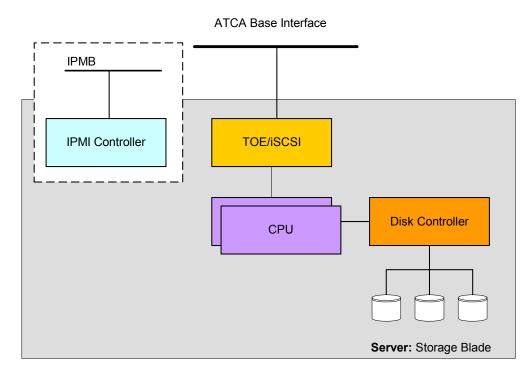

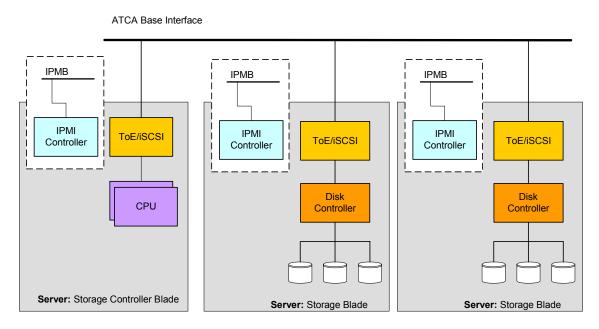

In all cases, the components include one or more CPUs, a TOE/iSCSI device, a disk controller, and storage disks. The examples depicted here show the use of iSCSI. If the fabric interface is based on PICMG 3.1, Fibre Channel connections on the backplane are also allowed and will often be a simpler solution.

Figure 2-8 depicts a storage blade in which the storage controller and storage are integrated.

Figure 2-8 Internal Storage -- Storage Controller and Storage on same Blade

Figure 2-9 shows a configuration where the storage controller and storage elements are different blades.

Figure 2-9 Internal Storage -- Storage Controller Blade and Storage Blades

Figure 2-10 depicts a configuration with external storage elements.

Figure 2-10 External Storage

#### 2.3 Switch Architecture

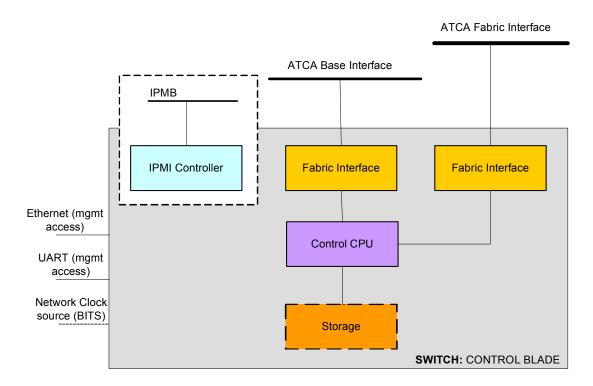

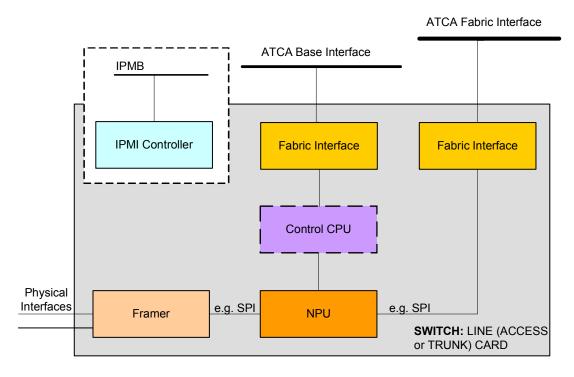

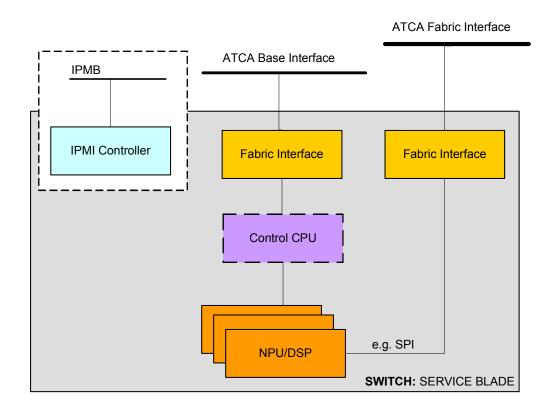

This section provides an overview of the architecture of a switch. Figure 2-11 depicts the key components of a switch.

Figure 2-11 Switch Architecture

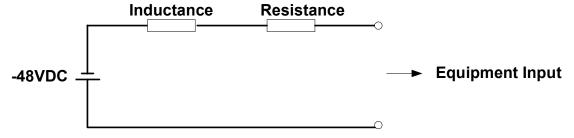

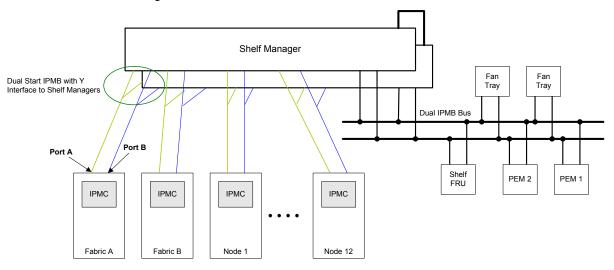

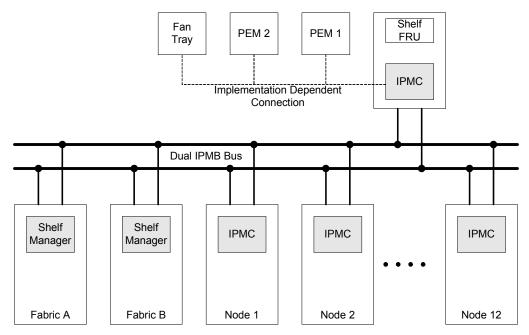

The high-level hardware building blocks included in a Switch are the following: