# STK6037

80C51-based microcontroller

- 16K flash memory

- In-system programming

- IAP programming

- Main Data Memory: 256 bytes

- AUX Memory: 320 bytes

- Timers 0, 1, 2, 3

- Watchdog timer

- UART0 and UART1

- 10-bit ADC

- 21-channel, 10-bit PWM

- Ports: 1, 2, 3 (different options)

- Low voltage detection and reset

- Operating voltage: 4.2 ~ 5.6 volts

- Operating temp. : -40 ~ +85°C

- ESD: > 4 KV (HBM)

V1 2009 May 14

The STK6037 is not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Syntek customers using or selling STK6037 for use in such applications do so at their own risk and agree to fully indemnify Syntek for any damages resulting from such improper use or sale.

# STK6037

- 1 FEATURES

- 2 ORDERING INFORMATION

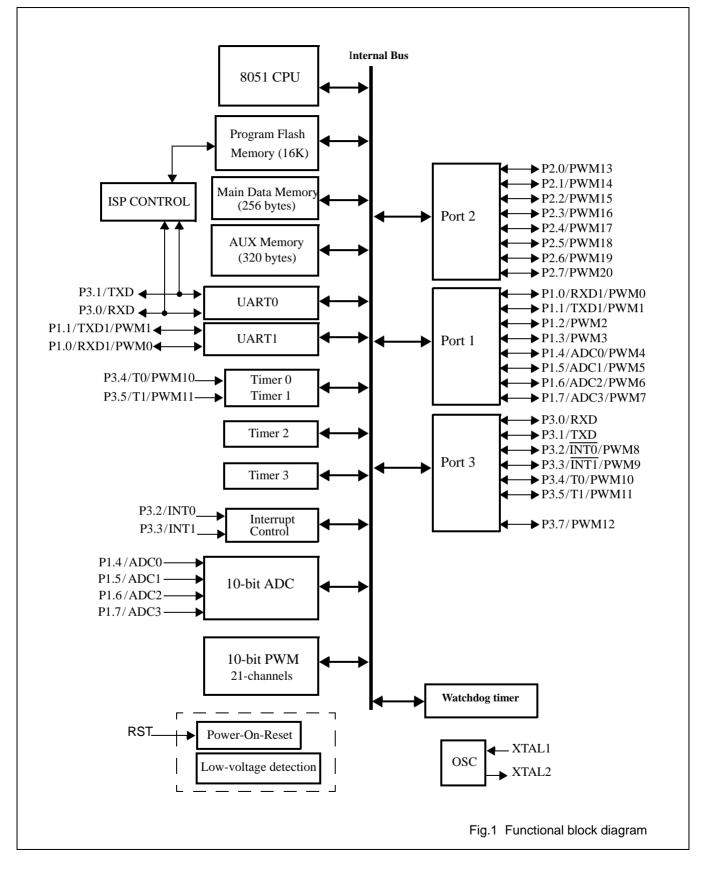

- 3 FUNCTIONAL BLOCK DIAGRAM

# 4 **PINNING INFORMATION**

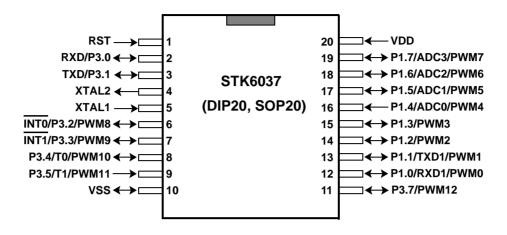

- 4.1 Pinning diagram (DIP20 and SOP20)

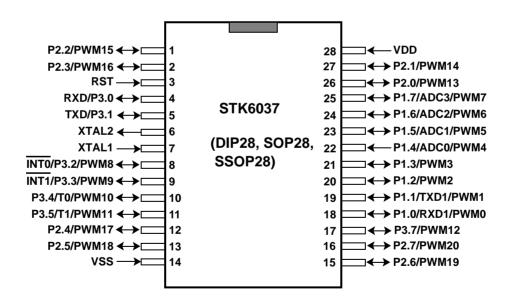

- 4.2 Pinning diagram (package of SOP28, DIP28, and SSOP28)

- 4.3 Pin description

# 5 CENTRAL PROCESSING UNIT (CPU)

- 5.1 Instruction Set and addressing modes

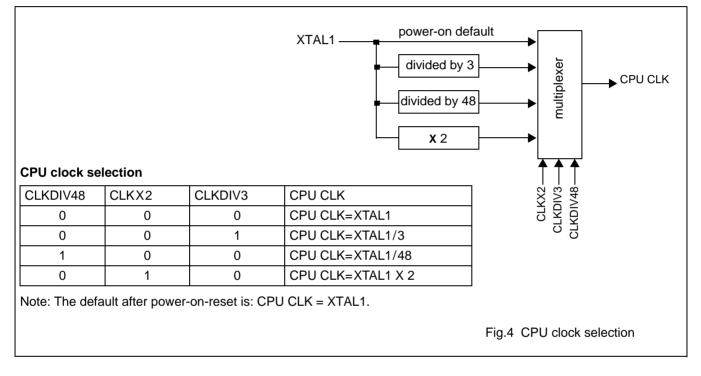

- 5.2 CPU clock and Chip Configuration Register (SFR CHIPCON)

- 5.3 Instruciton Cycle

- 5.4 Program Status Word

# 6 MEMORY ORGANIZATION

- 6.1 Program Memory

- 6.1.1 Proram ROM space

- 6.1.2 ISP prgramming for the 16K flash memory

- 6.1.3 ROM code protection

- 6.2 Main Data RAM and Special Function Register (SFR)

- 6.2.1 The lower 128 bytes of the Main Data RAM

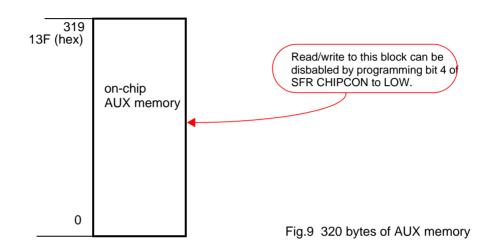

- 6.3 AUX Memory

- 6.3.1 AUX Memory space

- 6.3.2 On-chip AUX Memory

- 6.3.3 Dual Data Pointer (Data Pointer 0 and Data Pointer 1) and DPTR Select Register (SFR DPS)

# 7 SPECIAL FUNCTION REGISTERS

- 7.1 SFR allocation table

- 7.2 SFR Map Overview (98 SFRs)

- 7.3 SFR of Each Functional Block

# 8 INTERRUPTS

- 8.1 General Description

- 8.2 Interrupt Enable Registers: SFR IE and SFR EIE

- 8.3 Interrupt Priority Registers: SFR IP and SFR EIP

- 8.4 Interrupt Vectors

- 8.5 Flag Register of Extended Interrupts: SFR EXIF at address 91 hex

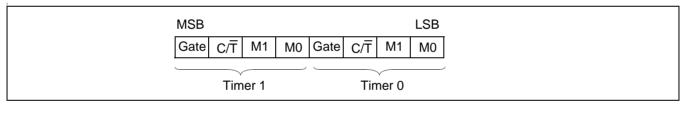

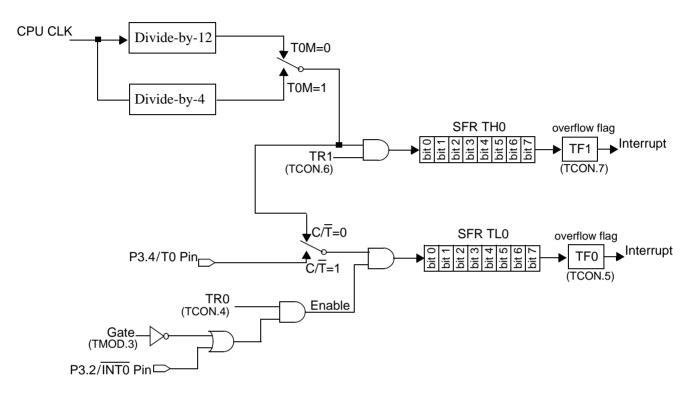

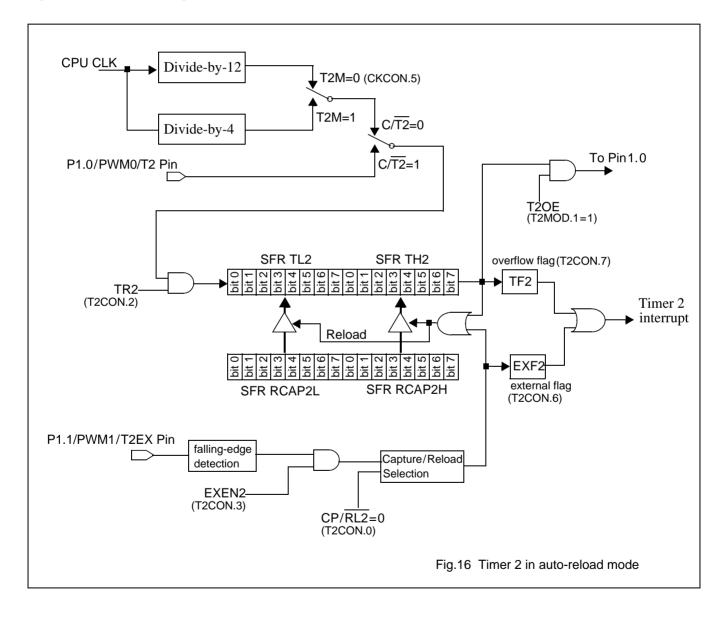

# 9 TIMER/COUNTER 0, TIMER/COUNTER 1

- 9.1 General Description

- 9.2 Mode Selection Regiser, SFR TMOD ( at 89H of SFR space)

- 9.3 Timer 0/1 Control Register (SFR TCON at 88 H of the SFR space)

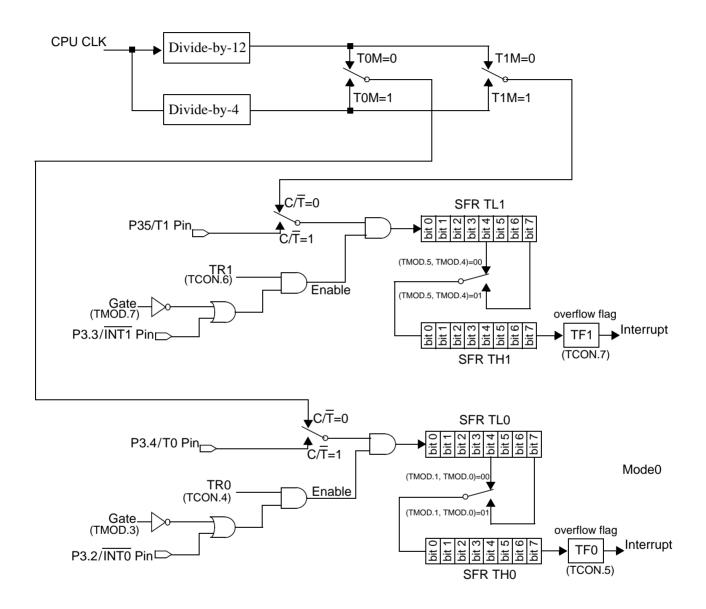

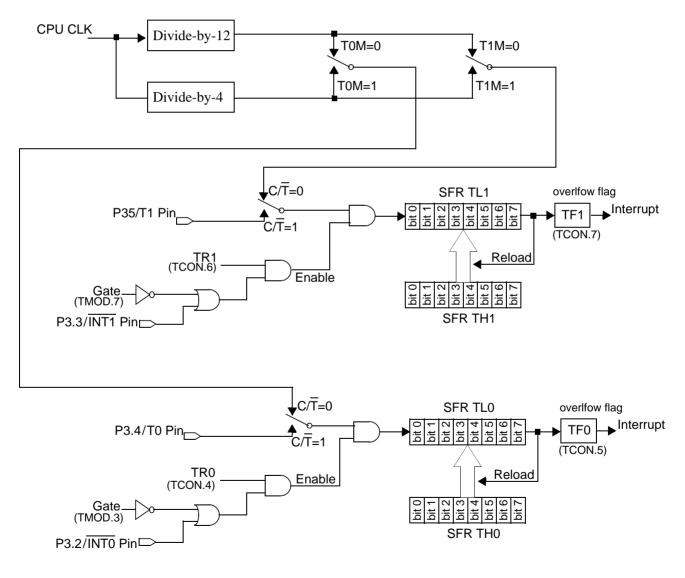

- 9.4 Clock Control Register, SFR CKCON, at address 8E hex of the SFR map

- 9.5 Operating Modes

- 9.5.1 Mode 0 (13-bit timer/counter)

- 9.5.2 Mode 1 (16-bit timer/counter)

- 9.5.3 Mode 2 (8-bit counter with auto-reload)

- 9.5.4 Mode 3 (two 8-bit counters from timer 0)

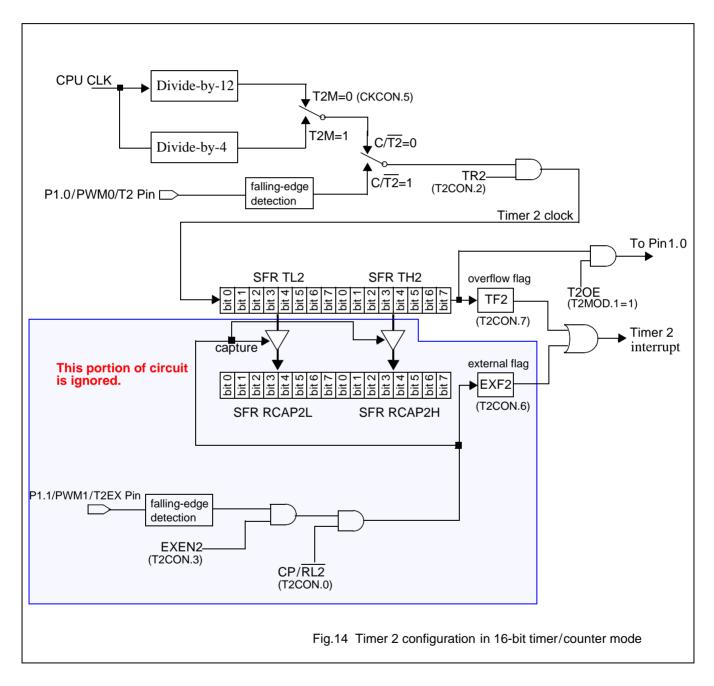

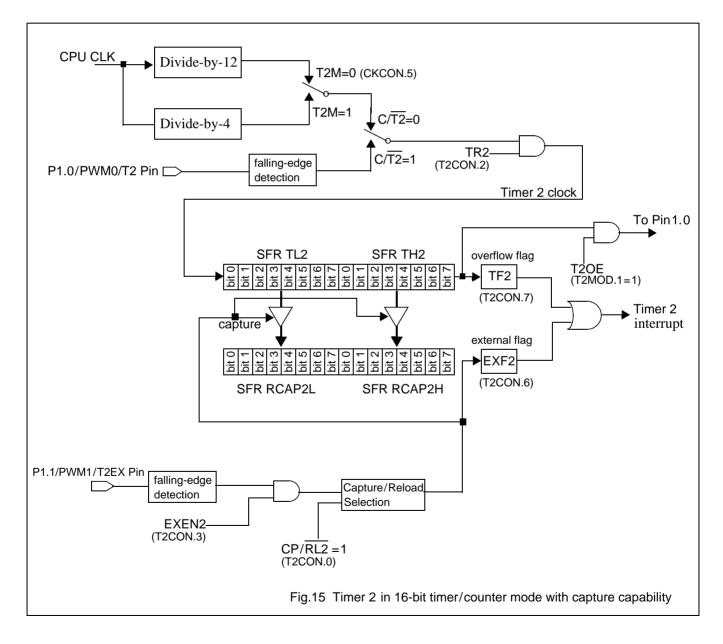

# 10 TIMER/COUNTER 2, TIMER3

# STK6037

- 10.1 General Description and operation modes

- 10.2 Special Function Registers associated with Timer 2

- 10.2.1 The T2M bit of Clock Control Register (SFR CKCON)

- 10.2.2 Timer 2 Control Register (SFR T2CON)

- 10.2.3 Timer 2 mode control register

- 10.3 16-bit Timer/Counter Mode

- 10.4 16-bit Timer/Counter with Capture capability (Capture Mode)

- 10.5 16-bit Timer/Counter with Auto-Reload capability (Auto-Reload Mode)

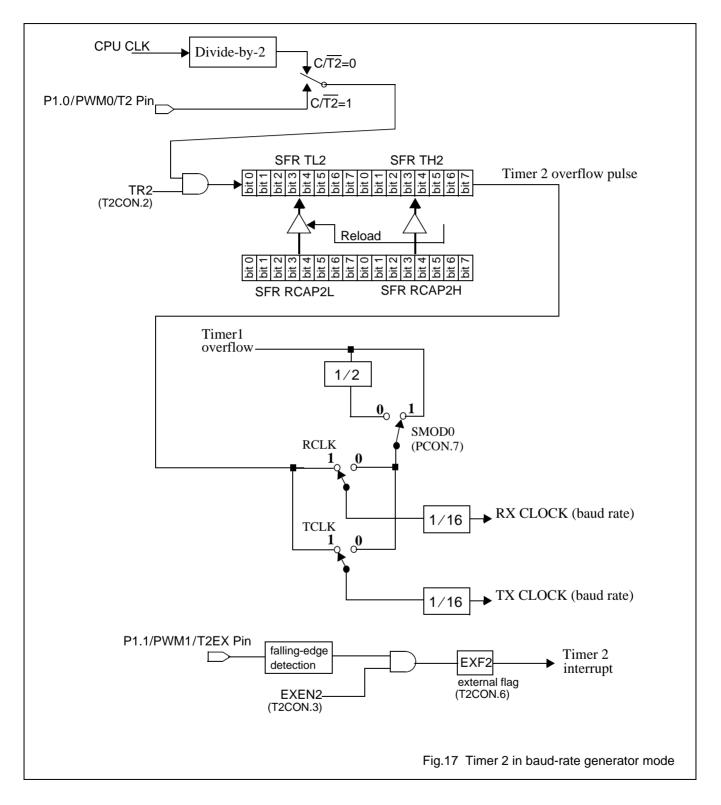

- 10.6 Baud Rate Generator Mode

- 10.6.1 calculating the value of RCAP2H and RCAP2L for a desired baud rate

- 10.6.2 More about Timer 2

- 10.6.3 Timer 2 in baud rate generator mode

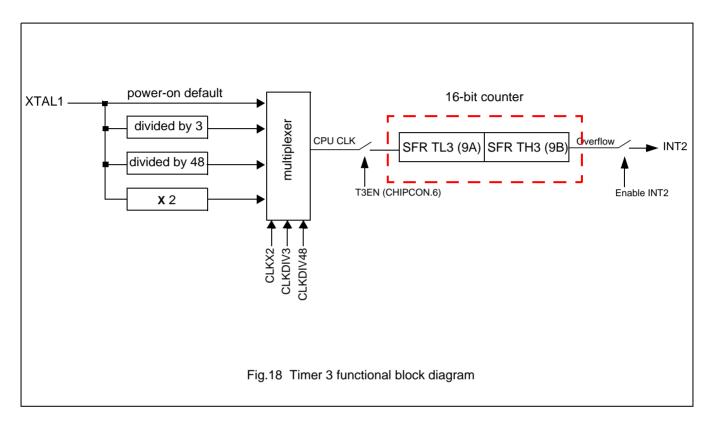

- 10.7 General Description and functional block diagram

- 10.8 Special Function Registers associated with Timer 3

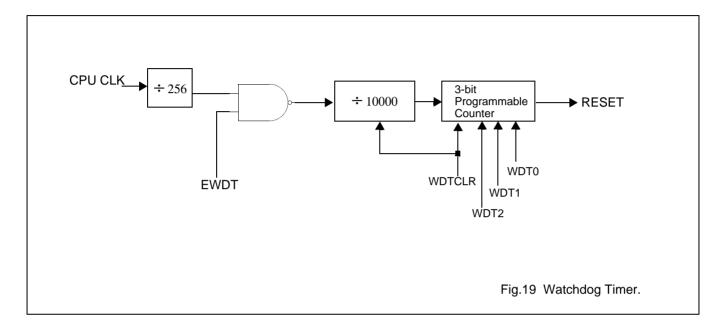

# 11 WATCHDOG TIMER

- 11.1 Functional Block Diagram

- 11.2 Watchdog Timer Control Register

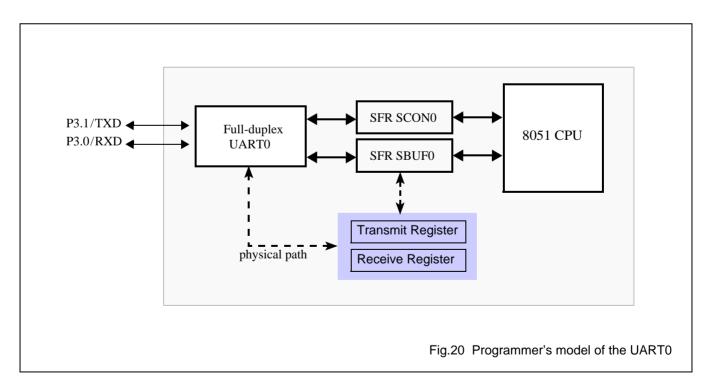

# 12 UARTO AND UART1

- 12.1 General Description

- 12.2 Summary of operation modes of UART0 and UART1

- 12.3 Control/Status Register and operaton mode of UART0

- 12.3.1 Operation modes of UART0

- 12.3.2 Control/Status Register (SFR SCON0) of UART0

- 12.4 Control/status Register and operaton mode of UART1

- 12.4.1 Operation modes of UART1

- 12.4.2 Control/Status Register (SFR SCON1) of UART1

- 12.5 Mode 0

- 12.5.1 transmission and reception of mode 0

- 12.5.2 Baud rate of Mode 0

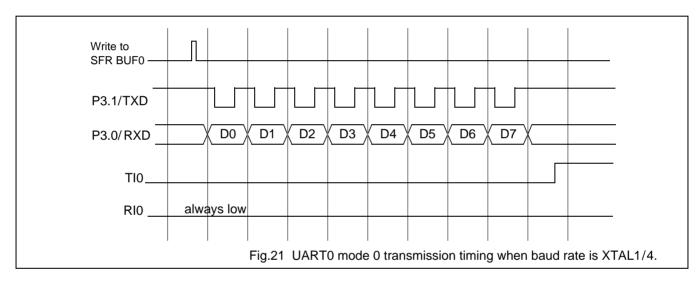

- 12.5.3 Transmission timing of mode 0

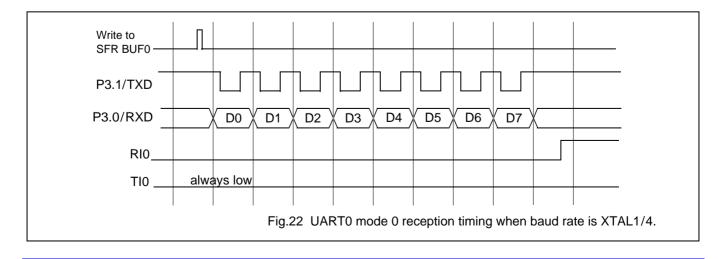

- 12.5.4 Reception timing of mode 0

- 12.6 Mode 1

- 12.6.1 Operation of mode 1

- 12.6.2 baud rate of mode 1

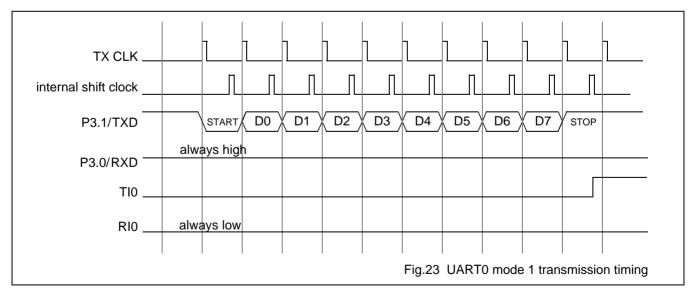

- 12.6.3 Data transmission timing in mode 1

- 12.6.4 Data reception timing in mode 1

- 12.7 Mode 2

- 12.7.1 Operation of mode 2

- 12.7.2 baud rate of mode 2

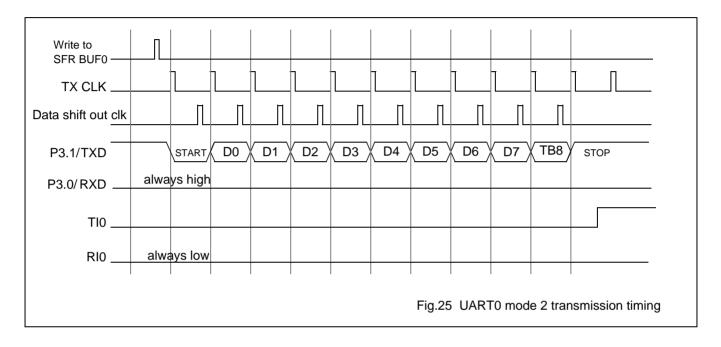

- 12.7.3 Data transmission timing in mode 2

- 12.7.4 Data reception timing in mode 2

- 12.8 Mode 3

- 12.8.1 Operation of mode 3

- 12.8.2 baud raTe of mode 3

- 12.8.3 Data transmission in mode 3

- 12.8.4 Data reception in mode 3

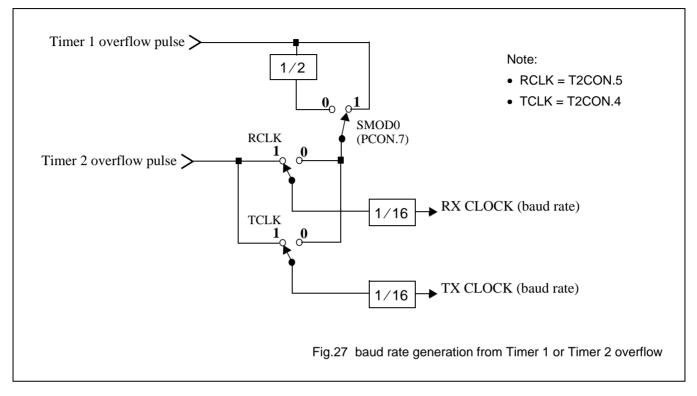

- 12.9 Baud Rate Generation for Mode 1 and Mode 3

- 12.9.1 Using Timer 1 to generate baud rates

- 12.9.2 Using Timer 2 to generate baud rates

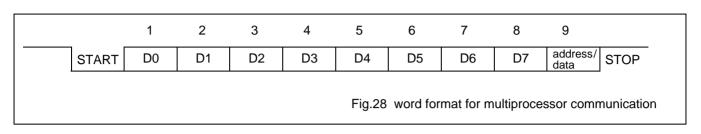

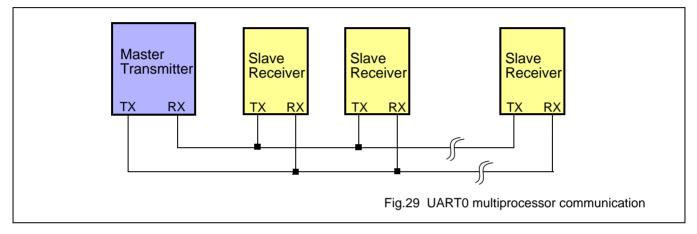

- 12.10 Multiprocessor communications

# STK6037

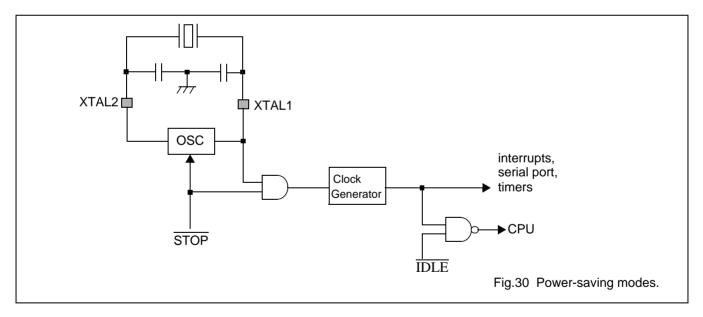

#### 13 POWER-SAVING MODES

- 13.1 Idle Mode

- 13.2 Stop mode

- 13.3 Status of external pins during power-saving modes

- 13.4 Summary of Power-saving Modes

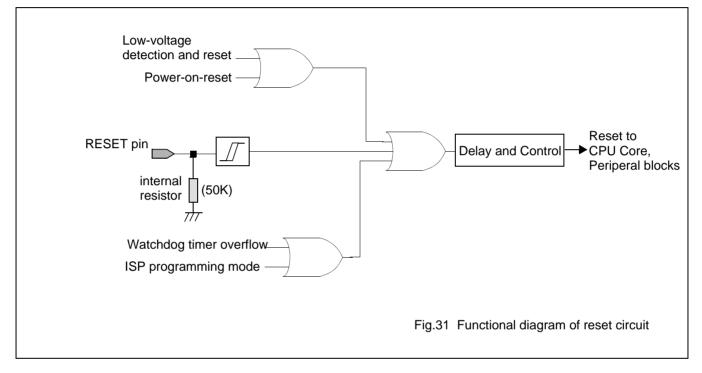

#### 14 RESET

- 14.1 Sources of RESET

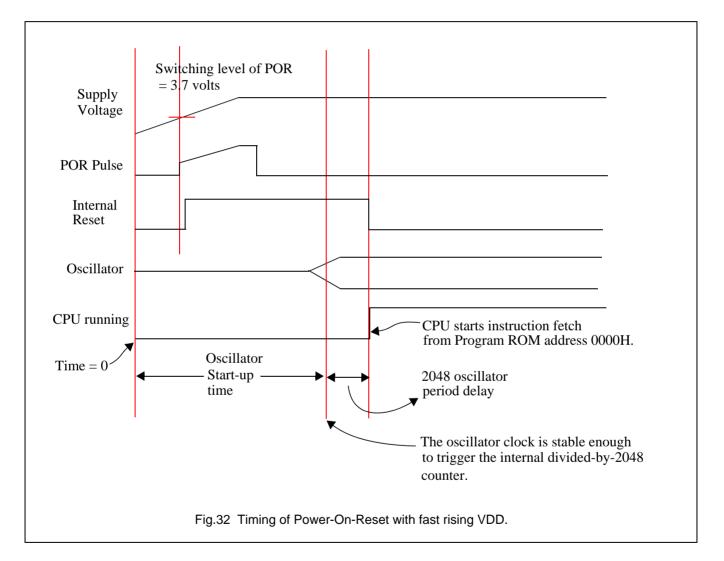

- 14.2 Power-On- Reset (POR) with fast-rising power supply

- 14.3 Asynchronous reset by adding a HIGH pulse to the RESET pin

- 14.4 Low-power detection and reset

- 14.5 Reset from the Watchdog Timer overflow

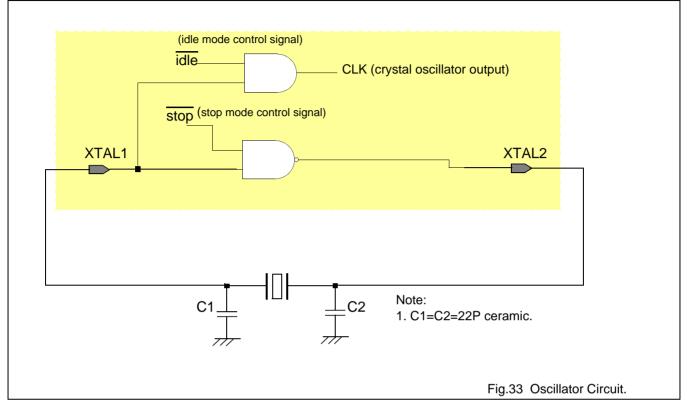

#### 15 OSCILLATOR CIRCUIT

#### 15.1 The Oscillator Circuit

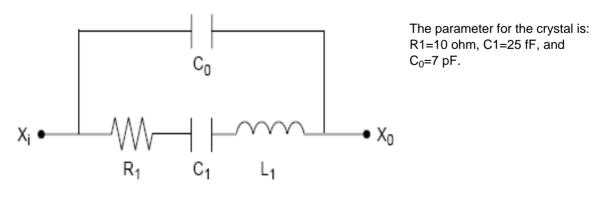

15.2 The values for R, C1, and C2

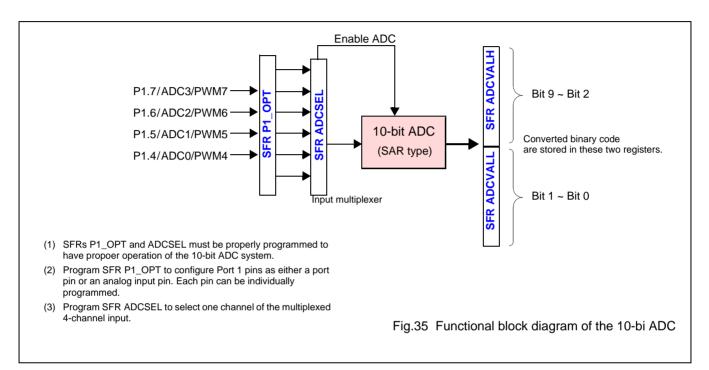

#### 16 10-BIT ANALOG-TO-DIGITAL CONVERTER (10-BIT ADC)

- 16.1 ADC functional description

- 16.2 ADC during Idle and Stop mode

- 16.3 ADC SFRs and their reset value

- 16.3.1 P1\_OPT Register

- 16.3.2 The ADCSEL Register

- 16.3.3 ADCVALH and ADCVALL Registers

- 16.4 ADC application guide

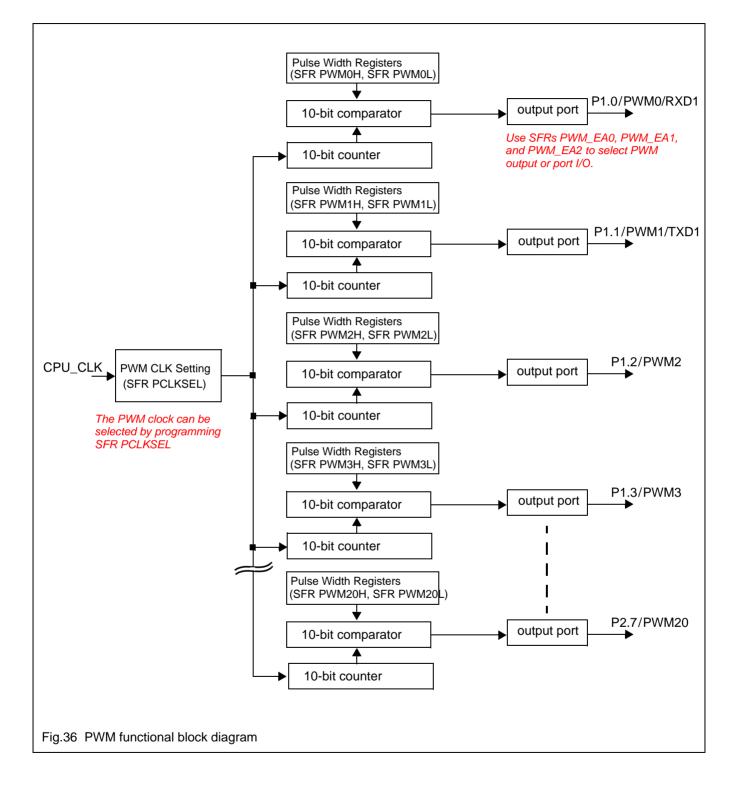

#### 17 PWM (PULSE WIDTH MODULATED OUTPUT)

- 17.1 SFRs associated with the PWM system

- 17.2 Functional block diagram of 10-bit PWMs

- 17.3 PWM/Port 1 Output Select Registers PWM\_EA0, PWM\_EA1, and PWM\_EA2

- 17.4 Pulse Width Registers (PWM0H, PWM0L ~ PWM20H, PWM20L)

- 17.5 PWM Clock Setting Register, SFR PCLKSEL

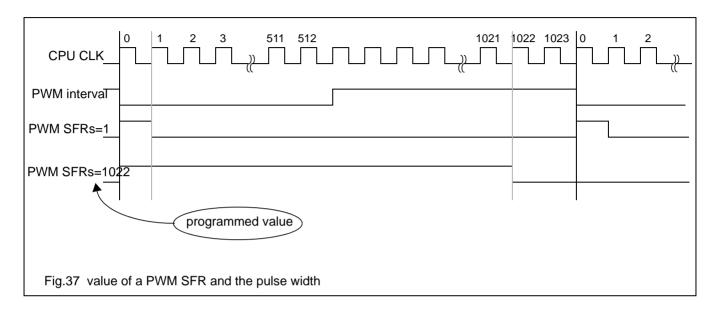

- 17.6 PWM timing diagram

- 17.7 Selection of P1.4, P1.5, P1.6, P1.7 as PWM outputs or as ADC inputs

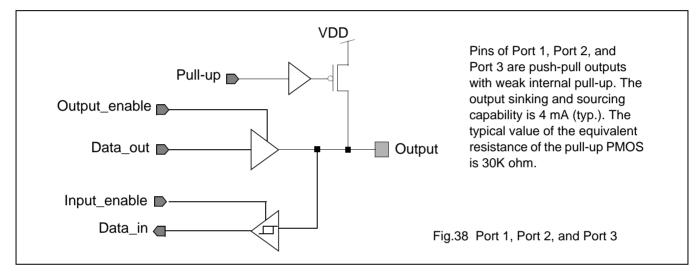

#### 18 PORT 1, PORT 2, PORT 3

- 18.1 General Description

- 18.2 Port 1, Port 2, and Port 3

- 18.3 MOVX instruction, Port 2, P3.6, P3.7

- 18.4 Multiple-Function Port Pins

#### **19 ABSOLUTE MAXIMUM RATING**

#### 20 DC/AC CHARACTERISTICS

#### 21 PIN CIRCUITS

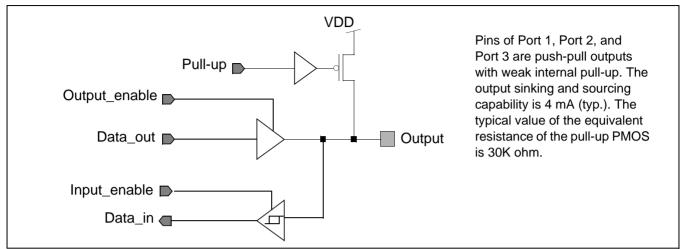

- 21.1 Port 1 (P1.0 ~ P1.7), Port 2 (P2.0 ~ P2.7), Port 3 (P3.0 ~ P3.5, and P3.7)) circuit (Bidirectional I/O, with weak Pull-up)

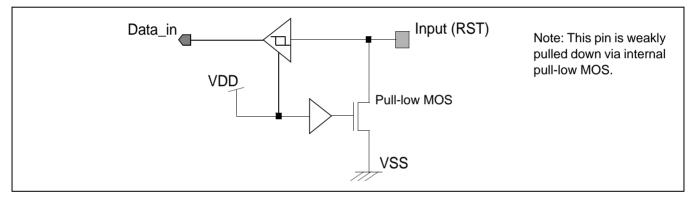

- 21.2 RST (Input)

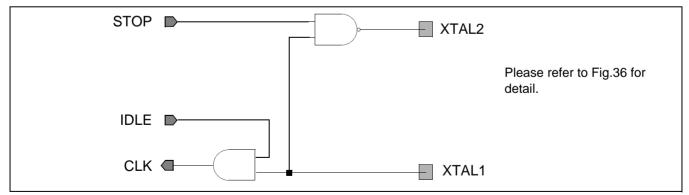

- 21.3 XTAL1, XTAL2

#### 22 REDUCING ELECTROMAGNETIC EMISSION

- 22.1 Filtering

- 22.2 Turning off ALE (not bonded out)

# STK6037

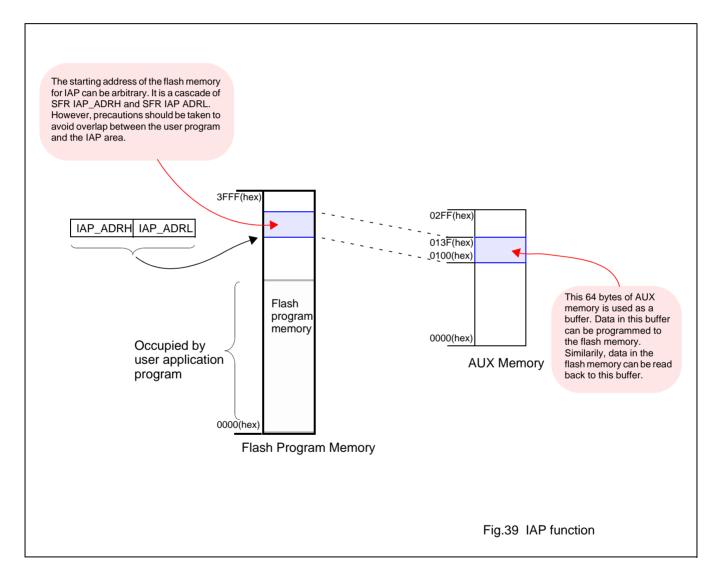

#### 23 IN-APPLICATION PROGRAMMING(IAP)

- 23.1 IAP programming

- 23.2 SFRs associated with IAP

- 23.3 SFR IAPEN

- 23.4 SFR IAP\_ADRL and SFR IAP\_ADR\_H

- 23.5 Programming caution

#### 24 INSTRUCTION SET

- 24.1 Addressing modes

- 24.2 80C51 family instruction set

- 24.3 Instruction set description

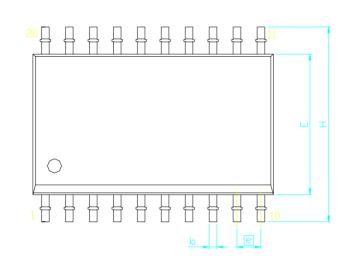

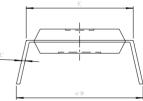

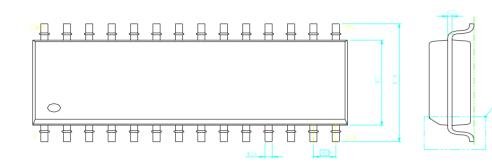

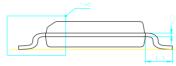

- 25 SOP20 PACKAGE OUTLINE DWRAWING

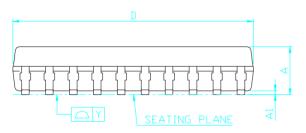

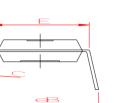

- 26 DIP20 PACKAGE OUTLINE DWRAWING

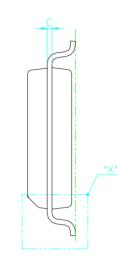

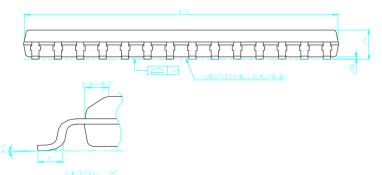

- 27 SOP28 PACKAGE OUTLINE DWRAWING

- 28 SSOP28 PACKAGE OUTLINE DWRAWING

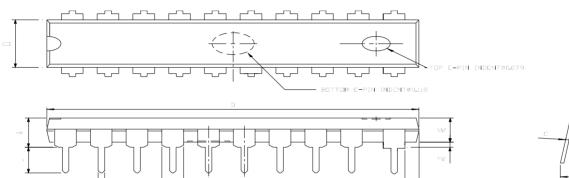

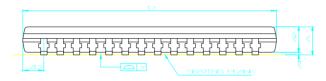

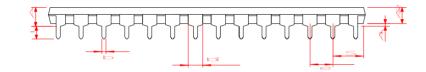

- 29 SKINNY28 PACKAGE OUTLINE DWRAWING

# 8-bit microcontroller

# STK6037

Table 1 Ordering information.....Page 10

Table 2

Pin description for 28-pin packages.....Page 13

Table 3 Chip Configuration Register.....Page 14

Table 4

Description of Chip Configuration Register (CHIPCON).....Page 15

Table 5 Program Status Word.....Page 16 Table 6 Description of Program Status Word (PSW).....Page 16

Table 7

Data Pointer 0, Data Pointer 1, and DPTR Select Register.....Page 21

Table 8 Instructions that use the DPTR.....Page 21 Table 9 Clock Control Register, SFR CKCON.....Page 22 Table 10 Description of the CKCON Register.....Page 22 Table 11 SFR allocation table.....Page 23 Table 12 The SFR Map.....Page 24 Table 13 SFR related to each functional block.....Page 27 Table 14 Overview of the interrupt system.....Page 30 Table 15 Interrupt Enable Register SFR IE.....Page 31 Table 16 Description of Interrupt Enable Register SFR IE.....Page 31 Table 17 Extended Interrupt Enable Register SFR EIE.....Page 32

Table 18

Description of Extended Interrupt Enable Register SFR EIE.....Page 32

Table 19 Interrupt Priority Register SFR IP.....Page 33

Table 20

Description of Interrupt Priority Register SFR IP.....Page 33

Table 21 Interrupt Priority Register SFR EIP.....Page 34

Table 22

Description of Interrupt Priority Register SFR EIP.....Page 34

Table 23 Flag Register SFR EXIF of Extended Interrupts 2~5.....Page 35

Table 24

SFRs associated with Timer/Counter 0 and Timer/Counter 1......Page 36

Table 25 Timer 0/1 Mode Selection Register.....Page 36 Table 26 Description of Timer 0/1 Mode Selection Register.....Page 37 Table 27 Timer 0/1 Control Register.....Page 37 Table 28 Description of Timer 0/1 Control Register.....Page 38 Table 29 Configuring Timer 2 into various operating modes.....Page 42 Table 30 Timer 2 SFRs.....Page 43 Table 31 T2M bit of SFR CKCON.....Page 43 Table 32 Description of the T2M bit of SFR CKCON.....Page 43

Table 33

Timer 2 Control Register (SFR T2CON, C8 hex).....Page 44

Table 34

Description of Timer 2 Control Register.....Page 44

Table 35 Timer 2 Mode Control Register (SFR T2MOD).....Page 46 Table 36 Description of Timer 2 Control Register.....Page 46

Table 37

Timer 2 reload value for UART Mode 1 and Mode 3 baud rate......Page 50

Table 38 Timer 3 SFRs.....Page 54 Table 39 Watchdog Timer Register.....Page 56 Table 40 Description of SFR WDT.....Page 56 Table 41 SFRs associated with UART0 and UART1......Page 57 Table 42 Operating modes of UART0 and UART1.....Page 58 Table 43 UARTO Operation Modes......Page 59

# 8-bit microcontroller

# STK6037

| Table 44 | UART0 Control/Status Register (SFR SCON0, 98h)Page 60                               |

|----------|-------------------------------------------------------------------------------------|

|          | Description of SFR SCON0Page 60                                                     |

|          | UART1 Operation ModesPage 62                                                        |

|          | UART1Control and Status Register (SFR SCON1, C0h)Page 63                            |

|          | Description of SFR SCON1Page 63                                                     |

|          | Timer 1 reload value for UART0 Mode 1 and Mode 3 baud ratePage 73                   |

|          | Power Control Register (SFR PCON)Page 75                                            |

| Table 51 | Status of external pins during Idle and Stop modesPage 77                           |

| Table 52 | .Summary of power-saving modesPage 77                                               |

| Table 53 | ADC Special Function Registers overviewPage 82                                      |

| Table 54 | P1_OPT register (address D1 hex)Page 83                                             |

| Table 55 | Description of P4_OPT Register bitsPage 83                                          |

| Table 56 | ADCSEL Register (SFR address DA hex)Page 84                                         |

| Table 57 | Description of ADC Register bitsPage 84                                             |

| Table 58 | ADCVALH Register (address DB hex)Page 84                                            |

| Table 59 | ADCVALL Register (address DC hex)Page 84                                            |

| Table 60 | SFRs for PWMsPage 86                                                                |

| Table 61 | PWM_EA0 Register(address D2 hex)Page 89                                             |

| Table 62 | Description of SFR PWM_EA0 bitsPage 89                                              |

|          | PWM_EA1 Register(address D3 hex)Page 89                                             |

|          | Description of SFR PWM_EA1 bitsPage 89                                              |

|          | PWM_EA2 Register(address D4 hex)Page 90                                             |

|          | Description of SFR PWM_EA2 bitsPage 90                                              |

|          | Pulse width registers (R/W)Page 91                                                  |

|          | Absolute Maximum RatingPage 95                                                      |

|          | DC and AC characteristicsPage 96                                                    |

|          | SFRs associated with IAPPage 101                                                    |

|          | IAPEN Register(address E4H)Page 102                                                 |

|          | Description of SFR IAPEN bitsPage 102                                               |

|          | IAP_ADRL Register(address E5H)Page 102                                              |

|          | IAP_ADRH Register(address E6H)Page 102                                              |

|          | Instructions that affect flag settings; note 1Page 104                              |

|          | Instruction set description: Arithmetic operationsPage 105                          |

|          | Instruction set: Logic operationsPage 106<br>Instruction set: Data transferPage 107 |

|          | Instruction set: Boolean variable manipulation, Program flow controlPage 108        |

|          | Description of the mnemonics in the Instruction setPage 109                         |

|          | שפטנוקונטר טו נוופ חווופרוטוונט ווו נוופ וווטנועטווט צפנרמשב דעש                    |

# List of Figures

# STK6037

| Fig. 1 Functional block diagramPage 11                                                |

|---------------------------------------------------------------------------------------|

| <b>Fig. 2</b> Pin configuration of DIP20 and SOP20 packagePage 12                     |

| Fig. 3 Pin configuration of SOP28, DIP28, and SSOP28Page 12                           |

| Fig. 4 CPU clock selectionPage 14                                                     |

| Fig. 5 CPU instruction cyclePage 15                                                   |

| Fig. 6 The phylical memories implemented on-chpPage 17                                |

| Fig. 7 Program MemoryPage 18                                                          |

| Fig. 8 Main Data Memory and SFRsPage 19                                               |

| Fig. 9 320 bytes of AUX memoryPage 20                                                 |

| <b>Fig. 10</b> Mode 0 (13-bit timer/counter) and Mode 1 (16-bit timer/counter)Page 39 |

| Fig. 11 Mode 2 operation of Timer 0, Timer 1Page 40                                   |

| Fig. 12 Mode 3 operation of Timer 0, Timer 1Page 41                                   |

| <b>Fig. 13</b> T2OE bitPage 46                                                        |

| <b>Fig. 14</b> Timer 2 configuration in 16-bit timer/counter modePage 47              |

| <b>Fig. 15</b> Timer 2 in 16-bit timer/counter mode with capture capabilityPage 48    |

| Fig. 16 Timer 2 in auto-reload modePage 49                                            |

| Fig. 17 Timer 2 in baud-rate generator modePage 52                                    |

| Fig. 18 Timer 3 functional block diagramPage 53                                       |

| Fig. 19 Watchdog TimerPage 55                                                         |

| Fig. 20 Programmer's model of the UART0Page 57                                        |

| Fig. 21 UART0 mode 0 transmission timing when baud rate is XTAL1/4Page 65             |

| Fig. 22 UART0 mode 0 reception timing when baud rate is XTAL1/4Page 65                |

| Fig. 23 UART0 mode 1 transmission timingPage 66                                       |

| Fig. 24 UART0 mode 1 reception timingPage 67                                          |

| Fig. 25 UART0 mode 2 transmission timingPage 69                                       |

| Fig. 26 UART0 mode 2 reception timingPage 70                                          |

| Fig. 27 baud rate generation from Timer 1 or Timer 2 overflowPage 72                  |

| Fig. 28 word format for multiprocessor communicationPage 74                           |

| Fig. 29 UART0 multiprocessor communicationPage 74                                     |

| Fig. 30 Power-saving modesPage 75                                                     |

| Fig. 31 Functional diagram of reset circuitPage 78                                    |

| Fig. 32 Timing of Power-On-Reset with fast rising VDDPage 79                          |

| Fig. 33 Oscillator CircuitPage 81                                                     |

| Fig. 34 crystal parametersPage 81                                                     |

| Fig. 35 Functional block diagram of the 10-bi ADCPage 82                              |

| Fig. 36 PWM functional block diagramPage 88                                           |

| Fig. 37 value of a PWM SFR and the pulse widthPage 92                                 |

| Fig. 38 Port 1, Port 2, and Port 3Page 94                                             |

| Fig. 39 IAP functionPage 100                                                          |

| Fig. 40 STK6037 SOP20 Package Outline DrawingPage 112                                 |

| Fig. 41 DIP20 package outline drawingPage 113                                         |

| Fig. 42 STK6037 SOP28 Package Outline DrawingPage 114                                 |

| Fig. 43 STK6037 SSOP28 Package Outline DrawingPage 115                                |

| Fig. 44 SKINNY 28 package outline drawingPage 116                                     |

# **1 FEATURES**

- 80C51 Central Processing Unit (CPU).

- Option for multiple CPU clock (XTAL1, XTAL1 x 2, XTAL 1 / 3, or XTAL 1 / 48).

- Industrial standard 80C51 instruction set.

- Normal mode, idle mode, and stop mode.

- Program Memory : 16 kbytes on-chip flash memory.

- with hardware ISP (In-System Programming).

- In-Application Progamming

- Program code protection.

- Main Data RAM: 256 bytes (upper 128 + lower 128 bytes) of on-chip SRAM.

- Aux Memory (AUX RAM): 320 bytes of SRAM.

- Stretched memory cycle for the MOVX instruction.

- SFRs (Special Function Register): 98 SFRs.

- Timers: Timer 0, Timer 1, Timer 2, and Timer 3.

- On-chip Watchdog Timer.

- Full-duplex UART: UART0 and UART1

- Three I/O ports: Port 1, Port 2, and Port 3.

- On-chip power-on-reset with low-voltage detection and reset.

- Interrupts: 8 sources, 2 priority level, 8 vectored addresses.

- Software enable/disable of ALE output pulse to reduce EMI.

- 4-channel, 10-bit ADC.

- 21-channel, 10-bit PWM.

- CPU operating frequency range: 2 to 30 MHz

- Operating temperature range: -40 to +85°C

- Operating voltage range: 4.2 to 5.6 V.

- ESD: ≥4 KV (HBM).

- EFT: ≥4 KV .

- Latch-up: 150 mA.

- Relibility of 16K flash memory:

- Data retention: 10 years at room temperature.

- Number of read/write cycle: > 20K.

- Available in 5 types of green package: DIP28, SOP28, SSOP28, DIP20, and SOP20.

# 2 ORDERING INFORMATION

# Table 1 Ordering information

| TYPE NUMBER    | PACKAGE                       | OUTLINE DRAWING                        |

|----------------|-------------------------------|----------------------------------------|

| STK6037ASO20G  | SOP 20 pin (Green package)    | please refer to Figure 40 on page 112. |

| STK6037ADI20G  | DIP 20 pin (Green package)    | please refer to Figure 41 on page 113. |

| STK6037ASO28G  | SOP 28 pin (Green package)    | please refer to Figure 42 on page 114. |

| STK6037AKDI28G | SKINNY 28 pin (Green package) | please refer to Figure 44 on page 116. |

| STK6037A1S28G  | SSOP 28 pin (Green package)   | Please refer to Figure 43 on page 115. |

### **3 FUNCTIONAL BLOCK DIAGRAM**

#### 4 PINNING INFORMATION

#### 4.1 Pinning diagram (DIP20 and SOP20)

Fig.2 Pin configuration of DIP20 and SOP20 package.

4.2 Pinning diagram (package of SOP28, DIP28, and SSOP28)

Fig.3 Pin configuration of SOP28, DIP28, and SSOP28

# 4.3 Pin description

Table 2

Pin description for 28-pin packages

To avoid a latch-up effect at power-on: V<sub>SS</sub> – 0.5 V < <u>voltage at any pin at any time</u> < V<sub>DD</sub> + 0.5 V .

| PIN                                     | TYPE                                                                                                                                                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26,<br>27,1,<br>2, 12,<br>13,<br>15, 16 | I/O                                                                                                                                                                         | Port 2 pins or PWM output pins.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3                                       | 1                                                                                                                                                                           | External reset input pin, active HIGH.<br>A HIGH level on this pin for at least 8 XTAL1 clocks, while the oscillator is<br>running, resets the STK6037.                                                                                                                                                                                                                                                                                |

| 4                                       | I/O                                                                                                                                                                         | Bit 0 of Port 3 or data receiver pin of the UART0.                                                                                                                                                                                                                                                                                                                                                                                     |

| 5                                       | I/O                                                                                                                                                                         | Bit 1 of Port 3 or data transmitter pin of the UART0.                                                                                                                                                                                                                                                                                                                                                                                  |

| 8                                       | I/O                                                                                                                                                                         | Bit 2 of Port 3 or input of External Interrupt 0, or PWM8 output.                                                                                                                                                                                                                                                                                                                                                                      |

| 9                                       | I/O                                                                                                                                                                         | Bit 3 of Port 3 or input of External interrupt 1, or PWM9 output.                                                                                                                                                                                                                                                                                                                                                                      |

| 10                                      | I/O                                                                                                                                                                         | Bit 4 of Port 3 or Timer 0 input, or PWM10 output.                                                                                                                                                                                                                                                                                                                                                                                     |

| 11                                      | I/O                                                                                                                                                                         | Bit 5 of Port 3 or Timer 1 input or PWM11 output.                                                                                                                                                                                                                                                                                                                                                                                      |

| 5                                       | I/O                                                                                                                                                                         | Bit 7 of Port 3 or PWM12 output.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6                                       | 0                                                                                                                                                                           | <b>Crystal pin 2:</b> output of the inverting amplifier that forms the oscillator. This pin should be left open-circuit when an external oscillator clock is used.                                                                                                                                                                                                                                                                     |

| 7                                       | I                                                                                                                                                                           | <b>Crystal pin 1:</b> input to the inverting amplifier that forms the oscillator. Receives the external oscillator clock signal when an external oscillator is used.                                                                                                                                                                                                                                                                   |

| 14                                      | 1                                                                                                                                                                           | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 28                                      |                                                                                                                                                                             | Power supply.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                         |                                                                                                                                                                             | This pin has three functions:                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                         |                                                                                                                                                                             | • Bit 0 of Port 1, or                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18                                      | 1/0                                                                                                                                                                         | PWM0 output, or                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                         |                                                                                                                                                                             | Receiver pin of UART1.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 19                                      | I/O                                                                                                                                                                         | Bit 1 of Port 1, or Transmitter pin of UART1, or PWM1 output.                                                                                                                                                                                                                                                                                                                                                                          |

| 21,<br>20,                              | I/O                                                                                                                                                                         | Bit 2, 3 of Port 1 or outputs of PWM 2, 3.                                                                                                                                                                                                                                                                                                                                                                                             |

| 22                                      |                                                                                                                                                                             | These pins have three functions:                                                                                                                                                                                                                                                                                                                                                                                                       |

| 22,<br>23,<br>24,<br>25                 | I/O                                                                                                                                                                         | <ul> <li>Bit 4 ~ 7 of Port 1, or</li> <li>Outputs of PWM 4 ~ 7, or</li> <li>Input pins of ADC 0~ 3.</li> </ul>                                                                                                                                                                                                                                                                                                                         |

|                                         | 26,<br>27,1,<br>2,12,<br>13,<br>15,16<br>3<br>4<br>5<br>8<br>9<br>10<br>11<br>5<br>6<br>7<br>14<br>28<br>7<br>14<br>28<br>18<br>18<br>19<br>21,<br>20,<br>22,<br>23,<br>24, | 26,       I/O         27,1,       I/O         2, 12,       I         13,       I         3       I         4       I/O         5       I/O         8       I/O         9       I/O         10       I/O         11       I/O         5       I/O         6       O         7       I         14       I         28       I         18       I/O         19       I/O         21,       I/O         22,       I/O         23,       I/O |

# 5 CENTRAL PROCESSING UNIT (CPU)

#### 5.1 Instruction Set and addressing modes

The STK6037's instruction set and addressing modes are completely compatible with that of industrial standard 80C51. User codes written in traditional 80C51 instruction set can be ported directly to the STK6037. Howerver, due to difference in CPU instruction clocks and timing, applications in which timer loops are used may need modification in the number of loops.

For a description of instruction set, please refer to Chapter 24, Instruction set.

### 5.2 CPU clock and Chip Configuration Register (SFR CHIPCON)

The CPU clock of the STK6037 can be selected by use of bit 5, bit 2, and bit 1 of the Chip Configuration Register (SFR CHIPCON), as illustrated in Fig.4.

The Chip Configuration Register (SFR CHIPCON, at SFR map address BF hex) controls the following:

- Enable or disable the on-chip AUX memory access,

- Enable or disable of the ALE output,

- Selection of CPU clock, and

- Enable or disable of low-power reset.

- Enable or disable Timer 3

| Table 3 | Chip | Configuration | Register |

|---------|------|---------------|----------|

|---------|------|---------------|----------|

| Chip Configuraton Register (SFR CHIPCON), located at BF hex of the SFR map, Read/Write |                             |      |          |        |      |       |         |      |  |

|----------------------------------------------------------------------------------------|-----------------------------|------|----------|--------|------|-------|---------|------|--|

| Bit Address                                                                            | Bit7                        | Bit6 | Bit5     | Bit4   | Bit3 | Bit2  | Bit1    | Bit0 |  |

| Mnemonics                                                                              | х                           | T3EN | CLKDIV48 | XRAMEN | Х    | CLKX2 | CLKDIV3 | LVR  |  |

| Reset value                                                                            | Reset value x 0 0 1 x 0 0 0 |      |          |        |      |       |         |      |  |

| Table / | Description ( | of Chin Confi   | guration Register |  |

|---------|---------------|-----------------|-------------------|--|

| Table 4 | Description   | or criip coring | Juralion Register |  |

| MNEMONIC | BIT POSITION | FUNCTION                                                                                                                    |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------|

|          | CHIPCON.7    | Not implemented.                                                                                                            |

|          |              | Enable or disable Timer 3.                                                                                                  |

| T3EN     | CHIPCON.6    | If T3EN=1, the selected CPU clock is added to Timer 3.                                                                      |

|          |              | If T3EN=0, the selected CPU clock is not added to Timer 3.                                                                  |

| CLKDIV48 | CHIPCON.5    | Enable or disable the option of dividing XTAL1 clock by 48.                                                                 |

|          |              | Enable or disable of the on-chip AUX memory access.                                                                         |

| XRAMEN   | CHIPCON.4    | • XRAMEN= 1 enables the read/write access to the on-chip AUX memory.                                                        |

|          |              | • XRAMEN= 0 disable the read/write access to the address AUX memory.                                                        |

|          | CHIPCON.3    | Not implemented.                                                                                                            |

| CLKx2    | CHIPCON.2    | Bits CLKDIV48, CLKx2, and CLKDIV3 are used to select CPU clock frequecny.                                                   |

|          |              | The CPU clock can be selected to be XTAL1, XTAL1÷3, XTAL1÷48, or XTAL1x2, by programming bits CLKDIV48, CLKx2, and CLKDIV3. |

| CLKDIV3  | CHIPCON.1    | The default after power-on-reset is: CPU CLK = XTAL1.                                                                       |

|          |              | Please refer to Fig.4. for selected CPU frequency versus programmed value.                                                  |

|          |              | Enable the low-voltage reset function.                                                                                      |

| LVR      | CHIPCON.0    | <ul> <li>LVR=0 enables the low-voltage reset function.</li> </ul>                                                           |

|          |              | <ul> <li>LVR=1 disables the low-voltage reset functon.</li> </ul>                                                           |

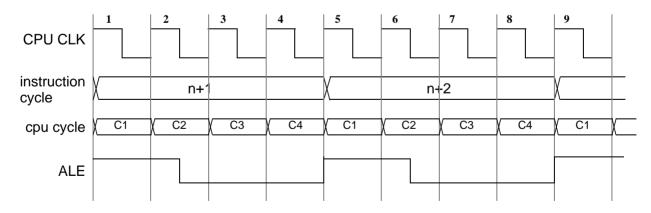

#### 5.3 Instruciton Cycle

The STK6037's CPU has a **pipe-line architecture**, and therefore execution of instructions are overlapped. While the CPU is executing the current instruction, the next instruction is also being fetched. The nominal instruction cycle is 4 CPU clocks. In each instruction cycle, the ALE signal rise to HIGH at the begining of the cycle and stays high for 1.5 CPU clocks.

The following diagram illustrates the relation among system clock (CPU CLK), instruction cycle, CPU cycle, and ALE. Simple instructions can be executed in just one instruction cycle, which consists of 4 CPU clocks.

Fig.5 CPU instruction cycle.

# 5.4 Program Status Word

The current state of the CPU is reflected in the Program Status Word (PSW) register, which is located at SFR address D0(hex).

# Table 5 Program Status Word

| PROGRAM STATUS WORD (SFR PSW), LOCATED AT D0H OF THE SFR MAP |      |      |      |      |      |      |      |      |

|--------------------------------------------------------------|------|------|------|------|------|------|------|------|

| Bit Address                                                  | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| Mnemonics                                                    | CY   | AC   | F0   | RS1  | RS0  | OV   | F1   | Р    |

| Table 6 | Description of Program Status Word (PSW) |

|---------|------------------------------------------|

|---------|------------------------------------------|

| MNEMONIC | BIT POSITION    | FUNCTION                                                                                                                                                                                                                                                                                               |

|----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CY       | PSW.7           | Carry flag.                                                                                                                                                                                                                                                                                            |

|          |                 | The Carry flag receives Carry-out from bit 7 of ALU. It is set to HIGH, when last arithmetic operation resulted in a carry (during addition) or borrow (during subtraction); otherwise, it is cleared to LOW by all arithmetic operations.                                                             |

| AC       | PSW.6           | Auxiliary Carry Flag.                                                                                                                                                                                                                                                                                  |

|          |                 | Auxiliary Carry Flag receives Carry-out from bit 3 of addition operands. It is set<br>to HIGH, when last arithmetic operation resulted in a carry into (during addition)<br>or borrow from (during subtraction) the high-order nibble; otherwise, it is cleared<br>to LOW by all arithmetic operations |

| F0       | PSW.5           | General purpose flag.                                                                                                                                                                                                                                                                                  |

|          |                 | This bit is uncommitted and may be used as general purpose status flag.                                                                                                                                                                                                                                |

| RS1, RS0 | PSW.4,<br>PSW.3 | Register Bank select control bits.                                                                                                                                                                                                                                                                     |

|          |                 | • RS1, RS0 = 00 selects register bank 0, address 00h ~ 07h.                                                                                                                                                                                                                                            |

|          |                 | • RS1, RS0 = 01 selects register bank 1, address 08h ~ 0Fh.                                                                                                                                                                                                                                            |

|          |                 | • RS1, RS0 = 10 selects register bank 2, address 10h ~ 17h.                                                                                                                                                                                                                                            |

|          |                 | • RS1, RS0 = 11 selects register bank 3, address 18h ~ 1Fh.                                                                                                                                                                                                                                            |

| OV       | PSW.2           | Overflow flag.                                                                                                                                                                                                                                                                                         |

|          |                 | This bit is set to HIGH, when last arithmetic operation resulted in a carry (addition), borrow (subtraction), or overflow (multiply or divide); otherwise, it is cleared to LOW by all arithmetic operation.                                                                                           |

| F1       | PSW.1           | General purpose flag.                                                                                                                                                                                                                                                                                  |

|          |                 | This bit is uncommitted and may be used as general purpose status flag.                                                                                                                                                                                                                                |

| Р        | PSW.0           | Parity flag.                                                                                                                                                                                                                                                                                           |

|          |                 | Set/Clear by hardware each instruction cycle to indicate an odd/even number of 1s in the accumulator, i.e., even parity.                                                                                                                                                                               |

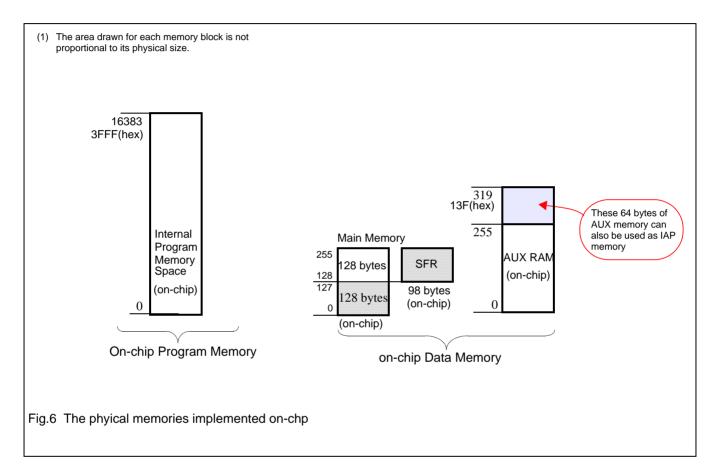

### 6 MEMORY ORGANIZATION

The STK6037 has 4 blocks of memory phyically implemented on-chip. These are:

- 16384 bytes of flash program memory,

- 256 bytes of Main Data Memory,

- 320 bytes of AUX memory, and

- 98 bytes of Special Function Register.

The following diagram shows the overall memory spaces available in the microcontroller.

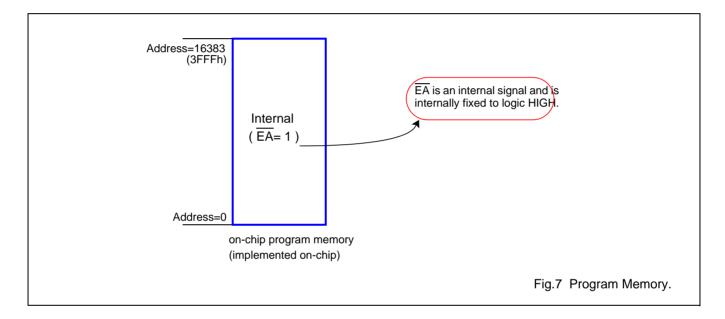

# 6.1 Program Memory

#### 6.1.1 PRORAM ROM SPACE

The STK6037 CPU can fetches instructions only from the 16K on-chip program memory. The memory adddress range is from 0000(hex) to 3FFF(hex). As Port 0 is not implemented, it is impossible to expand memory space by adding external memory.

### 6.1.2 ISP PRGRAMMING FOR THE 16K FLASH MEMORY

The on-chip program memory is implemented using flash memory, with ISP (In-System Programming) capability. Detailed description of ISP programming is given in another document.

### 6.1.3 ROM CODE PROTECTION

ROM code protection is implemented in the 16K flash memory.

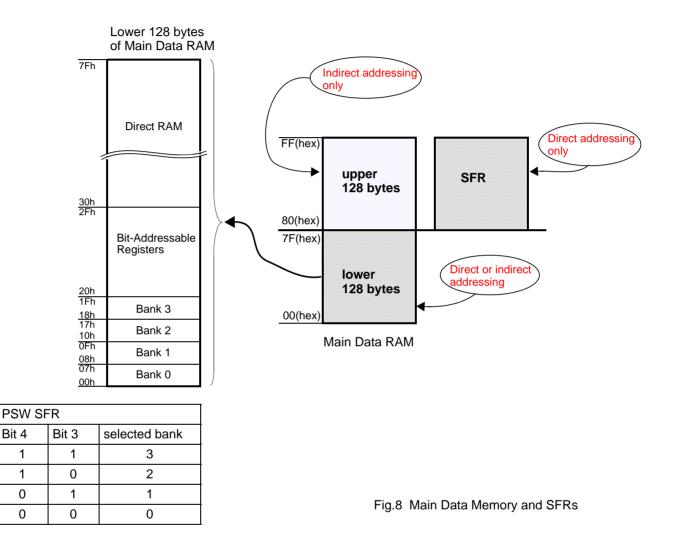

### 6.2 Main Data RAM and Special Function Register (SFR)

The STK6037 has 256 bytes of on-chip Main Data RAM and 98 bytes of SFR. Although the Main Data RAM and the SFRs shares overlapped memory space, they are two physically separate blocks. The upper 128 bytes of the Main Data RAM, from address 80H to FFH can be accessed only by **Indirect Addressing**. The lower 128 bytes of the Main RAM, from address 00H to 7FH, can be accessed by **Direct Addressing** or **Indirect Addressing**.

The SFRs occupy the address range from 80H to FFH and are only accessible using Direct Addressing.

### 6.2.1 THE LOWER 128 BYTES OF THE MAIN DATA RAM

The lower 128 bytes are organized as shown in Fig.8. The lower 32 bytes form 4 banks of eight registers (R0 - R7). Two bits on the Program Status Word (PSW) select which bank is active (in use). The next 16 bytes, from 20 (hex) to 2F (hex) , form a block of bit-addressable memory space, at bit address  $00(hex) \sim 07(hex)$ .

# 6.3 AUX Memory

#### 6.3.1 AUX MEMORY SPACE

The STK6037 has 320 bytes of auxiliary memory (AUX RAM) implemented on-chip. This memory can be accessed by use of MOVX instruction. It is not possible to expand the AUX memory space by adding off-chip memory, because Port 0 is not implemented.

The MOVX @Ri instruction, where i=0 or 1, can access only the lower 256-bytes of the on-chip AUX RAM. The MOVX @DTPR instruction can access all 320 bytes of AUX memory.

### 6.3.2 ON-CHIP AUX MEMORY

The on-chip AUX RAM from address 0 to address 319 can be accessed by the CPU as normal data memory, by performing a MOVX instructon. Read/Write access to this memory can be disabled by setting bit 4 of the SFR CHIPCON to LOW. Please refer to Table 3 and Table 4 for detailed description of the SFR CHIPCON.

When executing MOVX instruction from the 16K program memory, an access (read or write) to the 320-bytes AUX RAM do not affect the status of pin P3.7.

### 6.3.3 DUAL DATA POINTER (DATA POINTER 0 AND DATA POINTER 1) AND DPTR SELECT REGISTER (SFR DPS)

The STK6037 has two data pointers, Data Pointer 0 and Data Pointer 1. Data Pointer 0 is the traditional 8051 data pointer for MOVX instructions. Data Pointer 1 is an extra data pointer for fast moving a block of data. Before executing a MOVX instruction, an active data pointer must be selected by programming the Data Pointer Select Register (SFR DPS). Please refer to Table 7 for detailed description of SFR DPS.

| Address<br>(Hex) | R/W | SYMBOLS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                      | Reset Value |

|------------------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 82               | R/W | DPL0    | Data Pointer 0 Low (traditional 80C51 data pointer)                                                                                                                                                                                                                                                                                                                                                                              | 0000 0000   |

| 83               | R/W | DPH0    | Data Pointer 0 High (traditional 80C51 data pointer)                                                                                                                                                                                                                                                                                                                                                                             | 0000 0000   |

| 84               | R/W | DPL1    | Data Pointer 1 Low (extra data pointer), specific to the STK6037.                                                                                                                                                                                                                                                                                                                                                                | 0000 0000   |

| 85               | R/W | DPH1    | Data Pointer 1 High (extra data pointer), specific to the STK6037.                                                                                                                                                                                                                                                                                                                                                               | 0000 0000   |

| 86               | R/W | DPS     | DPTR Select Register (DPS), specific to the STK6037.<br>The DPS register has only one bit. Only its bit 0, called SEL bit,<br>is implemented on-chip. When SEL=0, instructions that use the<br>DPTR will use SFR DPL0 and SFR DPH0. When SEL=1,<br>instructions that use the DPTR will use SFR DPL1 and<br>SFR DPH1.<br>Bits 7~1 of SFR DPS can not be written to, and, when read,<br>always return a 0 for any of these 7 bits. | 0000 0000   |

| Table 7 | Data Daintar O. Data Daintar 1, and DDTD Calar  | + Decister |

|---------|-------------------------------------------------|------------|

| Table I | Data Pointer 0, Data Pointer 1, and DPTR Select | i register |

All DPTR-related instructions use the currently selected data pointer. To switch the active pointer, toggle the SEL bit, by use of the instruction INC DPS. The 6 instructions that use the DPTR are given in the following table. An active DPTR must be selected before executing these intructions.

# Table 8 Instructions that use the DPTR

| INSTRUCITON       | DESCRIPTION                                                |

|-------------------|------------------------------------------------------------|

| INC DPTR          | Increment the data pointer by1.                            |

| MOV DPTR, #data16 | Load the DPTR with a 16-bit constant.                      |

| MOVC A, @ A+DPTR  | Move code byte relative to DPTR to Accumulator (ACC).      |

| MOVX A, @DPTR     | Move AUX Memory byte (16-bit address) to Accumulator (ACC) |

| MOVX @DPTR, A     | Move ACC to AUX memory byte.                               |

| JMP @ A+DPTR      | Jump indirect relative to DPTR.                            |

# Table 9 Clock Control Register, SFR CKCON

#### Clock Control Register (SFR CKCON), located at 8E(hex) of the SFR map **Bit Address** Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 T2M T1M Reserved **Mnemonics** Reserved TOM Reserved Reserved Reset value 0 0 0 0 0 0 0 1

# Table 10 Description of the CKCON Register

| MNEMONIC | BIT<br>POSITION | FUNCTION                                                                                                                  |

|----------|-----------------|---------------------------------------------------------------------------------------------------------------------------|

| T2M      | CKCON.5         | Select Timer 2 clock frequecny.                                                                                           |

|          |                 | When T2M=0, Timer 2 uses (CPU CLK / 12) as clock frequency.                                                               |

|          |                 | When T2M=1, Timer 2 uses (CPU CLK / 4) as clock frequency.                                                                |

| T1M      | CKCON.4         | Select Timer 1 clock frequecny.                                                                                           |

|          |                 | When T1M=0, Timer 1 uses (CPU CLK / 12) as clock frequency.<br>When T1M=1, Timer 1 uses (CPU CLK / 4) as clock frequency. |

| TOM      | CKCON.3         | Select Timer 0 clock frequecny.                                                                                           |

|          |                 | When T0M=0, Timer 0 uses (CPU CLK / 12) as clock frequency.<br>When T0M=1, Timer 0 uses (CPU CLK / 4) as clock frequency. |

# 7 SPECIAL FUNCTION REGISTERS

The STK6037 has 98 Special Function Registers (SFR).

# 7.1 SFR allocation table

# Table 11 SFR allocation table

| F8 | EIP   | PWM0H  | PWM0L   | PWM1H   | PWM1L   | PWM2H    | PWM2L    |         |

|----|-------|--------|---------|---------|---------|----------|----------|---------|

| F0 | В     | PWM3H  | PWM3L   | PWM4H   | PWM4L   | PWM5H    | PWM5L    |         |

| E8 | EIE   | PWM6H  | PWM6L   | PWM7H   | PWM7L   | PWM8H    | PWM8L    |         |

| E0 | ACC   | WDT    | ISPSLV  | ISPEN   | IAPEN   | IAP_ADRL | IAP_ADRH |         |

| D8 | EICON |        | ADCSEL  | ADCVALH | ADCVALL |          |          |         |

| D0 | PSW   | P1_OPT | PWM_EA0 | PWM_EA1 | PWM_EA2 |          |          |         |

| C8 | T2CON | T2MOD  | RCAP2L  | RCAP2H  | TL2     | TH2      |          |         |

| C0 | SCON1 | SBUF1  |         |         |         |          |          |         |

| B8 | IP    | PWM9H  | PWM9L   | PWM10H  | PWM10L  | PWM11H   | PWM11L   | CHIPCON |

| B0 | P3    | PWM12H | PWM12L  | PWM13H  | PWM13L  | PWM13H   | PWM14L   | PCLKSEL |

| A8 | IE    | PWM15H | PWM15L  | PWM16H  | PWM16L  | PWM17H   | PWM17H   |         |

| A0 | P2    | PWM18H | PWM18L  | PWM19H  | PWM19L  | PWM20H   | PWM20L   |         |

| 98 | SCON0 | SBUF0  | TL3     | TH3     |         |          |          |         |

| 90 | P1    | EXIF   |         |         |         |          |          |         |

| 88 | TCON  | TMOD   | TL0     | TL1     | TH0     | TH1      | CKCON    |         |

| 80 | P0    | SP     | DPL0    | DPH0    | DPL1    | DPH1     | DPS      | PCON    |

# 7.2 SFR Map Overview (98 SFRs)

# Table 12 The SFR Map

| Address<br>(Hex) R/W |             | SYMBOLS        | DESCRIPTION                                                                                                                                                                                                     | Reset Value |  |

|----------------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| 80                   | R/W         | P0             | Port 0 output latch (bit-addressable). (not implemented, but reserved))                                                                                                                                         | 1111 1111   |  |

| 81                   | R/W         | SP             | Stack Pointer                                                                                                                                                                                                   | 0000 0111   |  |

| 82                   | R/W         | DPL0           | Data Pointer 0 Low (traditional 80C51 data pointer)                                                                                                                                                             | 0000 0000   |  |

| 83                   | R/W         | DPH0           | Data Pointer 0 High (traditional 80C51 data pointer)                                                                                                                                                            | 0000 0000   |  |

| 84                   | R/W         | DPL1           | Data Pointer 1 Low (extra data pointer), specific to the STK6037.                                                                                                                                               | 0000 0000   |  |

| 85                   | R/W         | DPH1           | Data Pointer 1 High (extra data pointer), specific to the STK6037.                                                                                                                                              | 0000 0000   |  |

| 86                   | R/W         | DPS            | DPTR Select Register (DPS), specific to the STK6037.                                                                                                                                                            | 0000 0000   |  |

| 87                   | R/W         | PCON           | Power Control Register.                                                                                                                                                                                         | 0011 0000   |  |

| 88                   | R/W         | TCON           | Timer0/1 Control Register (bit-addressable)                                                                                                                                                                     | 0000 0000   |  |

| 89                   | R/W         | TMOD           | Timer0/1 Mode Register                                                                                                                                                                                          | 0000 0000   |  |

| 8A                   | R/W         | TL0            | Timer0, Low byte                                                                                                                                                                                                | 0000 0000   |  |

| 8B                   | R/W         | TL1            | Timer1, Low byte                                                                                                                                                                                                | 0000 0000   |  |

| 8C                   | R/W         | TH0            | Timer0, High byte                                                                                                                                                                                               | 0000 0000   |  |

| 8D                   | R/W         | TH1            | Timer1, High byte                                                                                                                                                                                               | 0000 0000   |  |

| 8E                   | R/W         | CKCON          | Clock Control register, specific to the STK6037.<br>The register is for controlling the frequency of the clock added<br>to Timer 0, Timer 1, and Timer 2, and memory stretch cycle for<br>the MOVX instruction. | 0000 0001   |  |

| 8F                   | not used    |                |                                                                                                                                                                                                                 |             |  |

| 90                   | R/W         | P1             | Port 1 output latch (bit-addressable).                                                                                                                                                                          | 1111 1111   |  |

| 91                   | R/W         | EXIF           | Extended Interrupt Flag register                                                                                                                                                                                | 00001000    |  |

| 92                   | not used    |                |                                                                                                                                                                                                                 |             |  |

| 93, 94, 95           | , 96, 97, r | not implemente | d.                                                                                                                                                                                                              |             |  |

| 98                   | R/W         | SCON0          | UART0 (Serial Port 0) Control/Status Register (bit-addressable)                                                                                                                                                 | 0000 0000   |  |

| 99                   | R/W         | SBUF0          | UART0 (Serial Port 0) Buffer Register                                                                                                                                                                           | 0000 0000   |  |

| 9A                   | R/W         | TL3            | Timer 3 low byte.                                                                                                                                                                                               | 0000 0000   |  |

| 9B                   | R/W         | TH3            | Timer 3 high byte.                                                                                                                                                                                              | 0000 0000   |  |

| 9C, 9D, 9I           | E, 9F not   | used           |                                                                                                                                                                                                                 |             |  |

| A0                   | R/W         | P2             | Port 2 output latch (bit-addressable )                                                                                                                                                                          | 1111 1111   |  |

| A1                   | R/W         | PWM18H         | PWM18 high byte.                                                                                                                                                                                                | 1000 0000   |  |

| A2                   | R/W         | PWM18L         | PWM18 low byte.                                                                                                                                                                                                 | 00xx xxxx   |  |

| A3                   | R/W         | PWM19H         | PWM19 high byte.                                                                                                                                                                                                | 1000 0000   |  |

| A4                   | R/W         | PWM19L         | PWM19 low byte.                                                                                                                                                                                                 | 00xx xxxx   |  |

| A5                   | R/W         | PWM20H         | PWM20 high byte.                                                                                                                                                                                                | 1000 0000   |  |

| A6                   | R/W         | PWM20L         | PWM20 low byte.                                                                                                                                                                                                 | 00xx xxxx   |  |

| A7 not use           | ed.         |                |                                                                                                                                                                                                                 |             |  |

| A8                   | R/W         | IE             | Interrupt Enable Register (bit-addressable)                                                                                                                                                                     | 0000 0000   |  |

| Address<br>(Hex) | R/W SYMBOLS |                  | DESCRIPTION                                              | Reset Value |

|------------------|-------------|------------------|----------------------------------------------------------|-------------|

| A9               | R/W         | PWM15H           | PWM15 high byte.                                         | 1000 0000   |

| AA               | R/W         | PWM15L           | PWM15 low byte.                                          | 00xx xxxx   |

| AB               | R/W         | PWM16H           | PWM16 high byte.                                         | 1000 0000   |

| AC               | R/W         | PWM16L           | PWM16 low byte.                                          | 00xx xxxx   |

| AD               | R/W         | PWM17H           | PWM17 high byte.                                         | 1000 0000   |

| AE               | R/W         | PWM17L           | PWM17 low byte.                                          | 00xx xxxx   |

| AF not us        | ed.         | -                | -                                                        |             |

| B0               | R/W         | P3               | Port 3 output latch (bit-addressable)                    | 1111 1111   |

| B1               | R/W         | PWM12H           | PWM12 high byte.                                         | 1000 0000   |

| B2               | R/W         | PWM12L           | PWM12 low byte.                                          | 00xx xxxx   |

| B3               | R/W         | PWM13H           | PWM13 high byte.                                         | 1000 0000   |

| B4               | R/W         | PWM13L           | PWM13 low byte.                                          | 00xx xxxx   |

| B5               | R/W         | PWM14H           | PWM14 high byte.                                         | 1000 0000   |

| B6               | R/W         | PWM14L           | PWM14 low byte.                                          | 00xx xxxx   |

| B7               | R/W         | PCLKSEL          | PWM clock frequency setting                              | 0000 0000   |

| B8               | R/W         | IP               | Interrupt Priority Register (bit-addressable)            | 1000 0000   |

| B9               | R/W         | PWM9H            | PWM9 high byte.                                          | 1000 0000   |

| BA               | R/W         | PWM9L            | PWM9 low byte.                                           | 00xx xxxx   |

| BB               | R/W         | PWM10H           | PWM10 high byte.                                         | 1000 0000   |

| BC               | R/W         | PWM10L           | PWM10 low byte.                                          | 00xx xxxx   |

| BD               | R/W         | PWM11H           | PWM11 high byte.                                         | 1000 0000   |

| BE               | R/W         | PWM11L           | PWM11 low byte.                                          | 00xx xxxx   |

| BF               | R/W         | CHIPCON          | Chip Configuration Register                              | x001 x000   |

| C0               | R/W         | SCON1            | UART1 (ie., Serial Port 1) Control/Status Register       | 0000 0000   |

| C1               | R/W         | SBUF1            | UART1 (ie., Serial Port 1) Buffer Register               | 0000 0000   |

| C2, C3, C        | 4, C5, C    | 6, C7, not used. |                                                          |             |

| C8               | R/W         | T2CON            | Timer 2 Control Register (bit-addressable)               | 0000 0000   |

| C9               | R/W         | T2MOD            | Timer 2 Mode Control Register                            | 0000 xxx1   |

| CA               | R/W         | RCAP2L           | Timer 2 Reload Capture Register, Low byte                | 0000 0000   |

| СВ               | R/W         | RCAP2H           | Timer 2 Reload Capture Register, High byte               | 0000 0000   |

| CC               | R/W         | TL2              | Timer 2, Low byte                                        | 0000 0000   |

| CD               | R/W         | TH2              | Timer 2, High byte                                       | 0000 0000   |

| CE, CF no        | ot used.    |                  |                                                          |             |

| D0               | R/W         | PSW              | Program Status Word Register (bit-addressable)           | 0000 0000   |

| D1               | R/W         | P1_OPT           | Selecting Port 1 pin function, as Port or ADC input pin. | xxxx 0000   |

| D2               | R/W         | PWM_EA0          | Enable PWM 0~7 outputs.                                  | 0000 0000   |

| D3               | R/W         | PWM_EA1          | Enable PWM 8~15 outputs.                                 | 0000 0000   |

| D4               | R/W         | PWM_EA2          | Enable PWM 16~20 outputs.                                | xxx0 0000   |

| D5, D6, D        | 7not use    | d.               |                                                          | I           |

| D8               | R/W         | EICON            | Extended Interrupt Control register.                     | 0000 0000   |

| D9 not us        |             |                  | 1 · · ·                                                  |             |

| DA               | R/W         | ADCSEL           | Select a channel as ADC input and enable ADC             | 0xx0 0000   |

| Address<br>(Hex) | R/W       | SYMBOLS  | DESCRIPTION                                                        | Reset Value  |

|------------------|-----------|----------|--------------------------------------------------------------------|--------------|

| DB               | R         | ADCVALH  | Buffer for storing the upper 8 bits (Bits 9 ~ 2)of the 10-bit ADC. | 0000 0000    |

| DC               | R         | ADCVALL  | Buffer for storing the lower 2 bits (Bits 1 ~ 0) of the 10-bit ADC | xxxxxx00     |

| DD, DE, D        | DF not us | sed.     |                                                                    | 1            |

| E0               | R/W       | ACC      | Accumulator (bit-addressable)                                      | 0000 0000    |

| E1               | R/W       | WDT      | Watchdog Timer Control.                                            | 00xx x000    |

| E2               | R/W       | ISPSLV   | ISP Control Slave address                                          | 0000 0000    |

| E3               | R/W       | ISPEN    | ISP Enable register (write 93hex to enable the ISP mode)           | 0000 0000    |

| E4               | R/W       | IAPEN    | IAP ENable register.                                               | 0000 x x x x |

| E5               | R/W       | IAP_ADRL | Low-byte address of the flash memory location for IAP.             | 0000 0000    |