## CPE/EE 421 Microcomputers

**WEEK #10**

# Interpreting the Timing Diagram

The 68000 Read Cycle

### The Clock

1

5

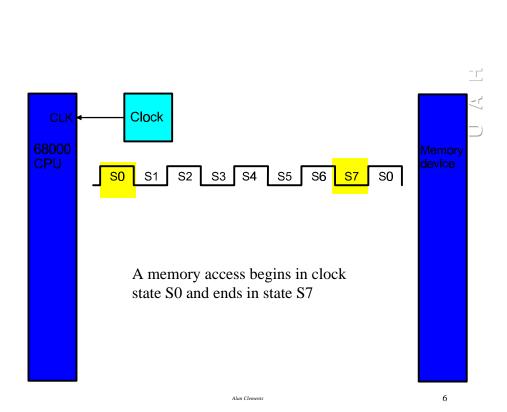

- A microprocessor requires a clock that provides a stream of timing pulses to control its internal operations

- A 68000 memory access takes a minimum of eight clock states numbered from clock state S0 to clock state S7

#### Address Timing

-1

9

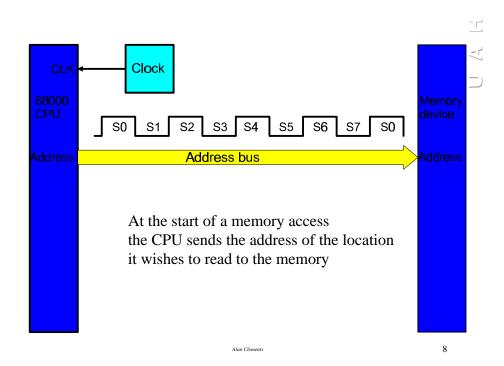

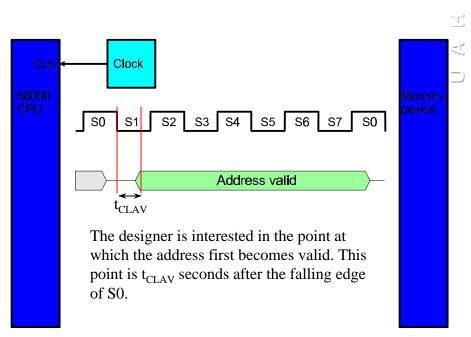

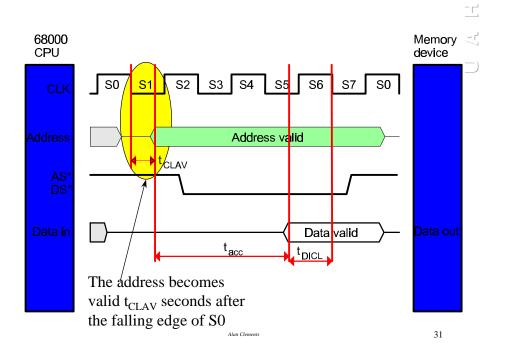

- We are interested in when the 68000 generates a new address for use in the current memory access

- The next slide shows the relationship between the new address and the state of the 68000's clock

# Address Timing

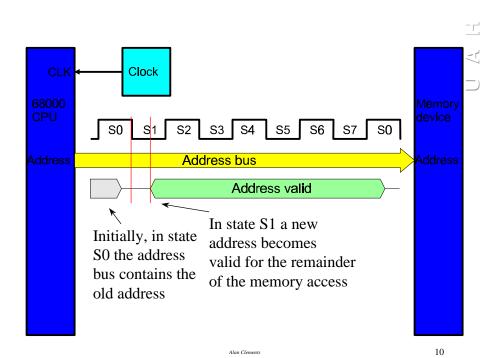

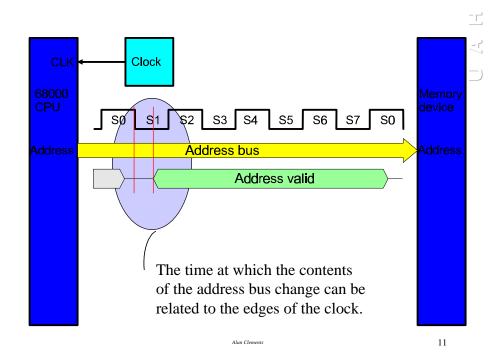

- Let's look at the sequence of events that govern the timing of the address bus

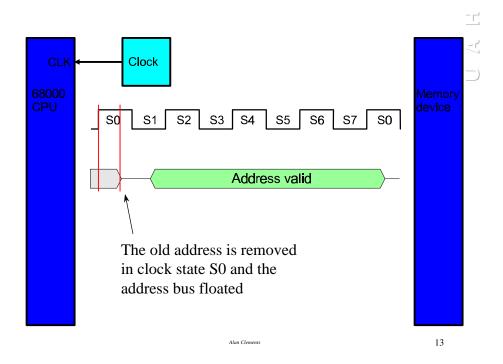

- The "old" address is removed in state S0

- The address bus is floated for a short time, and the CPU puts out a new address in state S1

Alan Clements

$\leq$

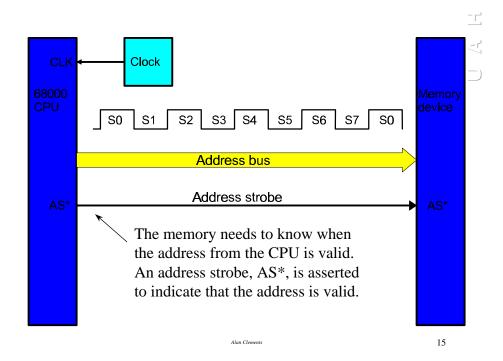

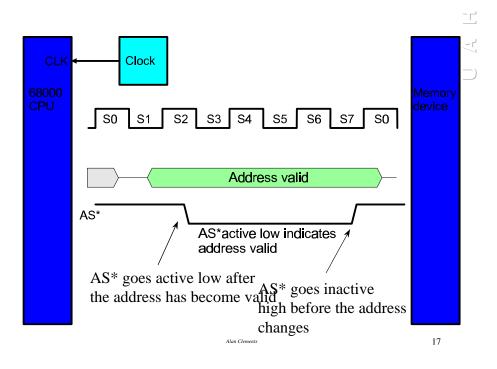

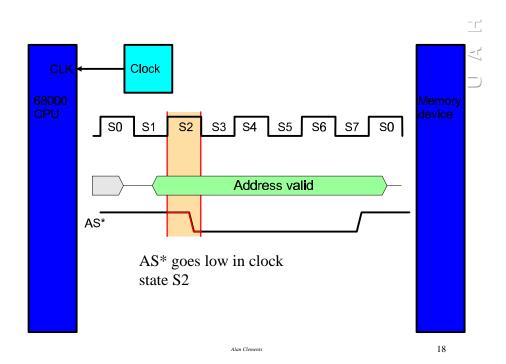

#### Address and Address Strobe

- We are interested in the relationship between the time at which the address is valid and the time at which the address strobe, AS\*, is asserted

- When AS\* is *active-low* it indicates that the address is valid

- We now look at the timing of the clock, the address, and the address strobe

Alan Clements

16

$\supset$

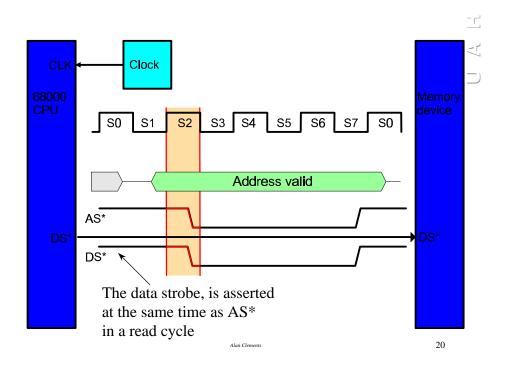

#### The Data Strobes

1

19

- The 68000 has two data strobes LDS\* and UDS\*. These select the lower byte or the upper byte of a word during a memory access

- To keep things simple, we will use a single data strobe, DS\*

Alan Clements

• The timing of DS\* in a read cycle is the same as the address strobe, AS\*

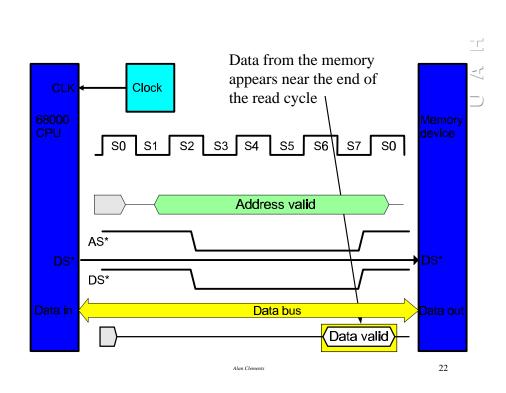

#### The Data Bus

-1

21

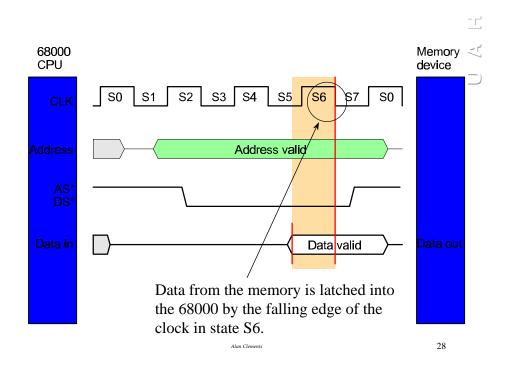

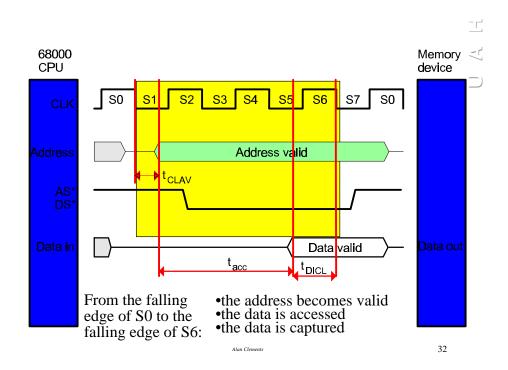

- During a read cycle the memory provides the CPU with data

- The next slide shows the data bus and the timing of the data signal

- Note that valid data does not appear on the data bus until near the end of the read cycle

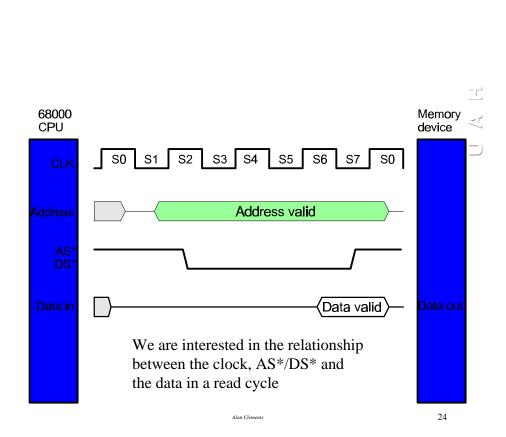

### Analyzing the Timing Diagram

-1

23

- We are going to redraw the timing diagram to remove clutter

- We aren't interested in the signal paths themselves, only in the relationship between the signals

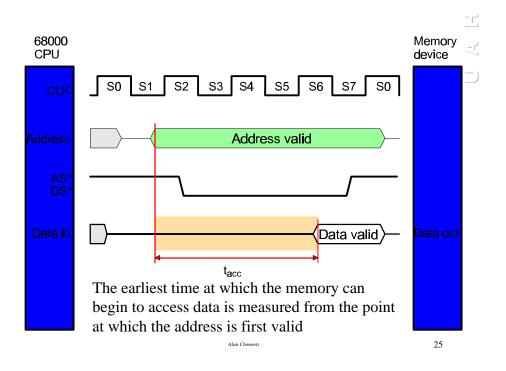

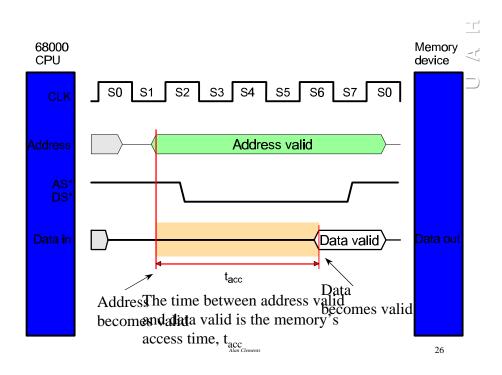

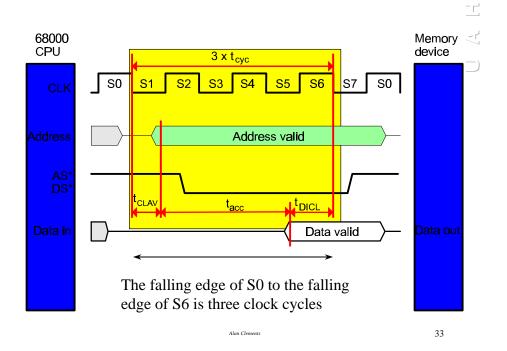

#### Calculating the Access Time

1

—)

27

- We need to calculate the memory's access time

- By knowing the access time, we can use the appropriate memory component

- Equally, if we select a given memory component, we can calculate whether its access time is adequate for a particular system

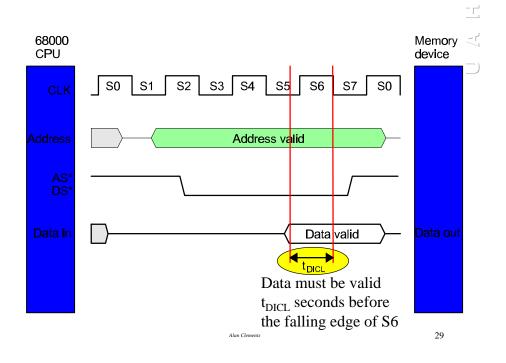

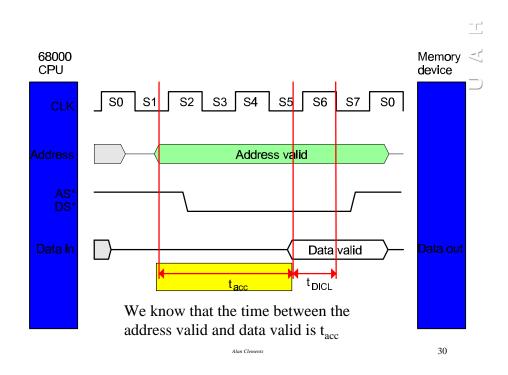

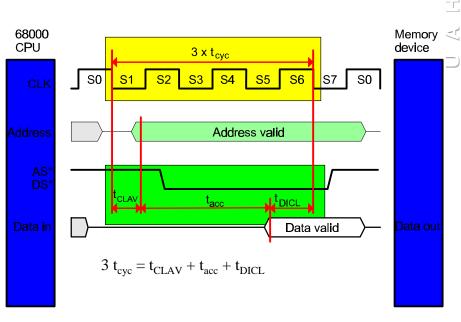

# Timing Example

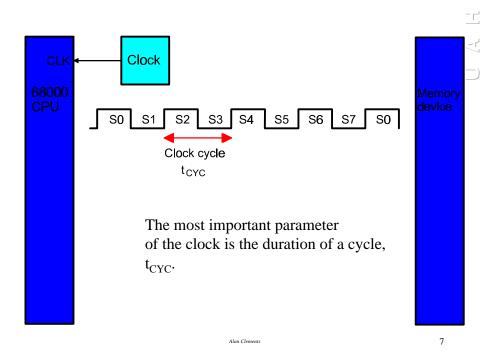

- 68000 clock 8 MHz  $t_{CYC} = 125 \text{ ns}$

- 68000 CPU  $t_{CLAV} = 70 \text{ ns}$

- 68000 CPU  $t_{DICL} = 15 \text{ ns}$

Alan Clements

- What is the minimum  $t_{acc}$ ?

- $3 t_{CYC} = t_{CLAV} + t_{acc} + t_{DICL}$

- $375 = 70 + t_{acc} + 15$

- $t_{acc} = 290 \text{ ns}$

#### 35