# MachXO 培训教程 2005年8月

英文网址: <a href="http://www.latticesemi.com">http://www.latticesemi.com</a>

中文网址: <a href="http://www.latticesemi.com.cn">http://www.latticesemi.com.cn</a>

或

http://www.lattice.com.cn

# MachX0 系列

MachXO 系列是新一代的跨越式可编程逻辑器件,支持传统上由高密度的 CPLD 或者低容量的 FPGA 所实现的应用,并且拥有更全面和高性能价格比的结构和工艺。通过采用 130nm 的非易失性嵌入式 Flash 处理工艺,以及用于逻辑实现的业界标准,4-输入查找表(LUT)的方法,这些新的器件能让系统设计者在单位逻辑功能上降低 50%的成本,而且在特性上有了很大的提升。

MachXO 器件不仅能用来处理传统的 CPLD 应用,在该系列的所有成员中都增加了分布式存贮器、一种低待机功耗的睡眠模式以及通过莱迪思特有的 TransFR 技术来透明地更新逻辑配置的功能。此外,在较大的系列成员中,增加了对嵌入式 RAM (EBR) 和锁相环 (PLL) 时钟电路以及 PCI 和 LVDS I/O 的支持,提供了通常仅在传统的 FPGA 结构中才有的功能。与此同时,还保留了莱迪思前几代 CPLD (如流行的 MACH®器件)的瞬时上电、单片和高速的优点。

MachXO 逻辑器件建立在低成本的 130nm 嵌入式 Flash 处理工艺上。它能够在单芯片中瞬时工作,这种特性对于许多 CPLD 应用来说是十分重要的。高达3.5ns 的管脚至管脚的延时使得器件能够满足当代系统设计的高速要求。MachXO 有两种类型, "E"型和 "C"型。 "E"型 MachXO 器件采用了 1.2V 逻辑核技术,适用于超低功耗的应用。一个片上的电压调整器使得 "C"型MachXO 器件可以支持 1.8V, 2.5V 或 3.3V 的外部电压,从而支持传统的系统电源要求。

在每个器件的内核中是一个查找表阵列,可以用来实现逻辑和小型的分布式存储器。这个阵列被灵活的 I/0 所包围,这些 I/0 能够实现多种流行的 I/0 标准,如 LVCMOS。在大一些的器件中,还支持 PCI 和 LVDS。

器件的睡眠模式可减少 100 倍的待机功耗,支持那些要求低功耗的应用。该器件还支持莱迪思特有的 TransFR (透明的现场重新配置) 技术,能够在器件使用 SRAM 配置存储器继续正常工作的情况下,对 Flash 配置存储器进行透明的编程。新的配置可以方便地在数毫秒中从 Flash 下载到 SRAM 块中。TransFR 技术使得器件能在不严重中断系统运行的情况下实现更新,确保了现场逻辑更新的灵活性。

#### 应用

MachXO 器件适用于多种功能的实现,诸如总线桥接、接口、控制逻辑、时钟管理、电源及复位控制、粘合逻辑、存储器控制以及 ASIC 和 FPGA 配置。这些应用能广泛地用于多种终端市场,包括汽车、消费品、通信、计算、工业、医疗、军用和网络市场。

#### 器件的主要特性

- 非易失, 无限次重构

- 瞬时上电,数微秒

- -单片, 无外部配置存储器

- 很高的设计安全性,不能截取位流

- 用数毫秒重构基于 SRAM 的逻辑

- 通过系统配置和 JTAG 口对 SRAM 和非易失存储器编程

- 支持非易失存储器的后台编程

- 睡眠模式 静态电流减小 100 倍

- TransFR 重构 系统正常工作时,可进行现场更新逻辑

- 大量 I/0

- 256 到 2280 查找表

- 73 到 271 个 I/O, 有多种封装选择

- 支持密度迁移

- 无铅的、符合 RoHS 标准的封装

- 嵌入式和分布式存储器

- 27Kbits sysMEM 嵌入式 RAM 块

- 7.7Kbits 分布式 RAM

- 专用 FIFO 控制逻辑

- 灵活的 I/0 缓冲器

可编程 sysIO 缓冲器支持多种接口

- LVCMOS 3.3/2.5/1.8/1.5/1.2

- LVTTL

- PCI

- LVDS、Bus-LVDS、LVPECL和RSDS

- 系统时钟 PLL

- 多达两个模拟 PLL

- 能够进行时钟分频、倍频和相移

- 系统级的支持

- IEEE 标准 1149.1 边界扫描, 具有 ispTRCY 内部逻辑分析仪功能

- 片内振荡器

- 器件的电源电压为 3.3V、2,5V、1.8V 或 1.2V

- 符合 IEEE 1532 在系统编程标准

- 表 1 为 MachXO 系列产品选择指南。

| Device                              | LCMXO256         | LCMXO640         | LCMXO1200        | LCMXO2280        |

|-------------------------------------|------------------|------------------|------------------|------------------|

| LUTs                                | 256              | 640              | 1200             | 2280             |

| Dist. RAM (Kbits)                   | 2.0              | 6.1              | 6.4              | 7.7              |

| EBR SRAM (Bits)                     | 0                | 0                | 9216             | 27648            |

| Number of EBR SRAM Blocks (9 Kbits) | 0                | 0                | 1                | 3                |

| V <sub>CC</sub> Voltage             | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V | 1.2/1.8/2.5/3.3V |

| Number of PLLs                      | 0                | 0                | 1                | 2                |

| Max. I/O                            | 78               | 159              | 211              | 271              |

| Packages                            |                  |                  |                  |                  |

| 100-pin TQFP (14x14 mm)             | 78               | 74               | 73               | 73               |

| 144-pin TQFP (20x20 mm)             |                  | 113              | 113              | 113              |

| 100-ball csBGA (8x8 mm)             | 78               | 74               |                  |                  |

| 132-ball csBGA (8x8 mm)             |                  | 101              | 101              | 101              |

| 256-ball fpBGA/ftBGA (17x17 mm)     |                  | 159              | 211              | 211              |

| 324-ball ftBGA (19x19 mm)           |                  |                  |                  | 271              |

表 1 MachX0 系列产品选择指南

MachXO 能满足 CPLD 和低容量 FPGA 应用的需求,例如: 粘合逻辑、总线桥接、上电控制以及控制逻辑。在单个芯片上集成了 CPLD 和 FPGA 的最佳特性。

借助莱迪思的 ispLEVER<sup>®</sup>设计工具可以使 MachXO 系列高效地实现大型复杂设计。支持 MachXO 的综合库适用于流行的逻辑综合工具。 ispLEVER 工具采用综合工具的输出结果,并且配合软件中的 floor planning 工具的约束条件,在 MachXO 器件中进行布局布线。 ispLEVER 工具从布线中提取时序信息,并将它们反注到设计中来进行时序验证。

#### 器件结构

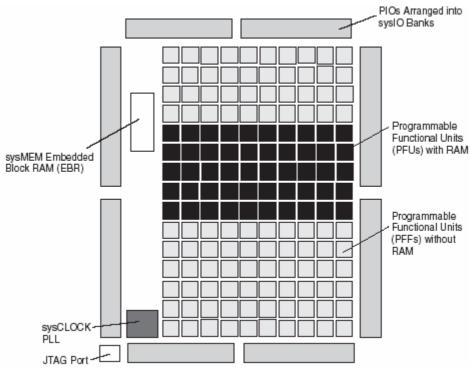

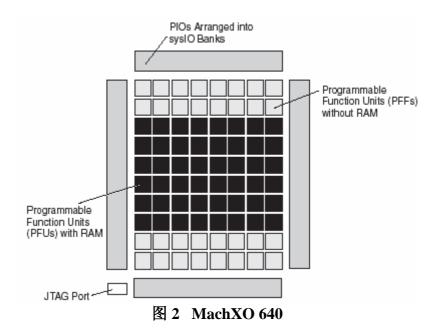

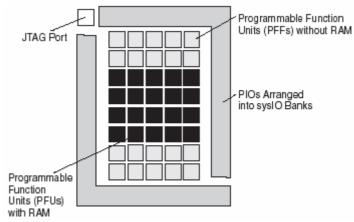

MachXO 系列器件的中间是逻辑块阵列,器件的四周是可编程 I/O 单元 (Program I/O ,简称 PIO)。这个系列中的有些器件有 sysCLOCK PLL 和 sysMEM Embedded Block RAM (EBR)。图 1、2、3 展示了此系列中的各种器件。

逻辑块以行和列的形式来排列。EBR 块放在逻辑阵列左边的列中。PIO 分布在器件的外围。PIO 利用灵活的、被称为 sysIO 接口的 I/O 缓冲器来支持各种接口标准。这些块连接到许多垂直的和水平的布线通道资源。布局和布线软件工具自动地分配这些布线资源。

器件中有两种逻辑块:可编程功能单元 (Programmable Function Unit, 简称 PFU); 无 RAM 的可编程功能单元 (Programmable Function Unit without RAM, 简称 PFF)。 PFU 包含用于逻辑、算法、RAM/ROM 和寄存器的积木块。 PFF 包含用于逻辑、算法、ROM 的积木块。 优化的 PFU 和 PFF 能够灵活、有效地实现复杂设计。逻辑块以二维的阵列形式分布。器件中每行为一种类型的积木块。

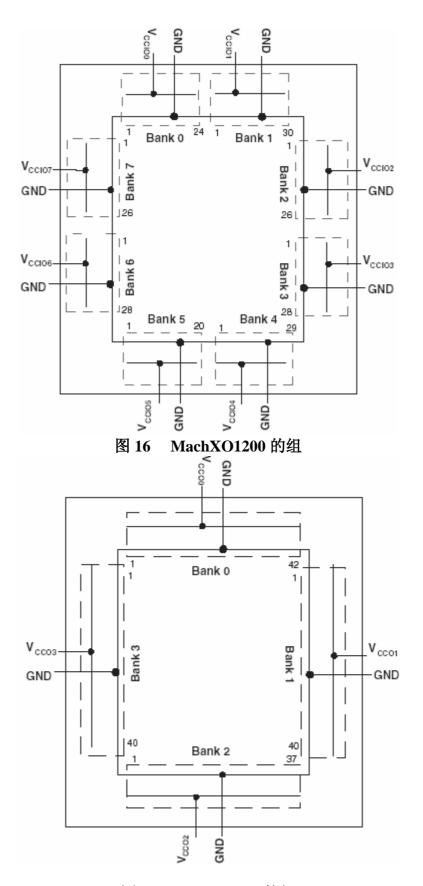

MachXO 系列中,组 (bank) 的数目根据器件而定。不同的组有着不同类型的 I/O 缓冲器。SysMEM EBR 是大的、专用快速存储器块,仅在较大的器件中有这些块,可以配置成 RAM、ROM 或 FIFO。FIFO 支持包括专用的 FIFO 指针,以及用于 LUT 使用最小化的标志"硬"控制逻辑。

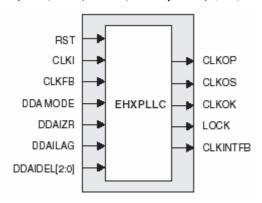

较大的 MachXO 结构提供多达 2 个 sysCLOCK 锁相环 (PLL)。这些块分布在存储器块的末端。PLL 有倍频、分频和相移功能,用来管理时钟的相位关系。

系列中的每种器件都有 JTAG 端口,支持编程、器件的配置和访问用户逻辑。MachXO 器件能工作于 3.3V、2.5V、1.8V 和 1.2V 的电压, 易于集成至整个系统。

图 1 MachXO 1200

图 3 MachXO 256

#### PFU 和 PFF 块

MachXO 器件的核心是 PFU 和 PFF。 PFU 可以通过编程实现逻辑、算法、分布式 RAM、分布式 ROM 功能。 PFF 可以通过编程实现逻辑、算法、 ROM 功能。除非特别说明,本文接下来不再区分 PFU 和 PFF,都简称为 PFU。

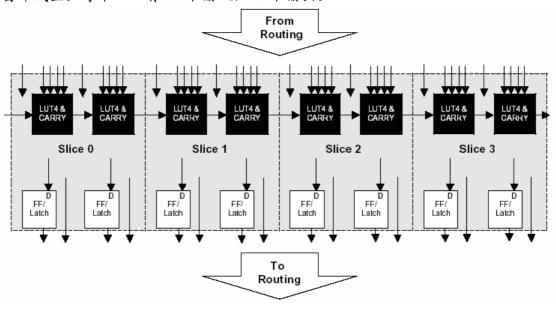

每个 PFU 由 4 个互联的 slice 组成,如图 4 所示。所有与 PFU 的互联都来自布线区。每个 PFU 有 53 个输入,25 个输出。

图 4 PFU 的结构

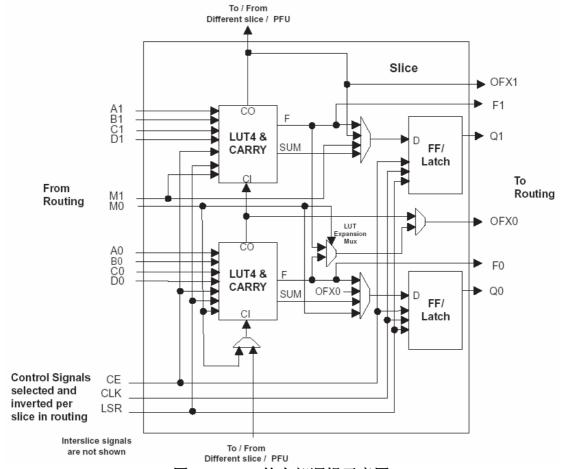

#### **Slice**

每个 slice 有两个 LUT4 查找表,其输出送入两个寄存器,这两个寄存器可以通过编程成为触发器或者锁存器模式。LUT 与相关的逻辑组合在一起可形成 LUT5、LUT6、LUT7 和 LUT8。器件中的控制逻辑执行 set/reset 功能(可编程为同步、异步模式)、时钟选择、片选和多种 RAM/ROM 功能。图 5 为 slice的内部逻辑示意图。Slice 内的寄存器可配置成正/负和边沿/电平时钟。有 14

个输入信号,13个来自布线区,一个来自邻近的 slice 或 PFU 的进位链。有7个输出,6个至布线区,一个至邻近 PFU 的进位链。

图 5 slice 的内部逻辑示意图

## Slice 的工作模式

每个 slice 都能实现四种模式:逻辑、行波、RAM 和 ROM。在 PFF 中的 slice 可实现除 RAM 外的其余模式。表 2 列出了 slice 实现的各种模式。

|           | Logic              | Ripple                | RAM     | ROM         |

|-----------|--------------------|-----------------------|---------|-------------|

| PFU Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | SPR16x2 | ROM16x1 x 2 |

| PFF Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | N/A     | ROM16x1 x 2 |

表 2 Slice 的工作模式

#### 1. 逻辑模式

在这种模式中,每个 slice 的 LUT 配置成 4 输入的组合逻辑查找表。 一个 LUT4 有 16 种可能的输入组合。通过编程可以产生有 4 输入的任意逻辑 功能。每个 slice 中有两个 LUT4。在一个 slice 内可构成 LUT5。较大的查 找表诸如 LUT6、LUT7、LU8 可用级连 slice 而构成。

## 2. 行波模式

此方式能够有效地实现较小的算术功能。每个 slice 能完成如下功能。

- 2位加

- 2位减

- 使用动态控制的 2 位加/减

- 2位加法计数器

- 2位减法计数器

- 行波模式乘法器积木块

- 有 A 和 B 两组输入的比较功能

- A 大于等于 B

- A 不等于 B

- A 小于等于 B

在这种模式中还有另外两个信号:进位和进位传递,允许级连的 slice 实现快速的算术功能。

#### 3. RAM 模式

可用每个 LUT 块构成 16X1 位存储器的分布式 RAM。多个 LUT 和 slice 的组合可构成各种不同的存储器。

莱迪思的软件支持构成各种大小的存储器。表 3 说明了实现不同类型的存储器所需要的 slice 数目。图 6 为分布式存储器组件图。双口 RAM 需要用两个 slice,一个 slice 用作读写口,另一个用作只读口。

|                  | SPR16x2 | DPR16x2 |

|------------------|---------|---------|

| Number of slices | 1       | 2       |

Note: SPR = Single Port RAM, DPR = Dual Port RAM

表 3 实现不同类型的存储器所需要的 slice 数目

图 6 分布式存储器组件

# 4. ROM 模式

ROM 模式与 RAM 模式相似,只是少了写端口。在 ROM 中预置数据是通过配置期间编程接口来完成的。

# PFU 的工作模式

一个 PFU 中的几个 Slices 可以合起来实现更大的功能。表 4 列出了 PFU 的几种工作模式。

| Logic                      | Ripple            | RAM <sup>1</sup>           | ROM         |

|----------------------------|-------------------|----------------------------|-------------|

| LUT 4x8 or<br>MUX 2x1 x 8  | 2-bit Add x 4     | SPR16x2 x 4<br>DPR16x2 x 2 | ROM16x1 x 8 |

| LUT 5x4 or<br>MUX 4x1 x 4  | 2-bit Sub x 4     | SPR16x4 x 2<br>DPR16x4 x 1 | ROM16x2 x 4 |

| LUT 6x 2 or<br>MUX 8x1 x 2 | 2-bit Counter x 4 | SPR16x8 x 1                | ROM16x4 x 2 |

| LUT 7x1 or<br>MUX 16x1 x 1 | 2-bit Comp x 4    |                            | ROM16x8 x 1 |

<sup>1.</sup> These modes are not available in PFF blocks

表 4 PFU 的工作模式

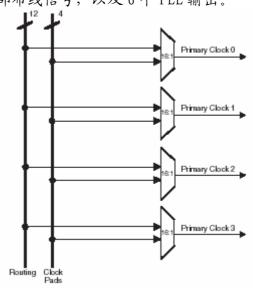

# 时钟/控制分布网络

MachX0 提供全局信号: 4个主时钟和 4个次级时钟。主时钟信号由 4个16:1 多路器产生,如图 7,8 所示。 MachX0256 和 MachX0640 有 4 个双功能时钟引脚,以及 12 个内部布线信号。MachX01200 和 MachX02280 有 4 个双功能时钟引脚,以及 6 个内部布线信号,以及 6 个 PLL 输出。

图 7 MachXO256 和 MachXO640 的主时钟

图 8 MachXO1200 和 MachXO2280 的主时钟

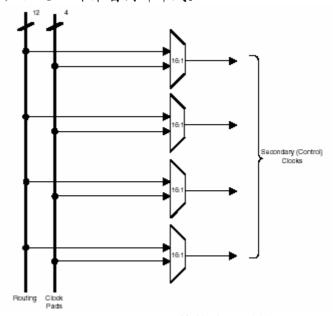

4个次级时钟由4个16:1多路器产生,如图 9所示。4个次级时钟源来自双功能时钟引脚,以及12个来自内部布线。

图 9 MachXO 器件的次级时钟

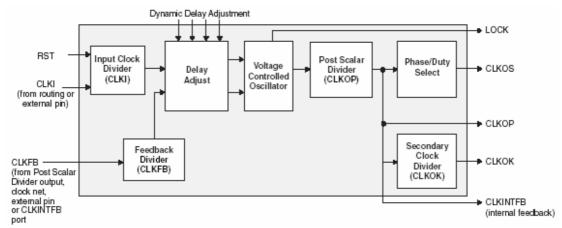

## 系统时钟锁相环

MachX01200 和 MachX02280 提供 PLL 支持。自引脚和布线区的时钟送至 PLL 的输入时钟分频器,有 4 个反馈信号送至反馈分频器,它们来自时钟网络、后定标分频器、布线区和外部引脚。PLL\_LOCK 信号用来指出 VCO 已经锁定输入信号。图 10 为系统时钟锁相环的方框图。

图 10 系统时钟锁相环的方框图

器件的建立和保持时间可以通过两种方式来改进: 在反馈中对延时进行编程; 或者在 PLL 的输入路径中相对于输入时钟提前或者延迟输出时钟。延时可以在配置期间配置或者动态调整。

系统时钟锁相环有综合时钟频率的能力。每个 PLL 有 4 个分频器:输入时钟分频器、反馈分频器、后定标分频器和次级时钟分频器。输入时钟分频器用于分频输入时钟信号,反馈分频器用于倍频输入信号,后定标分频器允许 VCO以高于输出时钟的频率运行,因此扩展了频率范围。次级时钟分频器用于得到较低的频率输出。PPL 的组件如图 11 所示。表 5 对各种 PLL 信号进行了描述。

图 11 PLL 的组件

| Signal       | I/O | Description                                                                 |  |

|--------------|-----|-----------------------------------------------------------------------------|--|

| CLKI         | I   | Clock input from external pin or routing                                    |  |

| CLKFB        | I   | PLL feedback input from PLL output, clocknet, routing or external pin       |  |

| RST          | I   | "1" to reset input clock divider                                            |  |

| CLKOS        | 0   | PLL output clock to clock tree (phase shifted/duty cycle changed)           |  |

| CLKOP        | 0   | PLL output clock to clock tree (No phase shift)                             |  |

| CLKOK        | 0   | PLL output to clock tree through secondary clock divider                    |  |

| LOCK         | 0   | "1" indicates PLL LOCK to CLKI                                              |  |

| DDAMODE      | I   | Dynamic Delay Enable. "1" Pin control (dynamic), "0": Fuse Control (static) |  |

| DDAIZR       | I   | Dynamic Delay Zero. "1": delay = 0, "0": delay = on                         |  |

| DDAILAG      | I   | Dynamic Delay Lag/Lead. "1": Lag, "0": Lead                                 |  |

| DDAIDEL[2:0] | I   | Dynamic Delay Input                                                         |  |

| DDAOZR       | 0   | Dynamic Delay Zero Output                                                   |  |

| DDAOLAG      | 0   | Dynamic Delay Lag/Lead Output                                               |  |

| DDAODEL[2:0] | 0   | Dynamic Delay Output                                                        |  |

表 5 PLL 信号的描述。

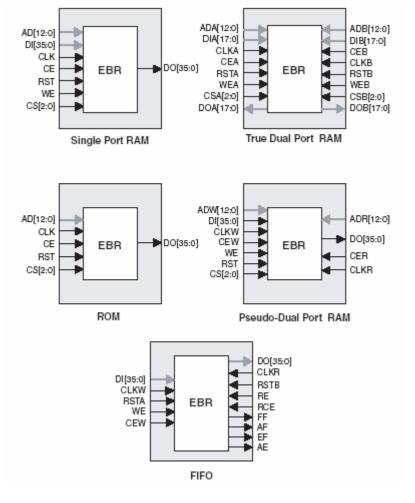

# 系统存储器(sysMEM Memory)

MachX01200和 MachX02280器件含有若干个嵌入式 RAM 块(EBR), EBR 可组成 9K 位的 RAM,并有专用输入和输出寄存器。系统存储器块可构成单口、双口、准双口存储器或 FIFO,每个块可构成不同的深度和宽度,如表 6 所示。

| Memory Mode      | Configurations                                                           |

|------------------|--------------------------------------------------------------------------|

| Single Port      | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

| True Dual Port   | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18             |

| Pseudo Dual Port | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

| FIFO             | 8,192 x 1<br>4,096 x 2<br>2,048 x 4<br>1,024 x 9<br>512 x 18<br>256 x 36 |

表 6 sysMEM 块的配置

# 单口、双口、准双口以及 FIFO 模式

图 12 展示了 5 种基本的存储器配置,在所有的系统 RAM 模式中,对于端口的输入数据和地址在存储器的输入端是锁存的。存储器的输出数据是否锁存是可选的。

图 12 sysMEM EBR 组件

EBR 存储器支持对双口模式的三种写操作:

- 1. 常规: 输出的数据仅在读周期出现,在写周期,数据(当前地址)不出现在输出。

- 2. 写完成:输入数据出现在相同端口的输出。

- 3. 写前的读:新的数据写入时,地址的旧内容出现在输出。

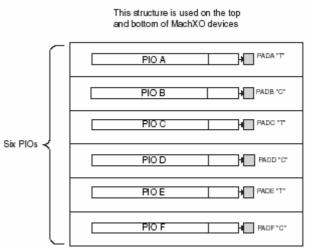

## PIO 群 (PIO Group)

在MachX0系列器件的组(bank)中,有两个PIO群。有6个PIO的一个群连到各自的sysyIO缓冲器,这个群位于底部和顶部的组。有4个PIO的一个群连到各自的sysyIO缓冲器,这个群位于左边和右边的组。SysIO缓冲器连接到各自的焊盘。

在这些群中,两个相邻的PIO可组成一个互补的I/O对,分别用T和C标出。MachX01200和MachX02280器件四边的相邻PIO为差分接收器。 MachX01200和MachX02280器件左边及右边一半的PIO可配置成LVDS发送、接

收对。其余的PIO为具有互补I/O性能的单端缓冲器。此外,MachX01200和MachX02280的顶部组提供PCI支持。

# Four PIOS PIO D PADO 'C' PIO D PADO 'C' PADO 'C'

图 13 4个可编程 I/O 组成的群

图 14 6个可编程 I/O 组成的群

# MachXO 支持的标准

MachXO sys IO 支持单端和差分标准。单端标准可以进一步分为 LVCMOS,LVTTL 和其它标准。缓冲器支持 LVTTL、LVCMOS 1.2、1.5、1.8、2.5 和 3.3V 标准。在 LVCMOS 和 LVTTL 模式下,缓冲器有独立的配置选项,例如总线保持(弱上拉、弱下拉、总线保持锁存),以及开漏特性。所有器件均支持 BLVDS 和 LVPECL 输出仿效。

在 MachX01200 和 MachX02280 的左边和右边区中,大约 50%的 I/0 支持 LVDS 输出。所有 MachX01200 和 MachX02280 的区都支持 LVDS、BLVDS 和 LVPECS 差分接收标准。MachX01200 和 MachX02280 器件顶部的区支持 PCI。下面的表 7 总结了 MachX0 系列器件的 I/0 特性。

|                                             | MachXO256                                                              | MachXO640                                                              | MachXO1200                                                                                                                                | MachXO2280                                                                                                                                |

|---------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Number of I/O Banks                         | 2                                                                      | 4                                                                      | 8                                                                                                                                         | 8                                                                                                                                         |

| Type of Input Buffers                       | Single-ended<br>(all four sides)                                       | Single-ended<br>(all four sides)                                       | Single-ended<br>(all four sides)<br>Differential Receivers<br>(all four sides)                                                            | Single-ended<br>(all four sides)<br>Differential Receivers<br>(all four sides)                                                            |

| Types of Output Buffers                     | Single-ended buffers<br>with complementary<br>outputs (all four sides) | Single-ended buffers<br>with complementary<br>outputs (all four sides) | Single-ended buffers with complementary outputs (all four sides) Differential buffers with true LVDS outputs (50% on left and right side) | Single-ended buffers with complementary outputs (all four sides) Differential buffers with true LVDS outputs (50% on left and right side) |

| Differential Output<br>Emulation Capability | All four sides                                                         | All four sides                                                         | All four sides                                                                                                                            | All four sides                                                                                                                            |

| PCI Support                                 | No                                                                     | No                                                                     | Top side only                                                                                                                             | Top side only                                                                                                                             |

表 7 MachXO 支持的 I/O 标准

表 8 和表 9 分别为 MachXO 器件支持的输入和输出 I/O 标准。

|                                                                                  | VCCIO (NOM) |      |      |      |      |

|----------------------------------------------------------------------------------|-------------|------|------|------|------|

| Input Standard                                                                   | 3.3V        | 2.5V | 1.8V | 1.5V | 1.2V |

| Single Ended Interfaces                                                          |             |      |      |      |      |

| LVTTL                                                                            | √           | √    | √    | √    | √    |

| LVTTL                                                                            | √           | √    | √    | √    | √    |

| LVCMOS33                                                                         | √           | √    | √    | √    | √    |

| LVCMOS33                                                                         | √           | √    | √    | √    | √    |

| LVCMOS25                                                                         | √           | √    | √    | √    | √    |

| LVCMOS25                                                                         | √           | √    | √    | √    | √    |

| LVCMOS18                                                                         |             |      | √    |      |      |

| LVCMOS15                                                                         |             |      |      | √    |      |

| LVCMOS12                                                                         | √           | √    | √    | √    | √    |

| PCI1                                                                             | √           |      |      |      |      |

| Differential Interfaces                                                          |             |      |      |      |      |

| BLVDS <sup>2</sup> , LVDS <sup>2</sup> , LVPECL <sup>2</sup> , RSDS <sup>2</sup> | √           |      |      |      |      |

Top banks of MachXO1200 and MachXO2280 devices only.

MachXO1200 and MachXO2280 devices only.

表 8 支持的输入标准

| Output Standard                         | Drive                | V <sub>CCIO</sub> (Nom.) |  |  |  |

|-----------------------------------------|----------------------|--------------------------|--|--|--|

| Single-ended Interfaces                 |                      |                          |  |  |  |

| LVTTL                                   | 4mA, 8mA, 12mA, 16mA | 3.3                      |  |  |  |

| LVCMOS33                                | 4mA, 8mA, 12mA, 14mA | 3.3                      |  |  |  |

| LVCMOS25                                | 4mA, 8mA, 12mA, 14mA | 2.5                      |  |  |  |

| LVCMOS18                                | 4mA, 8mA, 12mA, 14mA | 1.8                      |  |  |  |

| LVCMOS15                                | 4mA, 8mA             | 1.5                      |  |  |  |

| LVCMOS12                                | 2mA, 6mA             | 1.2                      |  |  |  |

| LVCMOS33, Open Drain                    | 4mA, 8mA, 12mA, 14mA | _                        |  |  |  |

| LVCMOS25, Open Drain                    | 4mA, 8mA, 12mA, 14mA | _                        |  |  |  |

| LVCMOS18, Open Drain                    | 4mA, 8mA, 12mA, 14mA | _                        |  |  |  |

| LVCMOS15, Open Drain                    | 4mA, 8mA             | _                        |  |  |  |

| LVCMOS12, Open Drain                    | 2mA, 6mA             | _                        |  |  |  |

| PCl33 <sup>3</sup>                      | N/A                  | 3.3                      |  |  |  |

| Differential Interfaces                 |                      |                          |  |  |  |

| LVDS <sup>1,2</sup>                     | N/A                  | 2.5                      |  |  |  |

| BLVDS <sup>2</sup>                      | N/A                  | 2.5                      |  |  |  |

| RSDS <sup>2</sup> , LVPECL <sup>2</sup> | N/A                  | 3.3                      |  |  |  |

- 1. MachXO1200 and MachXO2280 devices have dedicated LVDS buffers.

- 2. These interfaces can be emulated with external resistors in all devices.

- 3. Top banks of MachXO1200 and MachXO2280 devices only.

表 9 支持的输出标准

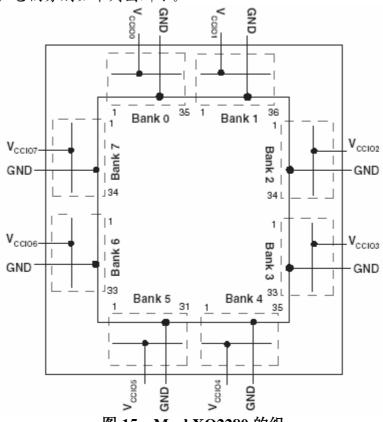

# sysIO 缓冲区

这个系列的器件有不同数目的组。较大的两个器件 MachX01200 和 MachX02280 的周围有 8 个组。MachX0640 的周围有 4 个组,MachX0256 的周围只有 2 个组。它们分别如下列图所示。

图 15 MachXO2280 的组

图 17 MachXO640 的组

图 18 MachXO256 的组

# 睡眠模式

MachXO 的 "C"型器件(Vcc=1.8/2.5/3.3V)具有睡眠模式,在器件不工作时,使待机电流减少两个数量级。睡眠模式由 SLEEPN 引脚进行控制。

睡眠模式期间,逻辑部分不工作,寄存器和 EBR 内容不保留, I/0 处于三态。对器件编程或配置时,不要使用睡眠模式。在睡眠模式,电源处于正常工作范围,表 10 对正常、关闭和睡眠模式特性进行了比较。

| Characteristic                  | Normal        | Off             | Sleep           |

|---------------------------------|---------------|-----------------|-----------------|

| SLEEPN Pin                      | High          | _               | Low             |

| Static Icc                      | Typical <10mA | 0               | Typical <100uA  |

| I/O Leakage                     | <10µA         | <1mA            | <10µA           |

| Power Supplies VCC/VCCIO/VCCAUX | Normal Range  | 0               | Normal Range    |

| Logic Operation                 | User Defined  | Non Operational | Non operational |

| I/O Operation                   | User Defined  | Tri-state       | Tri-state       |

| JTAG and Programming circuitry  | Operational   | Non-operational | Non-operational |

| EBR Contents and Registers      | Maintained    | Non-maintained  | Non-maintained  |

表 10 正常, 关闭和睡眠模式特性

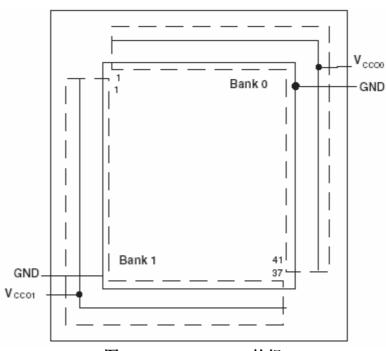

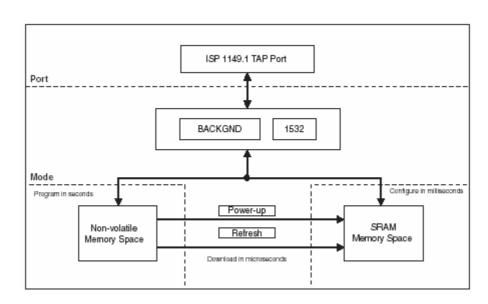

#### 器件的配置

所有的 MachXO 器件都含有一个端口用来实现器件的配置和编程。测试接入端口(TAP)支持位宽的配置方式。

MachXO 中的非易失存储器可以用两种不同的模式来配置:

• 在1532模式下通过1149.1端口来配置。在此模式下,器件脱机, I/0 连至BSCAN 寄存器。

• 在后台模式下通过1149.1 端口来配置。在此方式下重新编程时,器件可以同时进行工作。

MachXO 中的 SRAM 配置存储器可以用三种不同的模式来配置:

- 在上电时通过片上的非易失存储器来配置。

- 经由 IEEE 1149.1 端口发送一条刷新命令命令来实现这种配置。

- 在 IEEE 1532 模式下通过 IEEE 1149.1 端口来配置。

图 19 展示了 MachXO 器件中不同的编程模式。上电时,采用 IEEE 1532 协议,经 IEEE 1149.1 串行 TAP 端口对 SRAM 进行配置。

图 19 MachXO 器件配置和编程示意图

#### I/O 控制

用 IEEE 1532 模式对非易失存储器编程、SRAM 配置或者发送刷新命令时,用户可以指定 I/0 为高电平、低电平、三态或保持当前状态。这为实现需要重新配置和重复编程的系统提供了很好的灵活性。

#### TransFR

TransFr 是 Lattice 特有的技术,用户可以在现场更新逻辑而不中断系统的运行。

#### 安全性

MachXO 系列器件有闪存 RAM 和配置 SRAM。可以从 TAP 端口读回这两种存储器的内容。SRAM 和闪存的位流均可以被保护而免受未经许可的读回。MachXO 器件中闪存 RAM 和配置 SRAM 有多个安全熔丝,用于阻止未经许可的读回。一旦保密位设置后,消除保密位的的唯一办法是擦除存储器内容。从加密后的器件读回的内容全部为 0。