# Cadence 应用注意事项

| 1, | PCB工艺规则                   | 4   |

|----|---------------------------|-----|

| 2、 | Cadence的软件模块              | 4   |

| 3、 | Cadence的软件模块 Pad Designer | 5   |

| 4、 | ALLEGRO的PCB元件             | .10 |

| 5、 | Allegro PCB工作前的配置         | .20 |

| 6、 | 制作"菲林"                    | .24 |

| 7、 | 用CAM350 检查加工文件            | .35 |

| 8、 | 引用设计模块                    | .43 |

| 9、 | 多层PCB排版流程                 | .53 |

|    |                           |     |

Copyright (c) by Wang Wolver, INNOV Inc. R&D Center wolver@21com.com

All rights reserved.

Redistribution and use in documentation, with or without modification, are permitted provided that the following conditions are met:

- 1. Redistributions of documentation must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions documentation must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

- 3. All advertising materials mentioning features or use of this documentation must display the following acknowledgement:

- This product includes it developed by Wang Wolver

- 4. The name of the author may not be used to endorse or promote products derived from this documentation without specific prior written permission.

THIS DOCUMENTATION IS PROVIDED BY THE AUTHOR "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE AUTHOR BE LIABLE FOR ANY INDIRECT, INCIDENTAL, SPECIAL, DIRECT. EXEMPLARY, CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING **NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS** DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

版权: 王卫无,北京讯业互联科技有限公司一研究开发中心wolver@21com.com 保留一切权利

如果符合以下条件,则无论是以原文形式,且不论是否修改,再分发和使用本文档都是被允许的。

- 1、 文档的再分发必须保留上述的版权声明、本条件说明和以下免责声明。

- 2、 非本文档形式的再分发,必须在证明文件和(或)其它一同提供的材料中重新作上述的版权声明、本条件说明和以下免责声明。

- 3、一切提及本文档和使用的广告材料必须显示以下致谢: 本产品包含:王卫无、(北京讯业互联科技有限公司--研究开发中心)的文档。

- 4、 如果没有预先得到特定的书面许可,不能用作者的名字来宣传推广基于本文件得到 的产品。

# 免责声明:

本文档是由"某某"作者提供,如果出现以下情况,作者都不承担任何责任:

- 1、 因作者的说明以及任何明确的或暗示的保证(包括但不限于表达某种商业性和适合某一特定目的暗示性保证)而产生的损失。

- 2、无论在何种情况下,对使用本文档造成的任何直接的、间接的、偶然的、特定的、可 预见性的和连带产生的损失(包括但不限于获取替代产品和服务、作用丧失、数据遗失、 利益损失或商业干预),无论这些损失是怎样造成的,并且是以何种方式阐释责任。

- 3、任何因使用本文档而相关的合同、严格赔偿责任和侵权行为(包含: 疏忽或其它)的损失,甚至即便是可能的此类已经明示或暗示的损失。

# 1、PCB工艺规则

以下规则可能随中国国内加工工艺提高而变化

- 1.1. 不同元件间的焊盘间隙:大于等于 40mil(1mm),以保证各种批量在线焊板的需要。

- 1.2. 焊盘尺寸: 粘锡部分的宽度保证大于等于 10mil(0.254mm),如果焊脚(pin)较高,应修剪;如果不能修剪的,相应焊盘应增大.....

- 1.3. 机械过孔最小孔径:大于等于 6mil(0.15mm)。小于此尺寸将使用激光打孔,为国内大多数 PCB 厂家所不能接受。

- 1.4. 最小线宽和线间距:大于等于 4mil(0.10mm)。小于此尺寸,为国内大多数 PCB 厂家 所不能接受,并且不能保证成品率!

- 1.5. PCB 板厚:通常指成品板厚度,常见的是: 0.8mm、1mm、1.2mm、1.6mm、2.0mm; 材质为 FR-4。当然也有其它类型的,比如:陶瓷基板的...

- 1.6. 丝印字符尺寸: 高度大于 30mil(0.75mm), 线条宽大于 6mil(0.15mm), 高与宽比例 3:2

- 1.7. 最小孔径与板厚关系:目前国内加工能力为:板厚是最小孔径的 8~15 倍,大多数多层板 PCB 厂家是:8~10 倍。举例:假如板内最小孔径(如:VIA)6mil,那么你不能要求厂家给你做 1.6mm 厚的 PCB 板,但可以要求 1.2mm 或以下的。

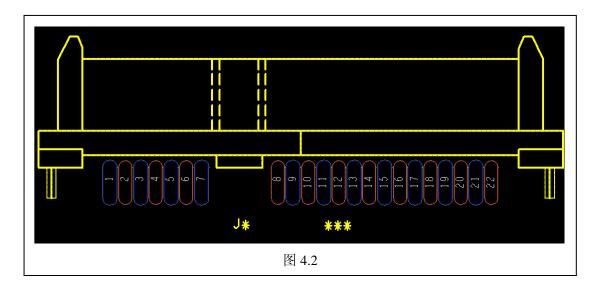

- 1.8. 定位基准点:用于给贴片机、插件机等自动设备取基准点,用 30mil(0.75mm)直径的 表贴实心圆盘(需要被 SOLDERMASK,以便铜裸露或镀锡而反光)。分布于顶层(TOP) 的板边对脚线、底层(BOTTOM)的板边对脚线,每面最少 2 个;另外无引脚封装的 贴片元件也需要在 pin1 附近放一个(不能被元件遮盖,可以在做这些元件封装时做好),这些元件可能是:BGA、LOFN等....比如:后面的图 4.3

- 1.9. 成品板铜薄厚度:大于等于 35um,强制 PCB 板厂执行,以保证质量!

- 1.10. 目前国内大多数 2 层板厂加工能力:最小线宽和线间距 8mil(0.2mm)、机械过孔最小孔径 16mil(0.4mm)。多层板厂商只受 1.1~1.9 限制。

- 1.11. 加工文件: GERBER、DRILL、ROUTE 或 STREAM。

- 1.11.1. **GERBER**: 光绘文件,保持与 CAM350V9.0 兼容就能为 PCB 厂接受。

- 1.11.2. DRILL: 钻孔(圆孔)文件, 保持与 CAM350V9.0 兼容就能为 PCB 厂接受。

- 1.11.3. ROUTE: 铣孔(非圆孔)文件,保持与 CAM350V9.0 兼容能为 PCB 厂接受。

- 1.11.4. STREAM: 流文件,目前国内只有一两家 PCB 厂识别,包含了 1.11.1~3 的所有信息。

# 2、Cadence 的软件模块

- 2.1、Design Entry CIS: 原理图制作和分析模块之一,ORCAD 是该模块的核心,为大多数电路设计员喜爱。

- 2.2、Design Entry HDL: 原理图制作和分析模块之一, Cadence 原创, 没有 ORCAD 那么受欢迎。

- 2.3、Pad Designer: 主要用于制作焊盘,供 Allegro 使用。

- 2.4、Allegro: 包含 PCB 编辑(Edit)、自动布线(Specctra)、信号完整性分析(SI)

- 2.5、Sigxplorer: PCB 布线规则和建模分析工具,与 Allegro 配合使用。

- 2.6、Layout Pluse: ORCAD 公司的 PCB 排板软件(ORCAD 已被 Cadence 收购), 很少人用。

- 2.7、文件和目录命名注意事项:严禁中文、严禁空格、字母最好全小写。

# 3、Cadence 的软件模块--- Pad Designer

- 3.1、PAD 外形: Circle 圆型、Square 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape 形状(可以是任意形状)

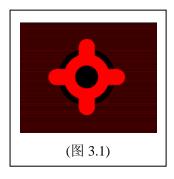

- 3.2、Thermal relief: 热涨缩间隙,常用于相同 NetList 的填充铜薄与 PAD 的间隙。通常比 Pad 直径大,详细说明见 3.12 和 3.13。形状见: 图 3.1 和 3.5(阴片)

- 3.3、Anti Pad: 抗电边距,常用于不同 NetList 的填充铜薄与 PAD 的间隙。通常比 Pad 直径大,详细说明见 3.12 和 3.13。形状见:图 3.2 和 3.5(阴片)

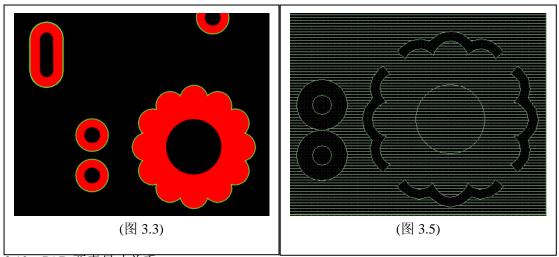

- 3.4、SolderMask: 阻焊,使铜箔裸露而可以镀涂。通常比 Pad 直径大 4mil。形状见: 图 3.3(绿色部分)

- 3.5、PasteMask: 胶贴或刚网: 通常与 SolderMask 一样。

- 3.6、FilmMask (用途不明): 暂时与 SolderMask 一样。

- 3.7、Blind: 瞒孔。从外层到里层,或者只有底层(可做金手指盘)。

- 3.8、Buried: 瞒埋孔: 只在内层,除非特别原因,不建议使用!

- 3.9、Plated: 孔化, 即孔壁镀涂! 例如: 锡。会减小孔径 1~2mil

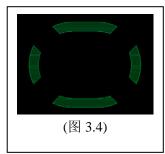

- 3.10、Flash: Pad 面的一种,只在阴片层(除非不想使用自动布线)里显示。对于异形盘(如图 3.4 和 3.5),可以先用 AutoCAD 先做外形,再 DXF 导入 Allegro,在 Allegro 中使用 Compose Shape 功能填充,然后删除 cline 边界线,再把 Shape 移到正确的位置,更改文件类型为 flash,存盘即可。

- 3.11、Shape: Pad 面的一种,可以做奇形怪状(如图 3)的盘面.....复杂的形状可用 AutoCAD 制作,类似 3.10,不过文件属性改为 Shape 再保存!

- 3.12、PAD 要素尺寸关系:

- 3.12.1) Hole <= PAD < Thermal relief = Anti Pad

- 3.12.2) SolderMask = PasteMask = FilmMask = PAD + 4mil

- 3.13、flash 要素尺寸规则(单位: mil):

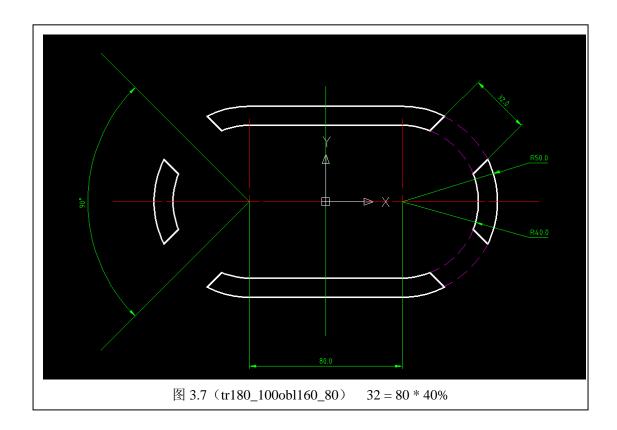

- 3.13.1) < 内盘 <= 20 的, 外盘增大 10 比如: tr28cir18

- 3.13.2) 20 < 内盘 <= 80 的, 外盘增大 20 比如: tr60cir40 tr120 92obl100 72

72 是基本盘面, 因此属于 20~80 范围)

- 3.13.3) 80 < 内盘 <= 160 的,外盘增大 30

- 3.13.4) 160 < 内盘 <= 320 的,外盘增大 40 比如: tr240cir200

- 3.13.5) 320 < 内盘 < ??? 的,外盘增大 80 比如: tr480cir400

- 比如: tr90cir60

- 3.13.6) flash 的 spoke(辐带)宽为盘直径的 40%, spoke 不允许在正交对角线上(比如:图 3.6 是不正确的),必须在45度斜交对角线。否则会导致Thermal relief外形尺寸计算错误!图 3.4 和 3.5 是正确的, 3.7 是机械尺寸关系图。Flash 规则同样适于 Thermal relief 和 Anti Pad

图 3.6 (错误的 spoke)

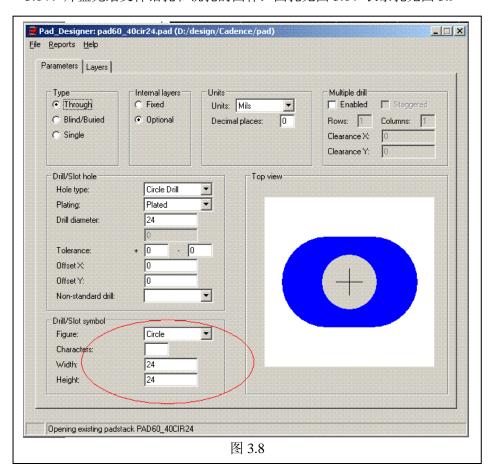

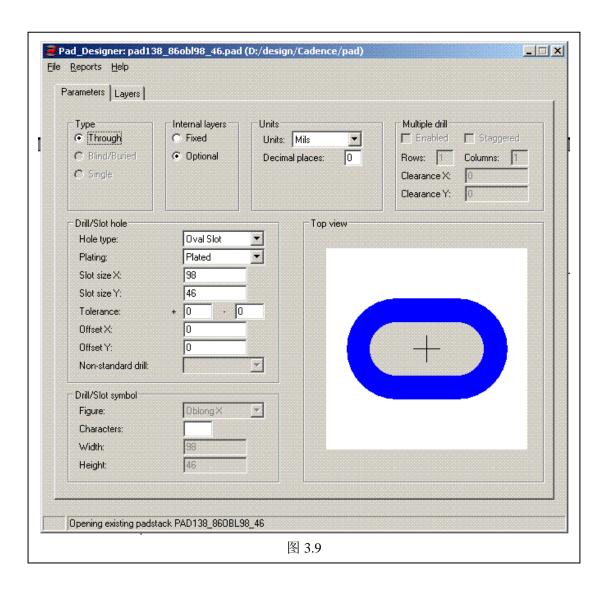

3.14、焊盘光绘文件钻孔和铣孔的图释:圆孔见图 3.8、长条孔见图 3.9

Pad\_Designer: pad120cir72d196.pad (D:/design/Cadence/pad) \_ | X | File Reports Help Parameters Layers Padstack layers Regular Pad Thermal Relief Anti Pad Oblong 316×120 Oblong 346×1 Oblong 346 Bgn BEGIN LAYER

→ DEFAULT INTER Oblong 316 X 120 Flash End END LAYER Oblong 316 × 120 Oblong 346 × 1 Oblong 346 SOLDERMASK\_TOP Oblong 320 X 124 N/A SOLDERMASK\_BOTTOM Oblong 320 X 124 N/A N/A PASTEMASK\_TOP PASTEMASK\_BOTTOM Oblong 320 X 124 N/A N/A Oblong 320 X 124 N/A N/A Thermal Relief Regular Pad Geometry: • • Oblong • Shape: TR346\_1500BL316 ... 316 346 346 Width: Height: 120 150 150 To Offset X: 0 To 0 0 0 DEFAULT INTERNAL Current layer: 图 3.12 (单盘双孔 pad120cir72d196.pad、盘面)

# 4、ALLEGRO 的 PCB 元件

Allegro 的 PCB 元件是一个元件一个独立文件,元件后缀名: dra

# 4.1、PCB 元件(Symbol)的必要的 CLASS/SUBCLASS

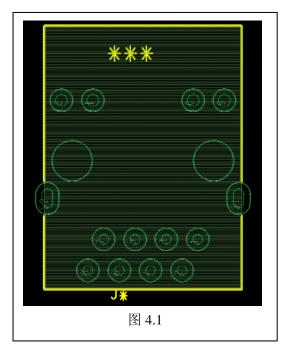

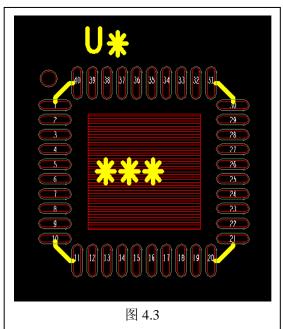

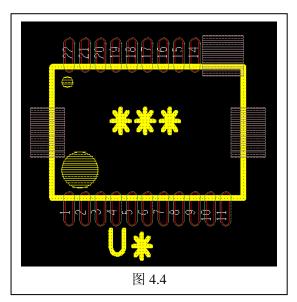

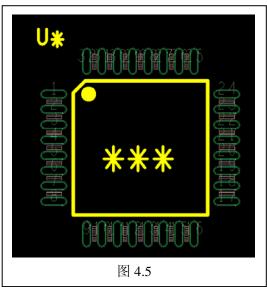

| 序号 | CLASS       | SUBCLASS        | 元件要素                 | 备注   |

|----|-------------|-----------------|----------------------|------|

| 1  | Eth         | Тор             | PAD/PIN(通孔或表贴孔)      | 必要、有 |

|    |             |                 | Shape (贴片 IC 下的散热铜箔) | 电导性  |

|    |             |                 | 见图: 4.1~7            |      |

| 2  | Eth         | Bottom          | PAD/PIN(通孔或盲孔)       | 视需要  |

|    |             |                 | 见图: 4.2              | 而定、有 |

|    |             |                 |                      | 电导性  |

| 3  | Package     | Pin_Number      | 映射原理图元件的 pin 号。      | 必要   |

|    | Geometry    |                 | 见图: 4.1~7            |      |

|    |             |                 | 如果 PAD 没标号,表示原理图不关   |      |

|    |             |                 | 心这个 pin 或是机械孔。       |      |

|    |             |                 | 见图: 4.1 和 4.3        |      |

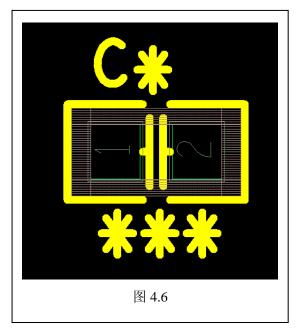

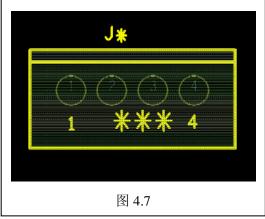

| 4  | Ref Des     | Silkscreen_Top  | 元件的位号。见图: 4.1~7      | 必要   |

| 5  | Component   | Silkscreen_Top  | 元件型号或元件值。见图: 4.1~7   | 必要   |

|    | Value       |                 |                      |      |

| 6  | Package     | Silkscreen_Top  | 元件外形和说明:线条、弧、字、      | 必要   |

|    | Geometry    |                 | Shape 等。见图: 4.1~7    |      |

| 7  | Package     | Place_Bound_Top | 元件占地区和高度。见图: 4.1~7   | 必要   |

|    | Geometry    |                 | 图 4.2~6 也有,只是图中没显示   |      |

| 8  | Route       | Тор             | 禁止布线区                | 视需要  |

|    | Keepout     |                 | 图 4.4~5              | 而定   |

| 9  | Via Keepout | Тор             | 禁止放过孔                | 视需要  |

|    |             |                 | 图 4.6                | 而定   |

# 4.2、PCB 元件(Symbol)位号的常用定义

通常使用 ORCAD 的默认定义,以便 SCH 与 PCB 统一。否则,会影响 Annotate 和 BackAnnotate 图 4.1~7 是这些定义的样本。

电阻: R\*

电阻 (可调): RP\* 电阻 (阵列): RCA\*

电容: C\* 电感: L\* 继电器: LE\* 二极管: D\* 三极管: Q\* 集成块: U\* 接插件: J\*

# 4.3、PCB 元件(Symbol)字符的字号和尺寸

不同的要素选择不同字号为原则,举例如下:

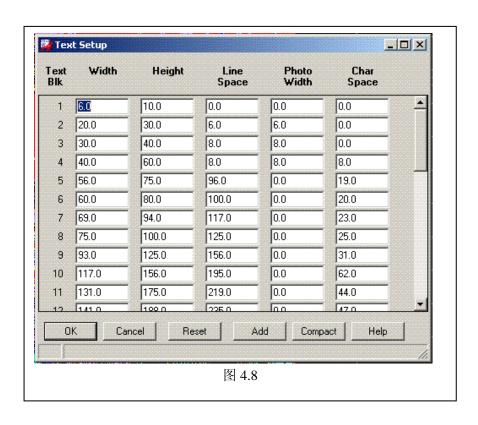

| 序号 | CLASS     | SUBCLASS       | 字号和尺寸 | 备注             |

|----|-----------|----------------|-------|----------------|

| 1  | Package   | Pin_Number     | 1#    | 用于元件引脚号        |

|    | Geometry  |                |       |                |

| 2  | Ref Des   | Silkscreen_Top | 2#    | 用于元件位号         |

| 3  | Component | Silkscreen_Top | 2#    | 用于元件型号或元件值     |

|    | Value     |                |       |                |

| 4  | Package   | Silkscreen_Top | 3#    | 用于元件附加描述。图 4.7 |

|    | Geometry  |                |       |                |

# 4.3、Allegro Board (wizard)定制 PCB 元件(Symbol)

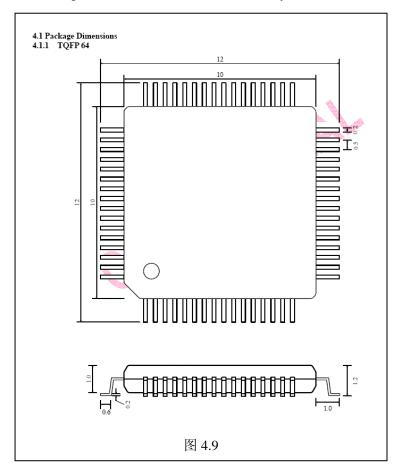

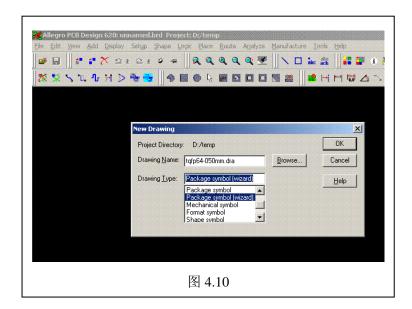

- 图 4.9 是 TQFP64、0.5mm 间距的 DataSheet,下面举 例制作这个 Symbol

- 1) 文件名、存放位置、工 作模式。图 4.10

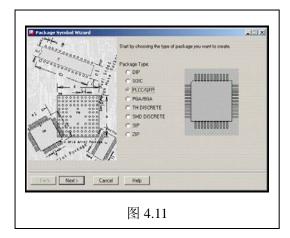

- 2) 选择封装外形: 选 4 面 脚的 QFP。见图 4.11

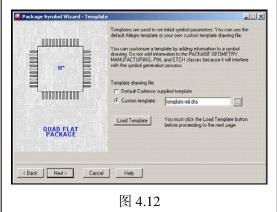

- 3)选择工作模板:可用默认的或用户自定义的。我们选自定义的是因为:模板预先已经设置了绘图尺寸、使用 Class/SubClass、颜色、字体、单位和分辨率等要素。更重要的是:默认的模板有 BUG,会自动清除 PAD 里的 Flash!!!见图 4.12

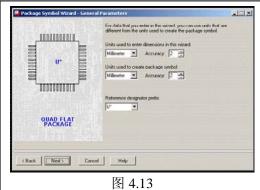

- 4)设置单位、分辨率、位号:由于我们使用自定义模板,因此这些设置从上一步继承下来。如果你的设置与图 4.13 不一样,请照单修改。

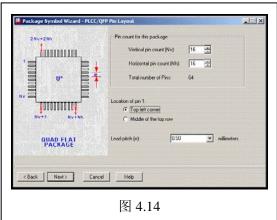

- 5)设置 pin 数与间距:如果你的设置与图 4.14 不一样,请照单修改。注意 pin1的位置选择!

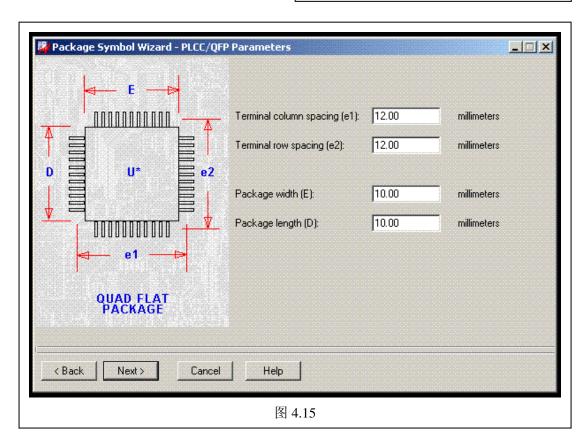

- 6)设置外形物理尺寸和 pin 脚边界:根据图 4.9

E = D = 10mm

e1 = e2 = 12mm 见图 4.15

值得注意的是 e1/e2 的值: 这样做使引脚的边缘处于 贴盘的中心,使贴盘外露 一半,便于手工焊接!

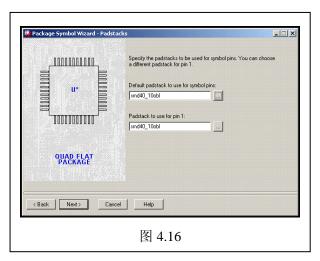

7) 选择 pin 的焊盘: 见图 4.16, 选择表贴盘 40mil 长、10mil 宽的长条椭圆盘。当然,可以给 pin1 定义不同于其它 pin 的盘。

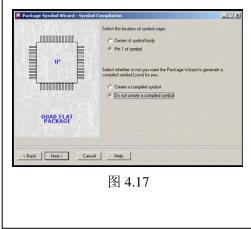

- 8) 选择元件基准点:选 pin1,并且不创建 psm 文件(因为后面还有修改)。见图 4.17

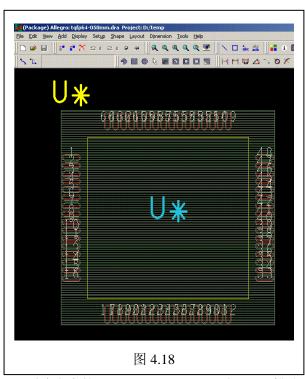

- 9) 结束 Board (wizard): next->finish 后,见图 4.18。你看到颜色如果与图不同,是因为在步骤(3)里用的模板不同.....

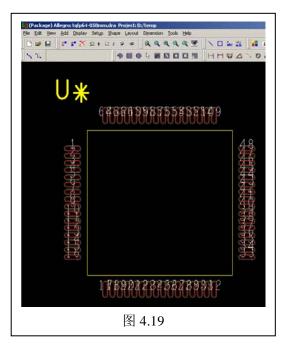

10)删除多余的CLASS/SUBCLASS: 参见4.1 描述, 关闭Package Geometry/Place\_Bound\_Top, 删除PACKAGE GEOMETRY/DFA\_BOUND\_TOP 上的 Shape;关闭Package Geometry/Silkscreen\_Top,删除PACKAGE GEOMETRY/ASSEMBLY\_TOP上的外形Line;删除REF DES/ASSEMBLY\_TOP的字符U\*;打开Package Geometry/Silkscreen\_Top;效果见图 4.19

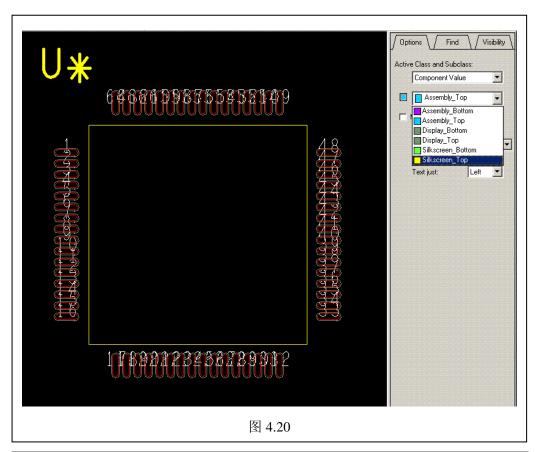

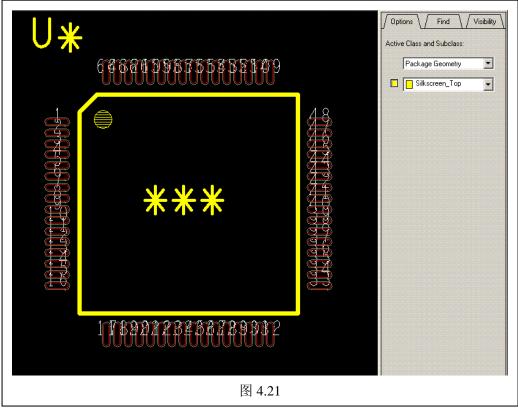

- 11) 设置元件 Value: 点击 Menu\Layout\Labels\Value, 选择 Component Value/ Silkscreen\_Top, 然后点取绘图区,输入\*\*\*, done。见图 4.20, 4.21

- 12) 标示 pin1 位置:将 Package Geometry/Silkscreen\_Top 上的 Line 倒 45 度角,并将 Line 宽改为 0.2mm,加 Shape 圆点。见图 4.21

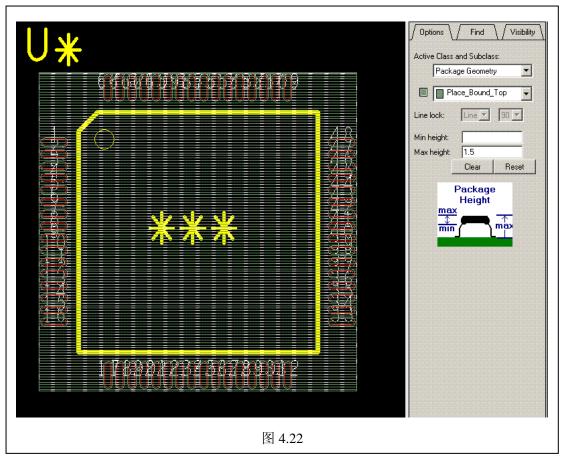

13)设置占位属性: 打开 Package Geometry/Place\_Bound\_Top, 点取 Menu\Setup\Areas\Package Height, 选中 Shape,输入高度: 1.5(数据手册 1.2mm)。见图 4.22

- 14) 清除冗余的 PAD: 冗余的 PAD 指包含却未在本 Symbol 中使用的 PAD! 通常在手动制图中会产生,而在 wizard 模式下不太会发生。点取 Menu\Tools\Padstack\Modify Design Padstack,选择 Purge\All,清除冗余的 PAD

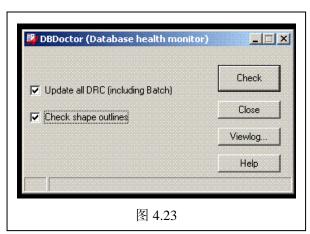

- 15) 清除非法数据:点取 Menu\Tools\Database Check, 然后 Check。见图: 4.23

16) 保存文件并创建 psm 文件: 点取 Menu\View\Zoom Fit, 然后 Menu\File\Save

## 4.4、常见问题 FAQ

1)PAD 已经修改了(PAD 文件名没变),但有 Symbol 用了这个 PAD,怎样更新这个 Symbol? A: Allegro 打开这个 Symbol,点取 Menu\Tools\Padstack\Reflash,然后重复 4.3 介绍的(14) 至(16)步骤

2)已经存在的 Symbol 想使用不同名字的 PAD, 怎样更新这个 Symbol? A: Allegro 打开这个 Symbol,点取 Menu\Tools\Padstack\Replace,选择替换的 PAD,然后重复 4.3 介绍的(14)至(16)步骤

# 3) 通孔 PAD 命名规则?

A: 3.1)圆孔 padMMcirNN.pad,MM 代表外盘,NN 代表孔径,单位 mil,如: pad72cir32.pad 3.2)长条孔 padMM\_NNoblXX\_YY.pad,MM\_NN 代表外盘,XX\_YY 孔形,单位 mil,一般大数在前,小数在后。如: pad100\_72obl60\_32.pad,见图 3.3 和 3.5 需要注意:最好别做矩形孔!因为长条孔实际是用钻头铣出来的,所以矩形的直角边基本没法处理,并且铣孔文件(1.11.3 描述)生成也比较困难!

## 4) 表贴 PAD 命名规则?

A: 类似通孔,只是没有打孔表示部分。比如: smdMMcir.pad、smdMM NNobl.pad

# 5) 过孔命名规则?

A: 首先过孔我们规定只能用圆的通孔,除非特殊要求,不用异形孔、瞒孔、瞒埋孔!因此,类似圆通孔: viaMMcirNN.pad

## 6) Flash 命名规则?

A: 类似通孔, 只不过外尺寸表示 Thermal relief, 内尺寸表示盘面。比如: tr120\_92obl100\_72.dra 是通孔 pad100\_72obl60\_32.pad 的 flash 盘。见图: 3.4

## 7) Shape 命名规则?

A: 类似表贴孔,通常以 shp 为开始,由于用的比较少,所以命名自己看得懂就好。比如:图 3.3 和 3.5 的"梅花 clubs" shape,我们命名为: shp304clu.dra(用于 eth 类)、shp308clu.dra(用于 SolderMask)、shp344clu.dra(用于 Anti Pad)、tr344clu304.dra(Thermal relief)。

## 8) 单盘多孔命名规则?

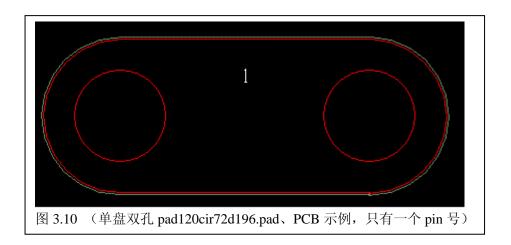

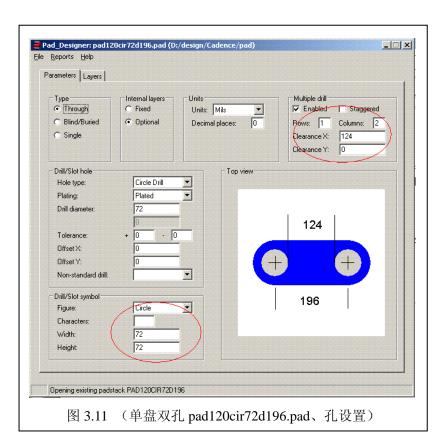

A: 类似通孔, 举例如下: pad120cir72d196.pad, 表示盘直径 120、孔 72、孔距 196、(d) 双孔。见图: 3.10 (PCB 示例)、3.11 (打孔参数设置)、3.12 (盘面示例)

# 强制标准

制作 Package Symbol 时,必须使用分发库模板文件 template-mil.dra 和 template-mm.dra,以回避 Allegro 使用默认模板导致 PAD 中 Flash 丢失的问题,详见 4.3 部分的 BUG 描述…… Package Symbol模板文件通常在分发库目录的template下….

# 5、Allegro PCB工作前的配置

## 5.1) User Preferences

Setup\User Preferences\AutoSave

(建议设置每10分钟保存一次)

$Setup \backslash User\ Preferences \backslash Design\_paths \backslash padpath$

(焊盘、过孔的搜索路径)

Setup\User Preferences\Design\_paths\psmpath

(flash、shape、symbol 的搜索路径)

Setup\User Preferences\Ui\pcb\_cursor

(PCB 显示光标:选 infinite,使用全屏交叉光标;选 cross,使用交叉小光标;)

Setup\User Preferences\Wirebond\wirebond\_push\_and\_shove

$Setup \backslash User\ Preferences \backslash Show\_element \backslash ShowElement\_high speed$

(使用 PCB SI 格式的对话框)

# 5.2) Setup\Drawing Size

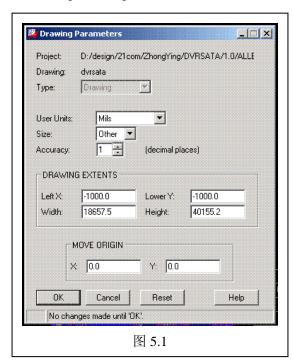

图 5.1 是参考设置建议,规定:一律使用 Mils 单位,精度 1。

LeftX/LowerY 为-1000, 使作图基点定位在 (1000, 1000), 好处是.....?

# 5.3) Setup\Drawing options

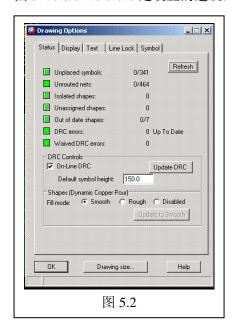

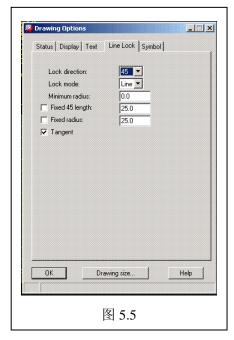

图 5.2/5.3/5.4/5.5/5.6 是设置的建议,其中图 5.2 可以用来查看布板完成情况和错误统计....

# 5.4) Setup\Text sizes

参看图 4.8 是设置的建议....

# 5.5) Setup\Grids

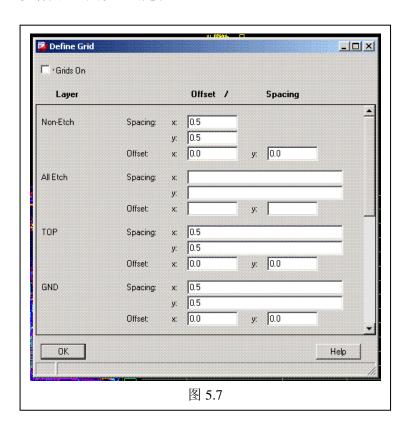

参看图 5.7 是设置的建议....

# 5.6) Setup\Subclasses

除非有特殊需求,一般不作设置....

# 5.7) Setup\Cross-section

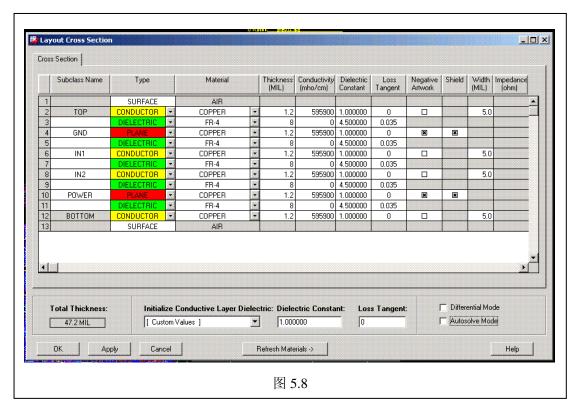

这图 5.8 是典型的 6 层板设置(其中 GND、POWER 为阴片)参考...

# 5.8) Setup\Materials

一般不需要设置,除非做板厚和 PCB 仿真....

## 5.9) Setup\Vias

一般不需要设置,除非有瞒孔和瞒埋孔....

## 5.10) Setup\Constraints

设置布线规则,取决于对电路性能和PCB工艺的理解深度....

# 5.11) Setup\Outlines\Board outlines

通过该方法绘规则的板边框和 route keepin,非规则的,可以通过 dxf 文件导入实现。

# 5.12) Shape\Global Dynamic param

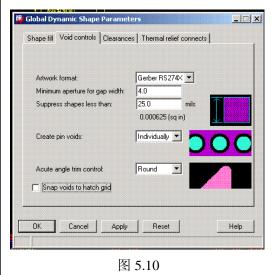

设置动态避让铺铜参数....图 5.9~5.12 是建议设置....

# 6、制作"菲林"

"菲林"就是光绘底片,在 Cadence 里叫 Artwork,可以通过 Allegro\manufacture\Artwork 菜单调用制作功能....以图 5.8 的 6 层板为例,说明要素如下:

| 图层序            | Class/SubCLass                   | 功能描述                 | 颜色 | 备注                     |

|----------------|----------------------------------|----------------------|----|------------------------|

|                | PIN/SOLDERMASK_TOP               | 所有的 PIN<br>镀锡        |    | 可以增加过孔类,               |

| TOP_SOLDERMASK | PACKAGE GEOMETRY/ SOLDERMASK_TOP | 附加连线、<br>铺铜等镀锡       |    | 但我们规定不要包 含过孔盘面镀锡!      |

|                | BOARD GEOMETRY/OUTLINE           | 板外框                  |    | I Clamma (X)           |

|                | REF DES/SILKSCREEN_TOP           | 上层元件位<br>号           |    |                        |

|                | PACKAGE GEOMETRY/ SILKSCREEN_TOP | 上层元件外 形              |    |                        |

| TOP_SILK       | BOARD GEOMETRY/ SILKSCREEN_TOP   | 上层附加:<br>标注、技术<br>要求 |    |                        |

|                | BOARD GEOMETRY/OUTLINE           | 板外框                  |    |                        |

|                | PIN/TOP                          | 元件脚                  |    |                        |

|                | ЕТН/ТОР                          | 连接线、铺铜               |    | 特别增加 DRC 是因为:如果有错误,    |

| ТОР            | VIA CLASS/TOP                    | 过孔                   |    | 可以即时发现;如果没错误,该类不       |

|                | DRC ERROR CLASS/TOP              | DRC 错误标<br>识         |    | 影响 Artwork 的输<br>出     |

|                | BOARD GEOMETRY/OUTLINE           | 板外框                  |    |                        |

|                | PIN/GND                          | 元件脚                  |    |                        |

|                | ETH/GND                          | 连接线、铺铜               |    | 中间层不需要                 |

| GND            | VIA CLASS/GND                    | 过孔                   |    | SOLDERMASK,<br>其余同 TOP |

|                | DRC ERROR CLASS/GND              | DRC 错误标<br>识         |    | <b>光外門 10</b> 1        |

|                | BOARD GEOMETRY/OUTLINE           | 板外框                  |    |                        |

续上表:

| タム <b>な:</b><br>图层序 | Class/SubCLass          | 功能描述         | 颜色 | 备注                               |

|---------------------|-------------------------|--------------|----|----------------------------------|

|                     | PIN/IN1                 | 元件脚          |    |                                  |

|                     | ETH/IN1                 | 连接线、铺铜       |    | <b>小词只</b> 了带来                   |

| IN1                 | VIA CLASS/IN1           | 过孔           |    | 中间层不需要<br>SOLDERMASK,<br>其余同 TOP |

|                     | DRC ERROR CLASS/IN1     | DRC 错误标<br>识 |    |                                  |

|                     | BOARD GEOMETRY/OUTLINE  | 板外框          |    |                                  |

|                     | PIN/IN2                 | 元件脚          |    |                                  |

|                     | ETH/IN2                 | 连接线、铺铜       |    | 中间层不需要                           |

| IN2                 | VIA CLASS/IN2           | 过孔           |    | SOLDERMASK,<br>其余同 TOP           |

|                     | DRC ERROR CLASS/IN2     | DRC 错误标<br>识 |    | 共水円 IUT                          |

|                     | BOARD GEOMETRY/OUTLINE  | 板外框          |    |                                  |

|                     | PIN/POWER               | 元件脚          |    |                                  |

|                     | ETH/ POWER              | 连接线、铺铜       |    | <b>山切早</b> 不電冊                   |

| POWER               | VIA CLASS/ POWER        | 过孔           |    | 中间层不需要<br>SOLDERMASK,<br>其余同 TOP |

|                     | DRC ERROR CLASS/ POWER  | DRC 错误标<br>识 |    | 央求回 IOF                          |

|                     | BOARD GEOMETRY/OUTLINE  | 板外框          |    |                                  |

|                     | PIN/ BOTTOM             | 元件脚          |    |                                  |

|                     | ETH/ BOTTOM             | 连接线、铺铜       |    |                                  |

| воттом              | VIA CLASS/ BOTTOM       | 过孔           |    | 同 TOP                            |

|                     | DRC ERROR CLASS/ BOTTOM | DRC 错误标<br>识 |    |                                  |

| l                   | BOARD GEOMETRY/OUTLINE  | 板外框          |    |                                  |

续上表:

| 图层序               | Class/SubCLass                       | 功能描述              | 颜色 | 备注                                                              |

|-------------------|--------------------------------------|-------------------|----|-----------------------------------------------------------------|

|                   | REF DES/SILKSCREEN_ BOTTOM           | 底层元件位<br>号        |    |                                                                 |

| DOMINON ON N      | PACKAGE GEOMETRY/ SILKSCREEN_ BOTTOM | 底层元件外 形           |    |                                                                 |

| BOTTOM_SILK       | BOARD GEOMETRY/ SILKSCREEN_ BOTTOM   | 底层附加:标注           |    |                                                                 |

|                   | BOARD GEOMETRY/OUTLINE               | 板外框               |    |                                                                 |

|                   | PIN/SOLDERMASK_BOTTOM                | 所有的 PIN<br>镀锡     |    | 크 이 ###마카 김 米                                                   |

| BOTTOM_SOLDERMASK | PACKAGE GEOMETRY/ SOLDERMASK_ BOTTOM | 附加连线、铺<br>铜等镀锡    |    | 可以增加过孔类,<br>但我们规定不要包<br>含过孔盘面镀锡!                                |

|                   | BOARD GEOMETRY/OUTLINE               | 板外框               |    | I CTUILING (CO)                                                 |

| NC_DRILL          | MANUFCTURING/NCLEGEND-?-?            | NC Legend<br>表和图释 |    | NCLEGEND-?-?是<br>生成钻孔表后,由<br>Allegro 自动添加                       |

|                   | BOARD GEOMETRY/OUTLINE               | 板外框               |    | 的,?代表的数字与<br>板的层数有关。                                            |

| DESIGN            | 包含除 GND、POWER 外的所有                   | 可以上部分             |    | 设计布线时使用,<br>提高工作效率,不<br>输出 Artwork 文<br>件,否则,PCB 厂<br>家马上就傻了!!! |

# 6.1、Artwork 设置

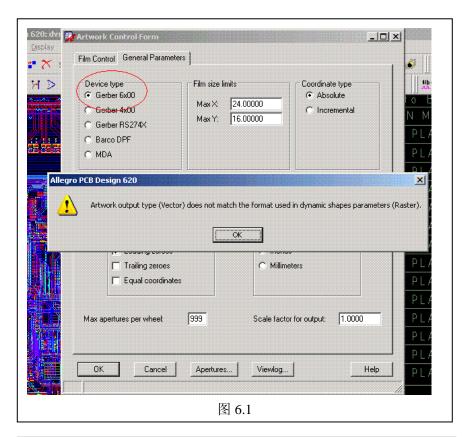

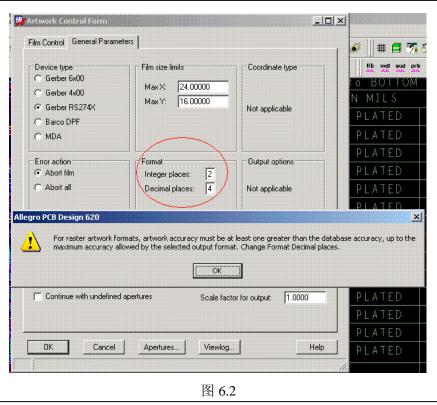

当执行 Allegro\manufacture\Artwork,如果得到如图 6.1 和 6.2 的错误,通常是参数设置不当。比如:图 6.1 就是 Shape 类型与图 5.10 不一致;而图 6.2 是因为输出精度不匹配,Artwork内部数据库精度如下:

| Database Unit | Accuracy | = | Format           |

|---------------|----------|---|------------------|

| MILS          | 0        | = | 2.3              |

| MILS          | 1        | = | 2.4              |

| MILS          | 2        | = | 2.5              |

| MILS          | 3        | = | 2.6 (不支持)        |

| MILS          | 4        | = | 2.7 (不支持)        |

| INCH          | 2        | = | 2.2 (不明含义,不推荐使用) |

| INCH          | 3        | = | 2.2 (不明含义,不推荐使用) |

举例:对于图 5.1 的绘图设置,根据上表应该使用 "Format=2.4",但通过错误信息知道:Artwork 的输出精度必须比制图的高 10 倍,所以选 "Format=2.5"。规定:今后的Artwork 文件一律使用 "英制(Inches)、Accuracy=1、Format=2.5"

图 6.3 和 6.4 是推荐配置。对于图 6.3,不能选择 Equal coordinates,有潜在的 bug,会导致部分输出线条或铺铜丢失。对于图 6.4,每个"Artwork 的 Undefined line width: 6.0"必须定义! 然后按 Create artwork 就输出所有选中的 artwork 到当前工作目录下。需要说明的是:由于我们使用的是 Devicetype=Gerber RS274X,因此不需要配置镜头、光圈等参数。

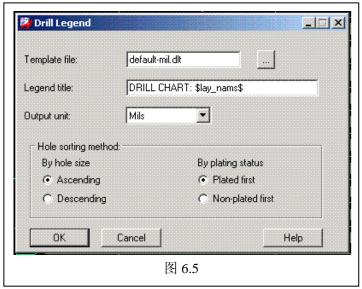

# 6.2、NC Drill Legend 钻孔表

当执行 Allegro\manufacture\NC\Drill Legend 得到图 6.5,除非特别需求,不用更改这些设置。

按 OK 后,放置表,如果不允许放置,通常是绘图区域太小,修改绘图区域见图 5.1

然后在 Artwork 文件的 TOP\_SILK 里增加该要素,见本章上表: Artwork 要素

# 6.3、增加 PCB 工艺技术要求文件

准备文件:用 AutoCAD 做个说明文件,中文字用 shp 字型,然后打爆或分解所有字和线,保存为 DXF 文本格式。

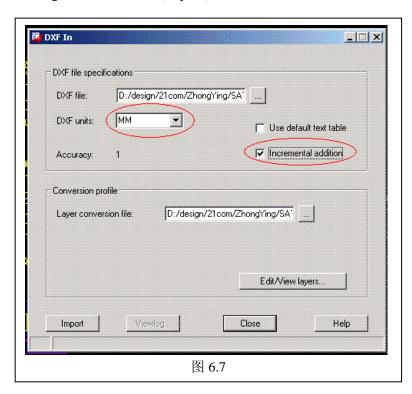

在 Allegro 中,调用 Files\Import\DXF, 得到图 6.7,

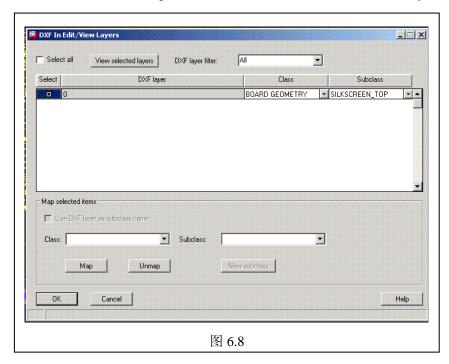

注意单位选择,因为在 AutoCAD 里该文件是用毫米单位,所以这里选: MM 另外必选的是 Increamental addition,否则,DXF 导入后,原来画的 PCB 图就全清空了! 决定 AutoCAD 层与 Allegro 的 Class/SubClass 关系:按 Edit/View layers,见图 6.8 推荐设置

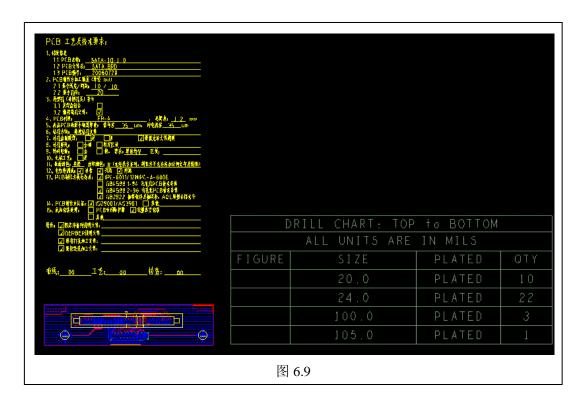

导入后,调整导入说明到合适的位置。完成后,图形大概象图 6.9

# 6.4、NC Drill 钻孔文件生成

Manufacture\NC\NC Drill 得到图 6.10,注意:不选择 Optimize drill head travel,发现生成打孔文件在 CAM350V90 的图视中有部分过孔偏心问题,这也许是 Allegro 的 bug!

| Root file name:                    | sata.drl   |              | Drill         |

|------------------------------------|------------|--------------|---------------|

| Scale factor:<br>Tool sequence:    | Increasing | C Decreasing | NC Parameters |

| Auto tool select                   |            |              |               |

| Separate files for<br>Repeat codes | Cancel     |              |               |

| Optimize drill hea                 | d travel   |              | View Log      |

|                                    |            |              | Help          |

NC Parameters 配置:

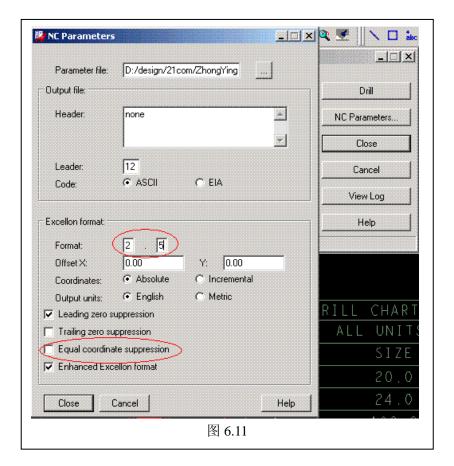

按 NC Parameters, 得到图 6.11,

# 注意:

- 1) 规定: Drill 文件使用英制、Format: 2.5

- 2)不选 Equal coordinate suppression, 发现 CAM350V90 图视丢失打孔的现象, 也许是 Allegro 的 bug

# 6.5、NC Route 铣孔文件

以图 6.12 的 NC Legend 为例,假如已经生成了 NC Drill 文件,那么会有文件 nc\_param.txt 和 nc\_tools\_auto.txt,打开 nc\_tools\_auto.txt 如下:

| 6.0   | P | T01 | 0.000000 | 0.000000 |

|-------|---|-----|----------|----------|

| 10.0  | P | T02 | 0.000000 | 0.000000 |

| 20.0  | P | T03 | 0.000000 | 0.000000 |

| 26.0  | P | T04 | 0.000000 | 0.000000 |

| 32.0  | P | T05 | 0.000000 | 0.000000 |

| 40.0  | P | T06 | 0.000000 | 0.000000 |

| 48.0  | P | T07 | 0.000000 | 0.000000 |

| 60.0  | P | T08 | 0.000000 | 0.000000 |

| 100.0 | P | T09 | 0.000000 | 0.000000 |

| 120.0 | P | T10 | 0.000000 | 0.000000 |

| 216.0 | P | T11 | 0.000000 | 0.000000 |

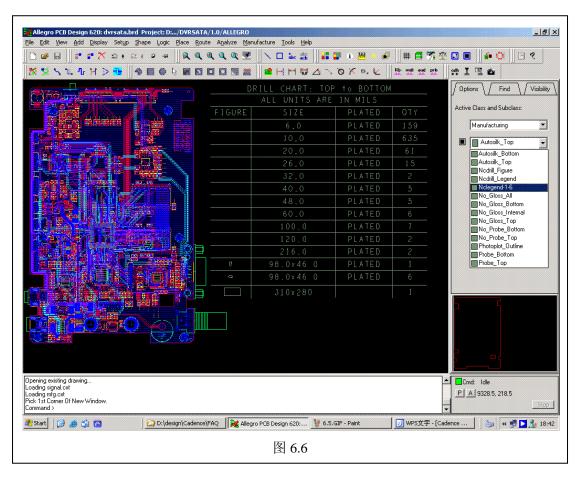

对比图 6.12, 可知这是圆孔的钻头表,显然,98X46 的 7 个条孔并没有生成铣孔文件!

| 0      | RILL CHART: TOF | to BOTTOM |     |

|--------|-----------------|-----------|-----|

|        | ALL UNITS ARE   | IN MILS   |     |

| F]GURE | SIZE            | PLATED    | QTY |

|        | 6,0             | PLATED    | 159 |

|        | 10.0            | PLATED    | 635 |

|        | 20.0            | PLATED    | 61  |

|        | 26.0            | PLATED    | 15  |

|        | 32.0            | PLATED    | 2   |

|        | 40,0            | PLATED    | 5   |

|        | 48.0            | PLATED    | 5   |

|        | 60.0            | PLATED    | 6   |

|        | 100.0           | PLATED    | 7   |

|        | 120.0           | PLATED    | 2   |

|        | 216.0           | PLATED    | 2   |

| 0      | 98.0×46.0       | PLATED    | 1   |

| 0      | 98.0x46.0       | PLATED    | 6   |

图 6.12

准备铣孔工具表文件: ncroutebits.txt

任意使用 TXT 纯文本编辑环境, 创建文件 ncroutebits.txt, 增加 98X46 条孔用的钻头: 46mil 文件内容如下:

0.046 T012

# 注意:单位是 Inches,不是 mil

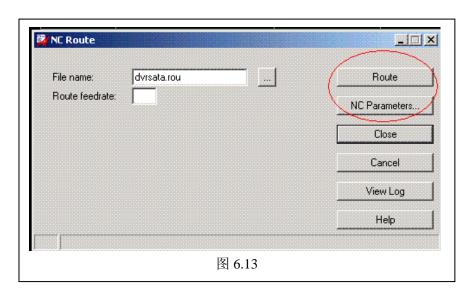

调用 Manufacture\NC\NC Route 得到图 6.13,由于前面已经设置过 NC Parameters,可以不用再设置,不过最好在这里还是检查一下。由于当前工作目录下已经准备好了文件ncroutebits.txt,按 Route 应该可以生成铣孔文件了......

# 总结 Allegro PCB 制图规定:

- 1) PCB 图只能用英制(Inch、Mil), Symbol 元件可以用公制(mm)

- 2) PCB 图绘图精度为: 0.1Mil, Symbol 元件可以用 0.1mm

- 3) Artwork 输出文件 (.art) 使用英制, 精度格式: 2.5, 设备类型: Gerber RS274X

- 4) 钻孔(.drl)和铣孔(.rou)输出文件使用英制,精度格式: 2.5

- 5) 所有的 PCB 文件必须有 Artwork 的 View film,以方便别人看图。参见 Artwork 要素表

# 7、用 CAM350 检查加工文件

这些文件是(\*.art、\*.drl、\*.rou),基本上所有 PCB 厂家支持 CAM350,并且该软件与 Allegro 配合也最好。以下示例使用第 6 章描述的 6 层板结构、CAM350Ver9.0 软件。

## 7.1、CAM350Ver9.0 导入 Gerber 文件

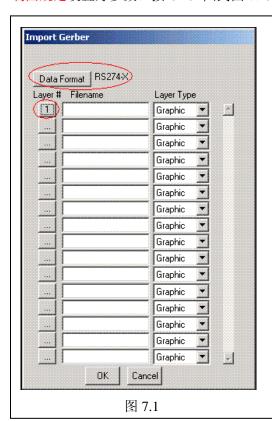

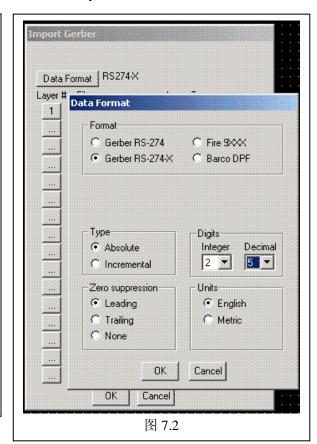

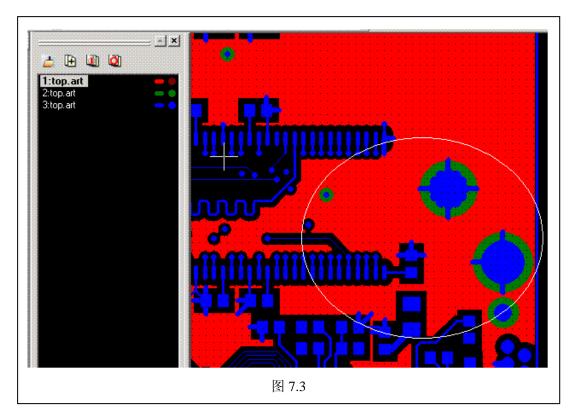

调用 File\Import\Gerber Data, 见图 7.1, 按 Data Format 设置参数, 见图 7.2, 根据 Allegro PCB 制图规定设置好参数。按 OK, 回到图 7.1, 按 1, 导入 top.art, 按 OK, 得到图 7.3

35

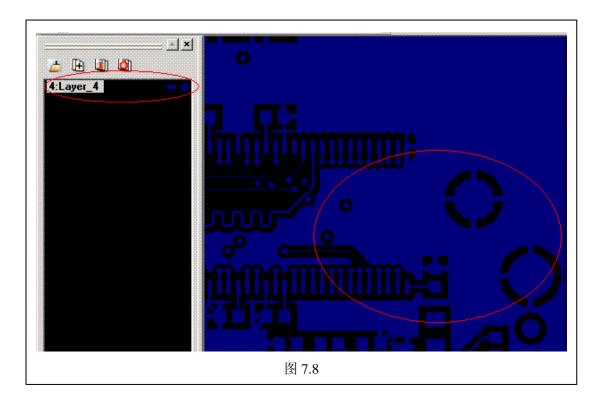

你可能已经注意到: 就一个 TOP 铜层怎么变为 3 个,而且"白圈"区域中的绿色在 Allegro 的 PCB 图中应该是不存在的....? 实际上在 CAM350 中这不是错误,而是不同要素分层显示的结果。但对于那些 CAM350 使用不熟悉的 PCB 厂家见到这种情形,因为不知道怎么取舍,就可能把你的 PCB 做错了.....

# 7.2、CAM350Ver9.0 融合多层为单层

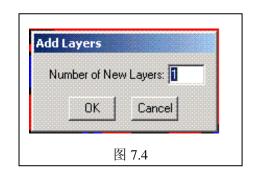

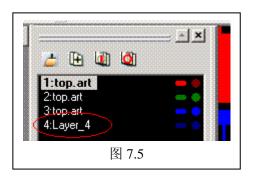

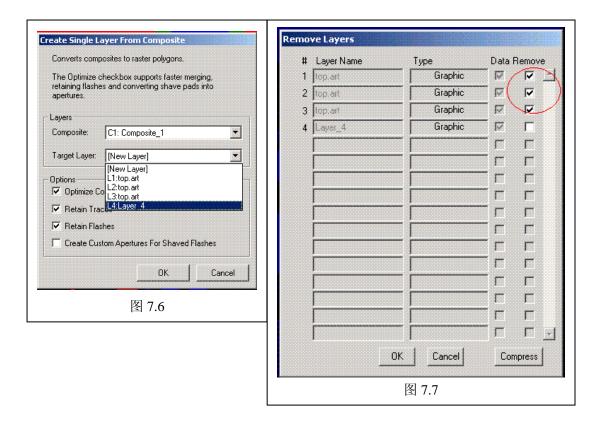

调用 Edit\Layers\Add Layers 添加一个层,见图 7.4,按 OK,后,见图 7.5

可以看到现在多了个 Layer\_4 的层,调用 Utilities\Convert Composite, 见图 7.6,对话框中选 Layer\_4,按 OK,等待融合完毕。调用 Edit\Layers\Remove 删除 Layer\_4 以外的层,见图 7.7,选择后,按 OK,后面会出现几个确认对话框,一路 OK 按下去(最好还是看看对话框内容),出现图 7.8 结果。现在除了颜色、层名和 Allegro 不同外(Allegro 应该是红色),其它都应该相同了,并且 PCB 厂家的困惑也消除了。

# 7.3、修改融合后的层名和颜色

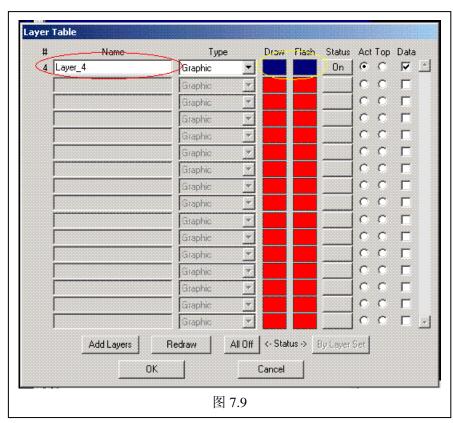

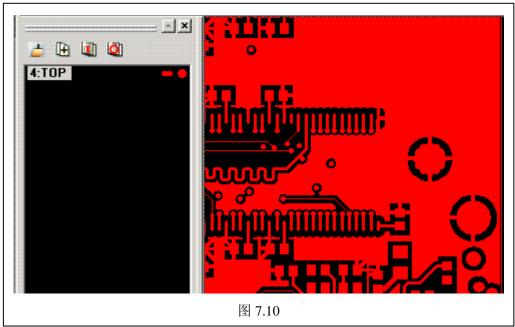

调用 Tables\Layers,如图 7.9,将 Layer\_4 改为: TOP,将 Draw 和 Flash 改为:红色,完成后按 OK,看到图应该象图 7.10

#### 7.4、保存文件

因为要融合的文件太多, 所以, 每融合成功一个光绘文件就保存。这是个好习惯...

# 7.5、检查钻孔(.drl)和铣孔(.rou)文件

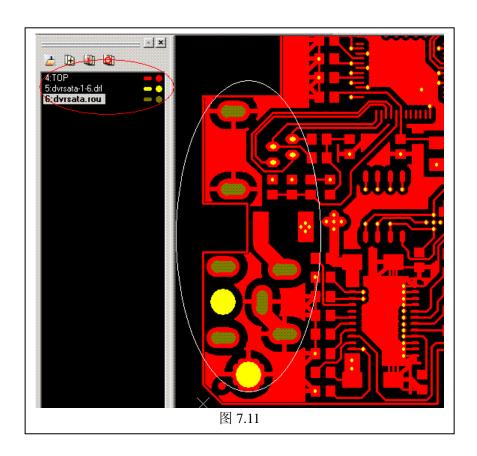

调用 File\Import\Drill Data 导入钻孔文件、调用 File\Import\Mill Data 导入铣孔文件,可以看到与图 7.11 类似的图,别忘了导入钻孔和铣孔文件时,设置参数与图 7.2 保持一致!!! 成功后保存文件。

# 7.6、用同样的方法融合其它的光绘文件 重复 7.1-7.4 过程:导入不同文件、融合、改层名、定颜色、保存。 注意:

- 1) 如果导入的光绘文件只有一个层,就不需要融合处理,直接改层名、定颜色...

- 2) CAM350 的层名只能容纳 15 字符,因此,BOTTOM\_SOLDERMASK 只好命名为BOTTOM\_SOLDER

- 3) 钻孔的层名为 NC\_DRILL

- 4) 铣孔的层名为 NC\_ROUTE

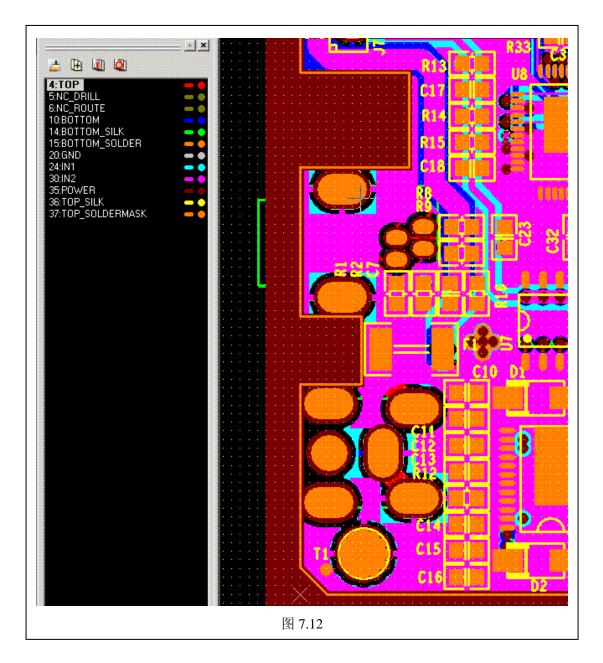

处理后大概会像图 7.12

# 7.7、融合后的层重定层序

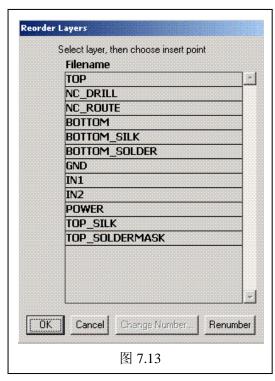

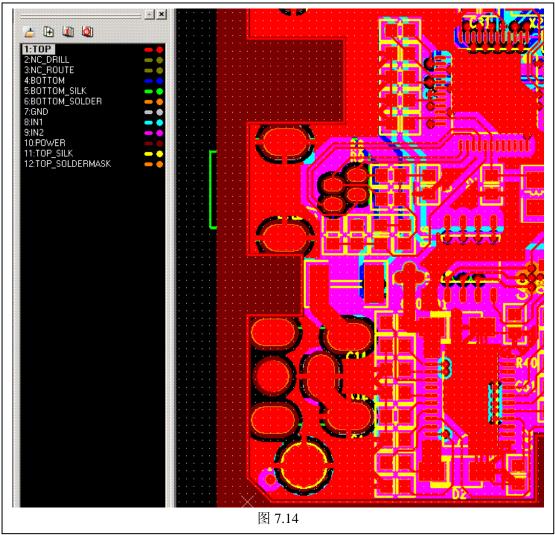

调用 Edit\Layer\Reorder, 如图 7.13, 按 Renumber 按钮后, 按 OK 后如图 7.14, 对比与图 7.12 与图 7.14 在层序号的不同....

另存文件(以 CAM350 VER8.7 格式)为:项目名.cam,比如: dvrsata.cam(dvrsata 为项目名)

#### 7.8、检查文件

#### 重点检查项目:

- 1) 钻孔和铣孔大小、位置是否正确?

- 2) 钻孔和铣孔是否有偏心的现象? 详见 6.4 部分 Allegro 的 bug 描述...

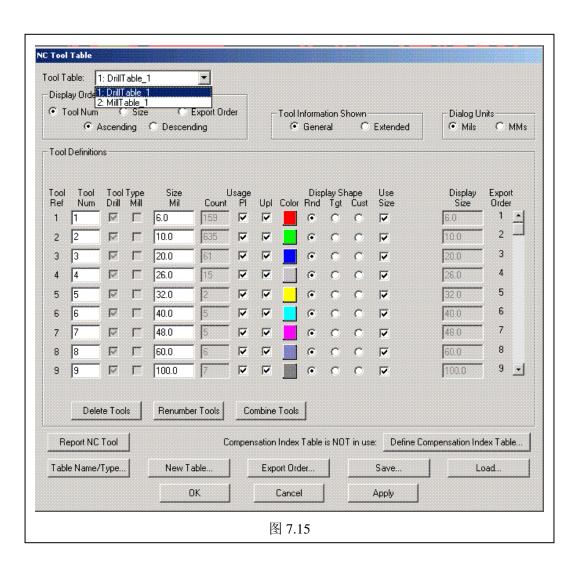

- 3) 钻孔和铣孔数量是否正确?调用 Tables\NC Tool Tables (见图 7.15),与 Allegro 生成的 NC Legend 表对比数量

#### 辅助检查项目

- 1)调用 Analysis 下的功能检查,取决于你对 CAM350 软件的熟悉程度

- 2) 不同的铜薄层是否错位

- 3) 你的图纸特别需要留意的地方

# 8、引用设计模块

#### 8.1、前言

不论是 ORCAD 的原理图 (\*.DSN) 或 ALLEGRO 的 PCB (\*.BRD) 都可以成为模块,并被其它的设计项目引用,以提高设计效率。通常下列两种情形需要做这样的事:

- 1) 一个 PCB 包含多个相同模块,如:多路调音台、多路总加表、多路......

- 2) 一个可以模块化的大型复杂 PCB,可以多人协作....当然,这种模式与 Cadence 的网络模式多人协作不相同。

在正式开始前,我们假定你已经具备如下技能:

- 1) ORCAD 的层次(hierarchical)原理图应用

- 2) ALLEGRO 的 PCB 实践

- 3) ORCAD + ALLEGRO 的联合应用

#### 8.2、实施步骤

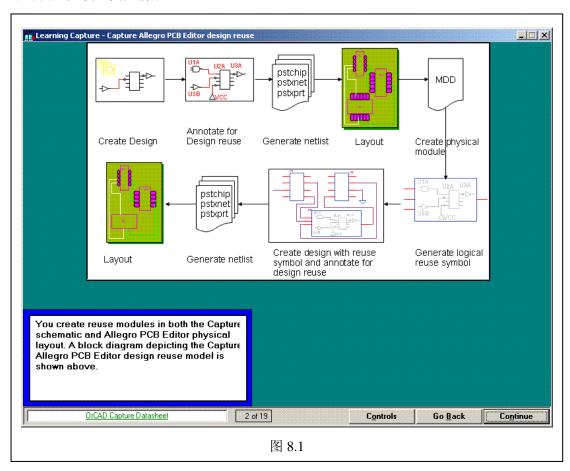

在 ORCAD 的 HELP (LEARNING) 有简单的讲解(图 8.1) 和介绍,不过我们的过程与它不尽同,更接近实际情形……

下面我们用一个双通道的 CLASS-D 功率放大器说明,步骤大致如下:

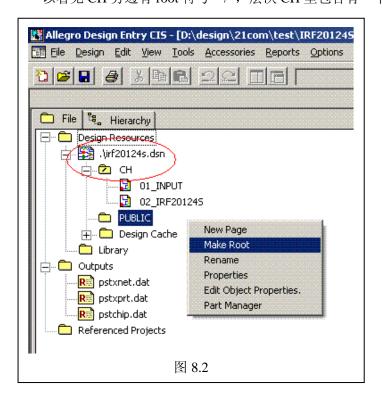

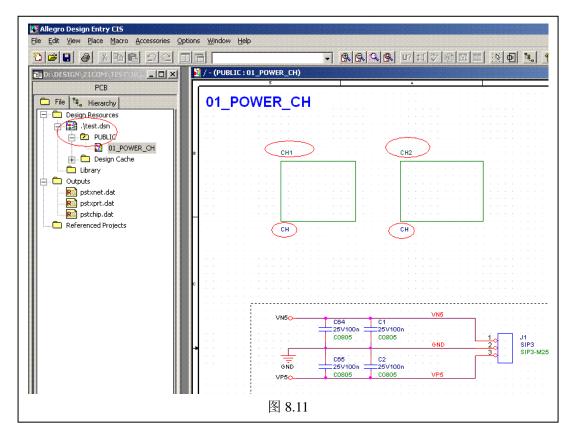

1)设计一个原理图 DSN(可能这个图以前已经做完了): 顺便提一下,如果包含多个层次图,必须有一个唯一的 root(系统默认第一个创建的层次为 root),你也可以改变 root,(鼠标点该"层"、左键、没现?哈哈!我使左手鼠标的),如果你用右手鼠标,当然是点右键!!! 见图 8.2(请记住原理图集名 IRF20124S 和层次名 CH,后面会用到),你可以看见 CH 旁边有 root 符号"/",层次 CH 里包含有一个通道的原理图....

- 2) 为 CH 层次图标注唯一位号,annotate (可能这步骤以前也做完了): 见图 8.3,必须选择 Occurrences 模式,而不是默认的 Instances 模式! Why? See help...

- 3) 为 CH 层次图 DRC 检查 (可能这步骤以前也做完了): 建议使用图 8.4 设置项,并使用与 annotate 下设置相同的 Occurrences 模式!

- 4) 为 CH 层次图创建 netlist (可能这步骤以前也做完了): 你如果能通过上一步,这步应该不会有问题。

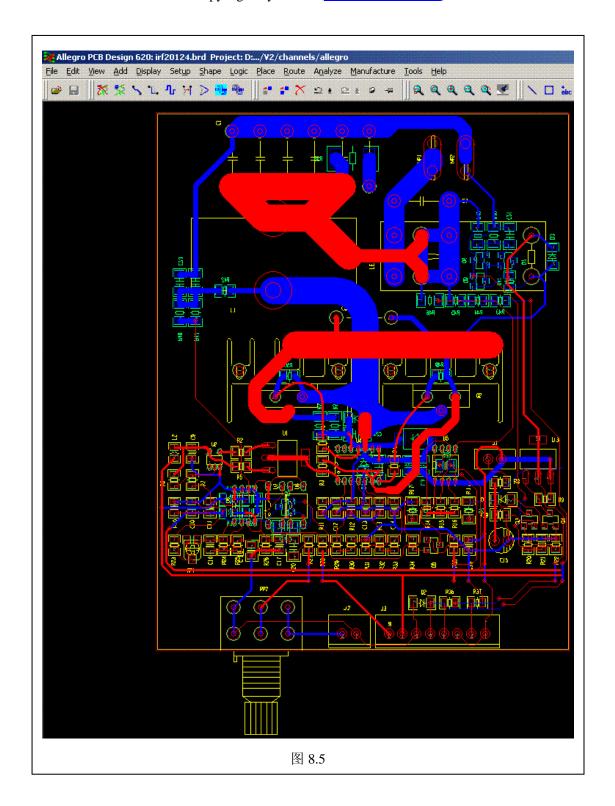

- 5) 用该 CH 层次图的 netlist 排个 PCB 图 (可能这步骤以前也做完了): 排好的板可能会像 图 8.5

前面 5 个步骤应该都没有问题,如果你以前用 ORCAD + ALLEGRO 做过图的话。后面的步骤才是这部分的....大餐....隆重登场!

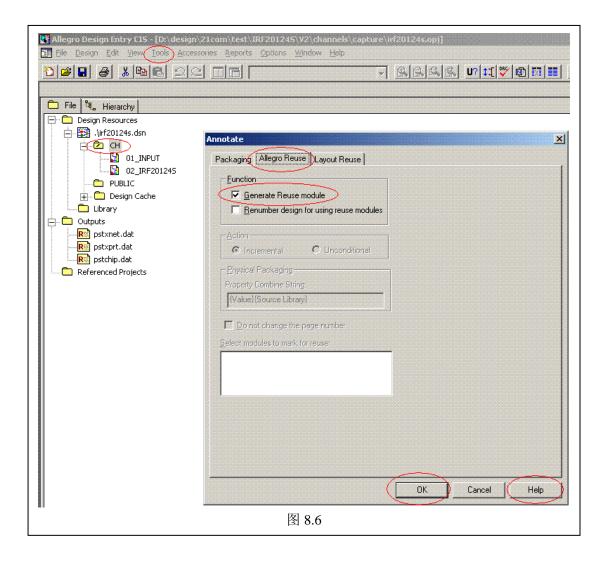

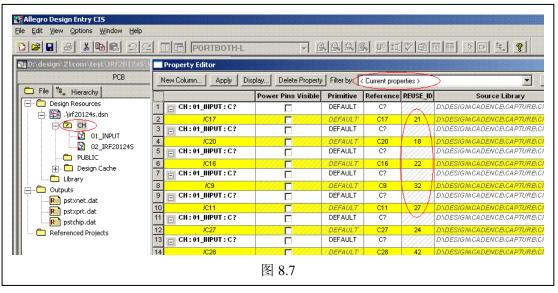

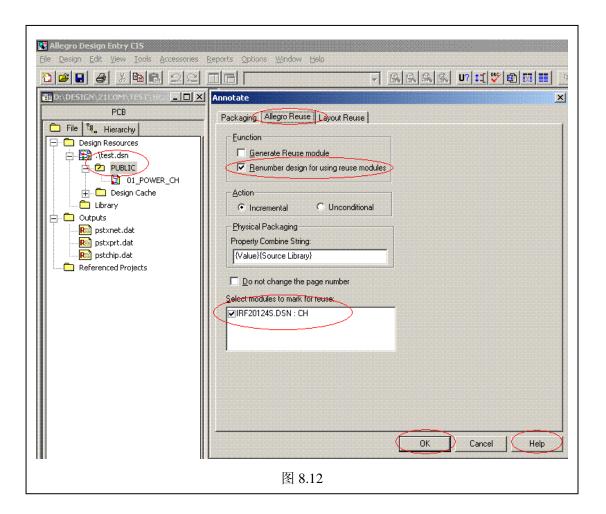

6) 为引用的层次图 CH 生成 REUSE\_ID: tools\annotate\allegro reuse,见图 8.6。你一定要在这个选项卡里按 OK,否则,不能生成。可以用图 8.7 来检查是否成功生成。

- 7)为引用的层次图 CH 生成包含 REUSE\_ID 的 netlist: 如果创建成功的话,打开 pstxprt.dat 网表文本文件,你应该可以看到每个 PART NAME 子项目名下都有 REUSE ID 属性。

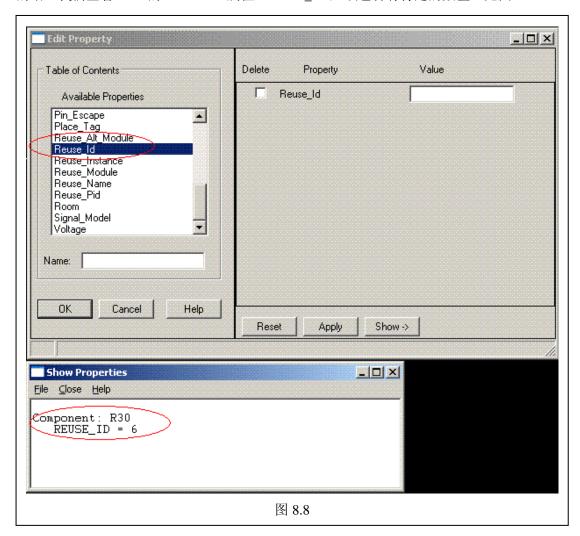

- 8) 为引用的 PCB(\*.brd)模块文件导入包含元件 REUSE\_ID 属性的 netlist: 如果没有问题的话,我们查看 PCB 的 SYMBOL 属性,RUSE\_ID 应该包含有特定的数值,见图 8.8

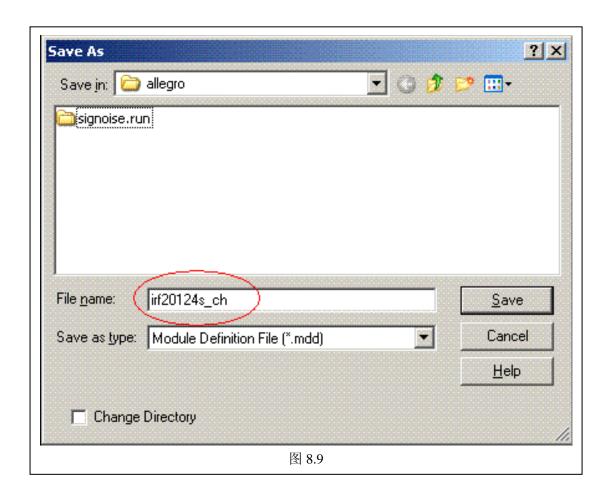

9) 为包含 REUSE\_ID 的 PCB 创建模块(\*.mdd)、并按规定约束命名: 点 allegro 菜单 tools\Create Module,选择所有目标物件,确定并选择基点(也就是模块的元点),在对话框内,填入模块名称: irfs20124s\_ch(图集名\_引用层次名),你应该还记得步骤(1)的提示吧。你可以不用这个命名规定约束,但你必须给引用层次原理图的每个元件增加REUSE\_NAME 属性,并给这个属性赋予你自定义的 PCB 模块名(那将是个巨麻烦的事)! 见图 8.9,同时,请记住这个模块的存放位置,后面设置模块搜寻路径时,会用它的路径....

你可以看出:上述第 6 至 9 步骤,实际上是给需要引用的层次原理图和 PCB 图做 REUSE 的模块化处理.....

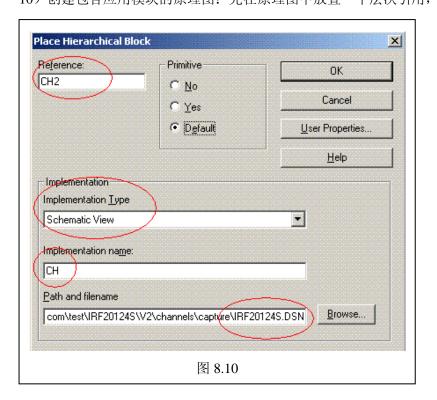

10) 创建包含应用模块的原理图: 先在原理图中放置一个层次引用, 见图 8.10

Reference 表示参照名,类似元件位号,不能重复。

Implementation Type 表示引用类型,选 Schematic View

Path and filename 表示引用(包含完整路径)原理图集名(包含需要的层次原理图,实例中是 IRF20124S.DSN, 见图 8.2 描述)

Implementation 表示引用原理图集中的层次名(实例中是 CH, 见图 8.2 描述) 完成后的图太概会像图 8.11, 由于这两个引用只有由源关联,没有其它关联的信号,所

完成后的图大概会像图 8.11,由于这两个引用只有电源关联,没有其它关联的信号,所以没有层次信号连接的 port

- 11) 重新标注包含唯一元件位号引用原理图:见图 8.12 (类似图 8.6),如果引用了多个层次模块,记住把他们都选上,没有引用的千万别选!

- 12) DRC 检查包含引用的原理图:参考步骤(3)

- 13) 为包含引用的原理图创建 netlist: 如果创建成功的话,打开 pstxprt.dat 网表文本文件,你应该可以看到每个 PART\_NAME 子项目名下都不仅包含 REUSE\_ID 属,还多出了 REUSE\_NAME 和 REUSE\_INSTANCE 属性。

- 14) 在 PCB 中导入包含 REUSE 属性的 netlist: 打开 PCB 的元件放置对话框,选择模组放置,应该可以看到有两个模组。模组在 PCB 里面相当于组群(Group),你可以移动他们作为 Group。见图 8.13

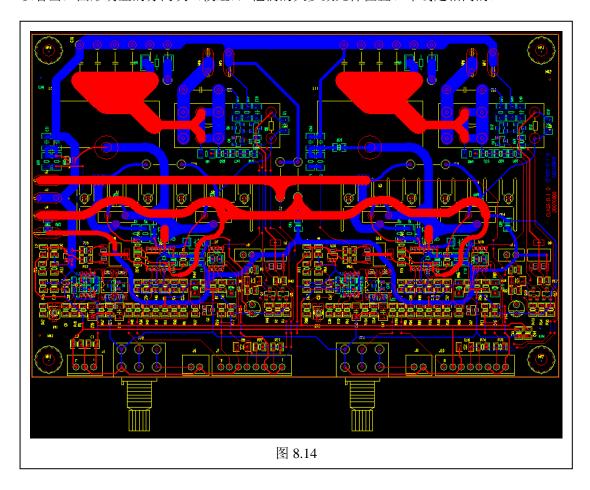

15) 放置剩余的其它元件,完成剩余布线:完成后的图大概会像图 8.14,对比图 5.5,你可以看出:图形明显的分两块(模组),他们的大多数元件位置、布线是相同的。

# 9、多层 PCB 排版流程

#### 前言

多层 PCB: 指四层或以上

该流程是对多层 PCB 排版的一般性必要步骤描述,通过这些步骤的检查和实施,有助于提高 PCB 的工艺规范性、一致性。并尽可能的缩短 layout 时间、避免遗漏;在保证原理图正确的情况下,提高多层 PCB 一次性成功率。同时,该流程也可作为从事多层 PCB 排版 Layout 的入门参考。

# 1、布局和原则

(示范案例: cc1100v1-m6.brd)

一个好的布局和元件位置,不仅能满足:外设接插件的位置要求、电路的性能指标、低 EMI 辐射,还能降低布线难度、提高布通率、减少布线时间,并且方便焊接、调试、维修。

- 1.1、以功能模块为中心区域的外围

- 1.2、功能 IC 的退耦: C、LC、RC....

- 1.3、给功能模块间的信号(如: BUS)连接预留走线空间,并使其最短距离、避免交差

- 1.4、连接和调试插座尽可能在板四周边缘

- 1.5、元件放置要考虑元件位号的空间,避免焊接误解、并易于焊接工艺

- 1.6、为连接插座预留功能描述字符的空间

- 1.7、为 PCB 板描述(如: 板号、版本、LOGO)预留空间

- 1.8、在保证性能的情况下,尽可能的对齐元件

- 1.9、充分考虑焊接、调试、维修的便利。

- 1.A、机械安装孔尽可能对称、距离取整数(单位: mm)

- 1.B、供机外使用的插座(如:电源、USB、RCA、RJ45....),其中心距取整数(单位:mm), 并留够足够的距离,以考虑插拔方便....

- 1.C、测试点、编程器件和冗余后备器件是否方便调试

- 1.D、安全规范考虑

#### 2、手动布线

(示范案例: cc1100v1-m6.brd)

完成自动布线无法实现的特定连接。

- 2.1、退耦

- 2.2、与功能 IC 直接相关的外围元件

- 2.3、关键信号线: 差分对、时钟、电源和分割、尽可能减少 VIA 的绕线、有特殊层或(和)宽度或(和)走向的信号线...

- 2.4、EMI 的避让

Cadence 应用注意事项 V1.6 CopyRight By 王卫无 (wolver@21com.com) 2007-11-20

2.5、电源长线(大于 2inch:50mm)辐射的退耦考虑

### 3、自动布线

(示范案例: cc1100v1-r6.brd)

功能模块间的连接,让计算机给我们提供最优化的走线路径,从繁杂的体力劳动中解放出来。

- 3.1、根据连接方向 Fanout Via (手动)

- 3.2、设置连接规则:远距严格、近距放松

- 3.3、设置走线避让(Route Keepout)、过孔避让(Via Keppout)

- 3.4、设置特殊网络使用的线宽和过孔

- 3.5、设置不同网络自动布线的优先级

- 3.6、使用自动布线工具测试布线

#### 4、对自动布线后的手工调整

(示范案例: cc1100v1-r6m1.brd) (示范案例: cc1100v1-r6m2.brd)

是对自动布线的结果优化,以及自动布线不满足特定需求的变更。

- 4.1、是否有未连接的 Pin

- 4.2、删除多余的 Via

- 4.3、调整走线与 Pad 和 Via 距离太靠近的部分

- 4.4、对无 Power 和 Gound 隔离的临近层信号做最小化堆叠调整

- 4.5、对规则宽松的部分做紧缩调整(如: DDR2RAM)

- 4.6、对完成布线的 PCB 做 SI 仿真 (理论对实践的参考)

#### 5、加工工艺调整

(示范案例: cc1100v1-r6m3.brd) (示范案例: cc1100v1-r6m4.brd) (示范案例: cc1100v1-r6m5.brd)

(示范案例: pcb\_tech.dxf) (示范案例: layer.txt)

在满足电性能需求的情况下,调整 PCB 要素,降低 PCB 加工和生产工艺要求,减少歧意引发的最终成品故障,同时还能达到美化 PCB 成品的作用。

- 5.1、加宽线路(如: Top 和 Bottom,与 Pad 连接的 Neck)

- 5.2、全局修改元件位号字符和 Pin Number 大小

- 5.3、位号重排序: Top 从左到右、从下到上; Bottom 从右到左、从下到上

- 5.4、同步原理图(如:将重排序的位号 Back Annotate 回原理图),并检查正确性

- 5.5、调整位号方向和位置: Top 水平方向向从左到右、垂直方向从下到上; Bottom 水平方向向从右到左、垂直方向从下到上 靠近元件,但不被元件、Pad、Via 遮盖,尽可能的领近对齐

- 5.6、给接插件和 PCB 放置功能描述字符或 Logo (方向规则与 5.5 同)

- 5.7、给特定的线或 Shape 增加 Soldmask

- 5.8、导入 PCB 加工技术说明文件,并填写符合本 PCB 工艺的要求内容

- 5.9、铺铜、减少孤铜,并做 DRC 相关的所有检查

- 5.A、生成 Gerber 文件、并检查它们。为 PCB 制造商作 Gerber 文件的必要说明

(未完、待读)