## Analog - Voltage-to-Frequency Converter

# AN2161

Author: Victor Kremin Associated Project: Yes Associated Part Family: CY8C24xxx, CY8C27xxx GET FREE SAMPLES HERE Software Version: PSoC Designer™ 4.0 Associated Application Notes: AN2041, AN2044

### **Application Note Abstract**

This Application Note demonstrates how to build a voltage-to-frequency converter using one continuous time PSoC® block and one switched capacitor PSoC block. The converter does not utilize the CPU during operation.

### Introduction

Voltage-to-frequency (V/F) converters are widely used in industrial electronics, frequency-shift keying modulators, phase-locked loop systems, analog-to-digital converters, isolation amplifiers, etc. Even though these converters are produced as standalone devices, they still require several external components and are relatively expensive compared to modern low-cost analog integrated circuits.

PSoC allows the designer to build the V/F using only one continuous time (CT) analog block and one switched capacitor (SC) analog block without any external analog components. All digital blocks, and the CPU, are at user disposal. The designer will get a useful device function with virtually no additional cost or extra components.

Moreover, the proposed V/F converter produces both meander and symmetric sawtooth signals, which are useful for applications such as analog PWM modulators and capacitance meters.

### **Converter Operation Theory**

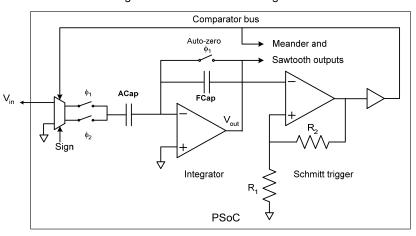

The converter, shown in the block diagram of Figure 1, consists of a reversible integrator and a Schmitt trigger. The integrator has been built around a type C SC block with an analog modulator. The Schmitt trigger has been built using a CT block with internal resistors. For more details about SC block operation, please refer to Application Notes AN2041 "Understanding Switched Capacitor Analog Blocks" and AN2044 "Signal Rectification, Using Switched Capacitor Modulators."

Figure 1. Converter Block Diagram

The integrator output voltage is determined by its output voltage from the previous sample and the state of the Schmitt trigger. The sign bit in the SC block is set to 1, which makes the integrator gain negative. The output state of the Schmitt trigger follows the polarity of the integrator output. When the Schmitt trigger output is negative, each column sample clock period decreases the integrator output voltage,  $V_{out}$ , by  $\Delta V$ . This increment is determined by the input voltage,  $V_{in}$ , and the block Acap-to-Fcap ratio:

$$\Delta V = V_{in} \frac{ACap}{FCap}$$

Equation 1

When  $V_{\text{out}}$  reaches the lower Schmitt trigger threshold,  $V_{\text{low}}^{\text{h}}$ , the trigger switches to the opposite state, driving the comparator bus high. This changes the integrator input voltage sign, causing the integrator signal to rise with the same  $\Delta V$  at each column sample clock period. This process will continue until the integrator signal reaches the Schmitt trigger upper threshold value,  $V_{\text{up}}^{\text{h}}$ . At this point, the trigger drives the comparator bus low again, and the process repeats.

The Schmitt trigger thresholds are determined by supply voltage, selected analog ground and the ratio of the internal resistors. The Schmitt trigger thresholds,  $V^{\rm th}_{\rm low}$  and  $V^{\rm th}_{\rm up}$ , are calculated easily using Equation 2 (all voltages are AGND related).

$$V^{th}{}_{low} = \frac{R_1}{R_1 + R_2} - V_{AGND};$$

$$V^{th}{}_{up} = \frac{R_1}{R_1 + R_2} (V_{dd} - V_{AGND})$$

Equation 2

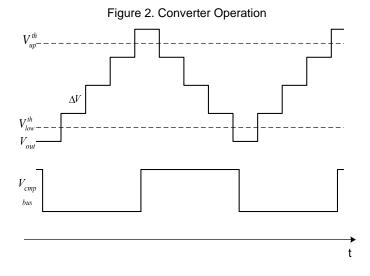

The SC integrator is a discrete system, in that the integrator output voltage can only be changed during discrete time intervals. To switch the Schmitt trigger, the integrator signal should be greater than or equal to the trigger threshold. This results in two additional integration column sample clock periods for each output signal, half-period integration time. This is shown in Figure 2.

The upper bound,  $N_{sup}$ , and the lower bound,  $N_{inf}$ , for halfperiod integration time in units of column sample cycles can be estimated by using the following equations:

$$N_{\rm sup} = \left[\frac{V_{up}^{th} - V_{low}^{th}}{\Delta V}\right] + 2; \ N_{\rm inf} = \left[\frac{V_{up}^{th} - V_{low}^{th}}{\Delta V}\right] \ \text{Equation 3}$$

The [] denote the integer part. The sample period for the SC block is the column clock signal, divided by 4, or:

$$T_i = \frac{4}{F_c}$$

Equation 4

$F_c$  is the column frequency. Supposing  $N_{\mathit{inf}}>>$  2,  $N_{\mathit{cyc}}$  =  $N_{\mathit{inf}}$  ~  $N_{\mathit{sup}}$  .

This takes into account that a single period total integration time is a doubled half-period time:

$$T_{out} = 2T_i \cdot N_{cyc}$$

Equation 5

Combining Equations (1) - (5), the converter output frequency is given by:

$$F_{out} = \frac{F_c}{8} \cdot \left(1 + \frac{R_2}{R_1}\right) \cdot \frac{ACap}{FCap} \cdot \frac{V_{in}}{V_{dd} - V_1 - V_0} \quad \text{Equation 6}$$

Note It is useful to substitute:

$$\beta = \left(1 + \frac{R_2}{R_1}\right)^{-1}$$

Equation 7

April 14, 2004

This is because  $\beta$  can be assigned as a *RefValue* parameter in PSoC Designer when a programmable threshold comparator is used as a Schmitt trigger building block. So, the final expression for the V/F output frequency,  $F_{out}$ , is given by:

$$F_{out} = \frac{F_c}{8\beta} \cdot \frac{ACap}{FCap} \cdot \frac{V_{in}}{V_{dd} - V_1 - V_0}$$

Equation 8

A more accurate expression for V/F converter output frequency can be obtained using the value of  $N_{inf}$  for an output signal half-period integration time estimation:

$$F_{out} = \frac{F_c}{8} \left\{ \beta \frac{V_{dd} - V_1 - V_0}{V_{in}} \frac{FCap}{ACap} + 2 \right\}^{-1} \quad \text{Equation 9}$$

### **PSoC Implementation**

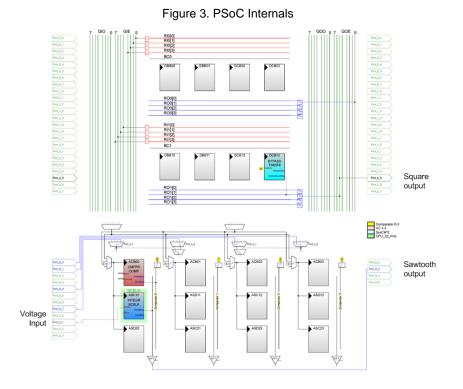

The V/F converter placement is shown in Figure 3. The converter has been placed in the *Column\_0*. The programmable threshold comparator has been used to make the Schmitt trigger. The feedback resistors were rerouted manually in the firmware to the non-inverting operational amplifier input. The inverting input was directly connected to the integrator output. Because the integrator uses auto-zero mode, the SC output alternates between demanded output value and the AGND level for each clock period. However, the integrator has no influence on converter operation due to Schmitt trigger hysteresis. The designer can disable auto-zero mode in the integrator when neither sawtooth signal symmetry nor 50% duty cycle for a rectangle signal are important. This allows for larger output maximum frequencies.

In this example, the integrator has been placed in ASC10. The configurable SC block has been used to make the integrator. The *ComparatorBus\_0* was set as the modulator source. The **FCap** was set to 32 and the **ACap** to 1 to get the maximum possible integration steps per given input voltage. The input signal comes directly from the P2[1] input pin. The SC block serves an additional level-shifting function. To process PSoC  $V_{ss}$  ground-related input signals, the **ARefMux** reference was set to REFLO and the **RefMux** was set to  $V_{dd}/2 \pm V_{dd}/2$ . Users should set **ARefMux** to AGND when they want to work with AGND-related input signals, such as those that come from another analog block. The integrator output voltage is sent to the P0[3] pin.

The Timer\_8 User Module is required to pass the comparator bus signal to an external pin. The timer function has been changed to the CRC and pass mode has been enabled in the firmware. This module is required only when the digital V/F converter output is directly passed to an external pin. If output is sent to another digital module, the pass block is not required.

#### **Test Results**

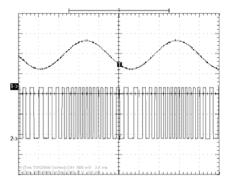

Figure 4 illustrates the converter output signals. Figure 5 demonstrates use of the converter as a frequency modulator.

#### Figure 4. Converter Output Signals

Figure 5. Converter as Frequency Modulator

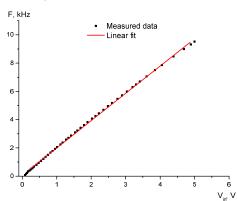

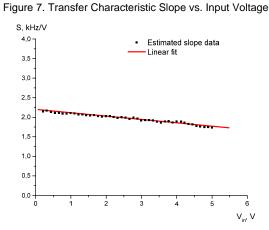

To study converter transfer characteristics, the output frequency has been measured for various input voltages. See Figure 6. The relation between minimum and maximum frequency is near 100, which makes the converter suitable for many practical applications. Figure 7 depicts the transfer characteristic slope as a function of input voltage. Note that the slope decreases with increasing input voltage due to the constant value in the half-period integration time. See Equation (3). To examine this, differentiate Equation (9) by V<sub>in</sub>. Note that some noise in the output data is caused by the low cost 3.5-digit, multimeter used for measurement.

Figure 6. Transfer Characteristics

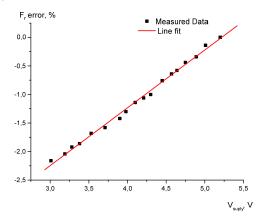

To study the influence of power supply level on output frequency, the PSoC supply was varied from 3.0V to 5.25V and the input voltage was fixed to half the supply level. Figure 8 illustrates the relative frequency variation obtained during these measurements. The 5.25V supply was used as a reference level.

Figure 8. Output Frequency Variation vs. Supply Level

Finally, the difference between calculated and measured frequencies was estimated. For the 2.5V input signal and 5V supply level, the internal 24 MHz generator measured the frequency as 4993 Hz. The frequency calculated from Equation (8) is near 5212 Hz, which provides the relative frequency error -4.2%. The primary error source is the assumption that the difference between comparator thresholds is exactly equal to that of the integer number of the switched capacitance integrator voltage. As a result, the real half-period integration time is longer than the time evaluated by Equation (5). The more accurate equation, (9), predicts the value at 4938 Hz and error at 1.1%.

## **The Design Modifications**

The proposed voltage-to-frequency converter can be used in various applications. Some adaptation may be required to suit some situations. The integrator can be built using a CT block with an external resistor and capacitor. This will reduce possible jitter in the output signal on maximum frequencies, thereby improving the voltage conversion accuracy (when high stability passive components are used!) and linearity because the transfer characteristic slope is constant for the whole  $V_{in}$  range. Because this design uses the power supply value as the converter reference voltage, the output frequency is dependent on the power supply value.

This is fine for sources such as strain gauges and some pressure sensors, which provide the radiometric output signal, but is not very good for devices that supply absolute voltage. In these situations, the two comparators that check the integrator signal relative to the internal reference can be used to switch a "memory cell" such as a Schmitt or LUT-based RS trigger to a control analog modulator.

#### Source

The main routine source code.

```

void main()

CMPPR_COMP_CR0 |= BIT(2); //connect the

RTopMux to opam output

CMPPR_COMP_CR1 = (CMPPR_COMP_CR1 & 0xC0)

| 0x2F; //set NMux and PMux connections

CMPPR_COMP_CR2 &= BIT(6); //The output

latch is always transparent

CMPPR Start(CMPPR HIGHPOWER);

AMD_CR0 = 0x04;

INTEGR_Start(INTEGR_HIGHPOWER);

BYPASS_FUNC_REG = BYPASS_FUNC_REG & 0xFC

0x02;

BYPASS_CONTROL_REG | = 0x03;

BYPASS Start();

while(1); //loops forever here

}

```

#### About the Author

| Name:<br>Title:<br>Background: | Victor Kremin<br>Associate Professor<br>Victor earned a radiophysics diploma<br>in 1996 from Ivan Franko National<br>Lviv University, a PhD degree in<br>Computer Aided Design systems in<br>2000, and is presently working as<br>Associate Professor at National<br>University "Lvivska Polytechnika"<br>(Lviv, Ukraine). His interests involve<br>the full cycle of embedded systems<br>design including various processors,<br>operating systems and target<br>applications. |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Contact: vkremin@lviv.farlep.net

In March of 2007, Cypress recataloged all of its Application Notes using a new documentation number and revision code. This new documentation number and revision code (001-xxxxx, beginning with rev. \*\*), located in the footer of the document, will be used in all subsequent revisions.

PSoC is a registered trademark of Cypress Semiconductor Corp. "Programmable System-on-Chip," PSoC Designer, and PSoC Express are trademarks of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone: 408-943-2600 Fax: 408-943-4730 http://www.cypress.com/

© Cypress Semiconductor Corporation, 2004-2007. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.