## 819 NNW

#### What's New with the PIC18 Architecture Including nanoWatt Technology Features and the Extended Instruction Set

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

What's New with the PIC18 Architecture

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

#### What's New on PIC18

#### Class Goals:

- At the end this class, you will...

- be familiar with PIC18's revised & new modules

- have an understanding of clock switching

- know the "Latest and Greatest"

- know how to use the extended instruction set

- be able to apply nanoWatt technology to your application

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

What's New with the PIC18 Architecture

## Agenda

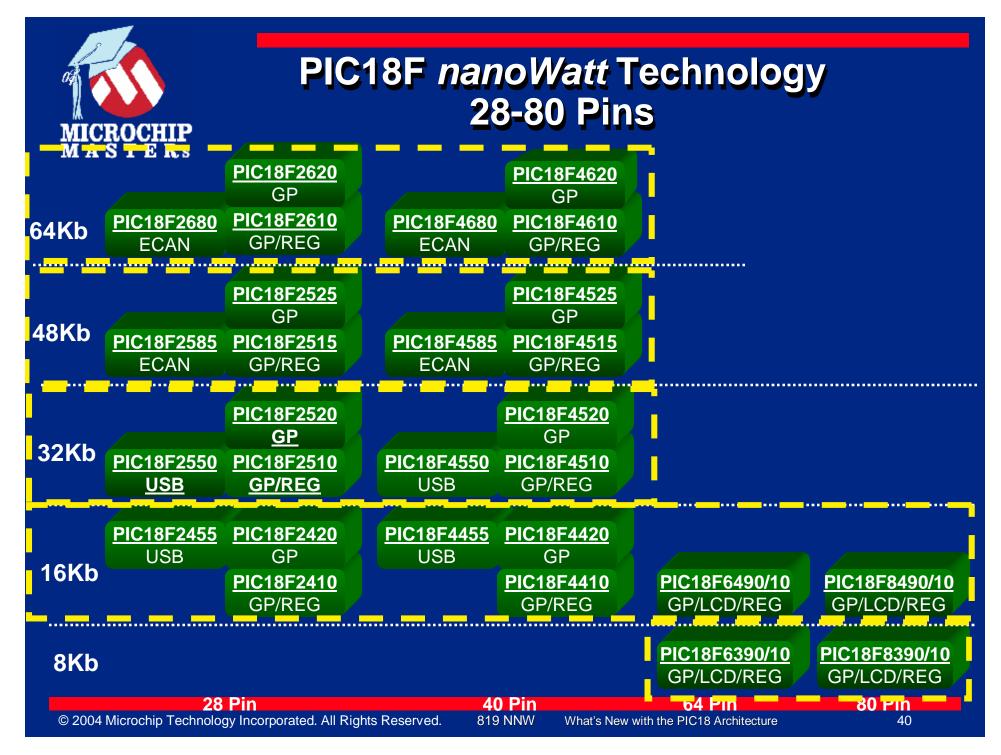

## nanoWatt Technology review **PIC18** Features **Clock System Power Managed Modes PIC18** Devices **Extended Instruction Set** Summary

819 NNW

PDF created with FinePrint pdfFactory trial version www.pdffactory.com

© 2004 Microchip Technology Incorporated. All Rights Reserved.

## What is nanoWatt Technology?

Microchip continues to make improvements over its existing portfolio:

Redesigning Legacy Designing New Modules

Low Power & Greater Application flexibility

- Low Power Timer1

- Two-Speed Start-up

- Fail Safe Clock Monitor

- HLVD

- LCD

- USB

- Internal RC Oscillator

- EUSART

- Variable Boot Block

- Power Managed Modes

- LIN

- Motor Control

- BOR

- ECCP

nanoWatt Technology review **PIC18 Features Clock System Power Managed Modes PIC18** Devices **Extended Instruction Set** Summary

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

What's New with the PIC18 Architecture

## **PIC18 Features: Timer1**

#### Low Power Timer1 Oscillator:

- I 3ua vs 30ua

- Oscillator amplitude is regulated

- Constant current across VDD and Temperature

- Robust operation

- Enabled by T1OSCEN (T1CON<3>)

- Commonly 32.768 kHz for a RTC time base

- User code is responsible for determining when RTC is ready

#### PIC18 Features: 2 - Speed Start-up

#### <u>Two Speed Start-up:</u>

- Used with crystal based modes only

- Immediate code execution

- Automatically switches to Primary

- Code may go back to SLEEP before Primary is ready

- Used for:

- Start from RESET or wake from SLEEP mode

- Primary clocks startup delays

- Crystal / Resonator oscillator start time

- OST delay (counts 1024 oscillator cycles)

- PLL delay (additional 2ms delay for HS/PLL)

- Power-up Timer (PWRT)

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

## **PIC18 Features: FSCM**

#### Fail-Safe Clock Monitor:

- Used to detect a loss of externally-based clocked sources

- During start-up (Reset or Wake from Sleep)

- INTRC/INTOSC provides system clocks until Primary clock is ready (similar to 2-speed start)

- When the primary is ready, an automatic clock switch selects the primary clock

- Dedicated interrupt: OSCFIF

- 1 31 kHz INTRC clock source

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

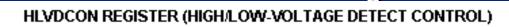

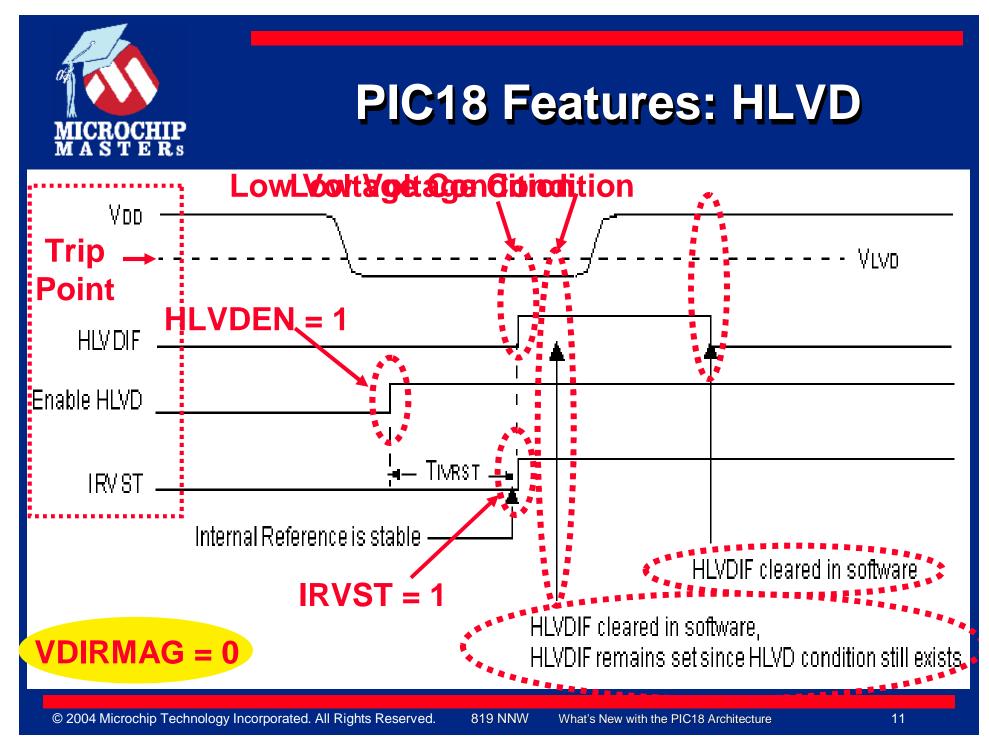

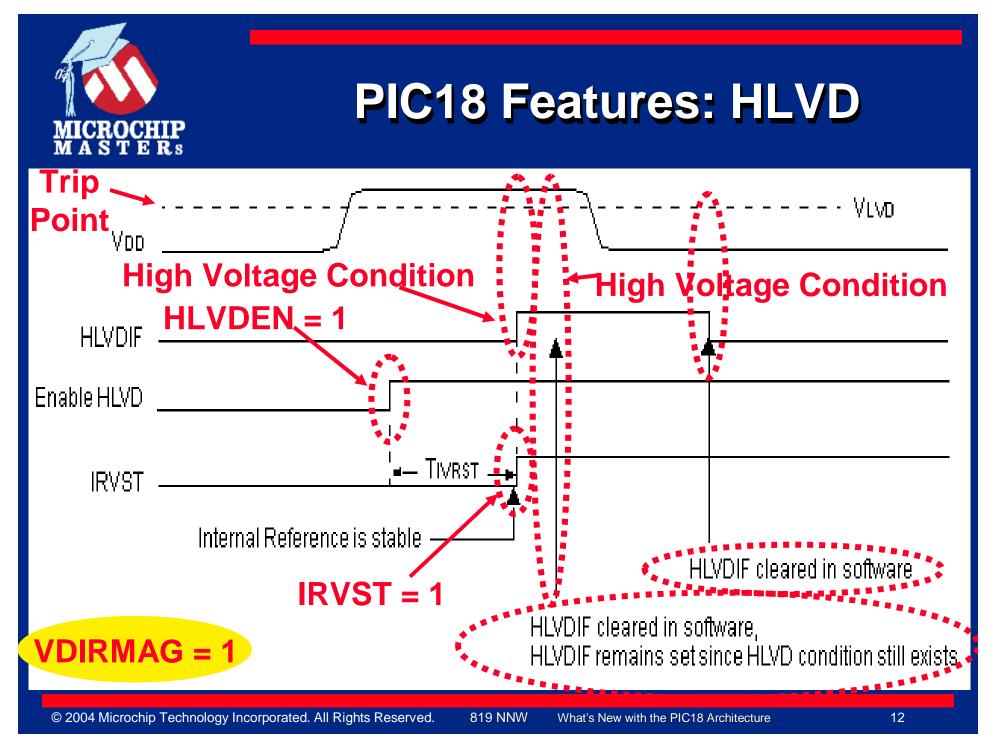

### **PIC18 Features: HLVD**

- High/Low Voltage Detect

- Programmable Voltage trip point

- Programmable direction of change

- VDIRMAG bit: indicates voltage direction

REGISTER 22-1:

bit 7

1 = Event occurs when voltage equals or exceeds trip point (HLVDL3:HLDVL0)

0 = Event occurs when voltage equals or falls below trip point (HLVDL3:HLVDL0)

**VDIRMAG**: Voltage Direction Magnitude Select Bit

- 1 = Event occurs when voltage equals or exceeds trip point (HLVDL3:HLVDL0)

- 0 = Event occurs when voltage equals or falls below trip point (HLVDL3:HLVDL0)

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

| MICROCHI<br>M A S T E R                                                               | P      | PIC18 Features: BOR |                                                                                                  |  |

|---------------------------------------------------------------------------------------|--------|---------------------|--------------------------------------------------------------------------------------------------|--|

| BOR Configuration                                                                     |        | BOREN1:0            | BOI SBOREN bit st be                                                                             |  |

| BOREN1                                                                                | BORENO | SBOREN<br>(RCON<6>) | the configuration bits "OFF".                                                                    |  |

| 0                                                                                     | 0      | Unavailable         |                                                                                                  |  |

| 0                                                                                     | 1      | Available           | *                                                                                                |  |

| 1                                                                                     | 0      | Unavailable         | * BOR enabled in software;                                                                       |  |

|                                                                                       |        |                     | operation controlled by                                                                          |  |

| 1                                                                                     | 1      | Unavailable 🔉       | SBOREN.                                                                                          |  |

| * BOR enabled in hardware<br>in RUN and IDLE modes,<br>disabled during SLEEP<br>mode. |        |                     | BOR enabled in hardware;<br>must be disabled by<br>reprogramming the<br>configuration bits "ON". |  |

© 2004 Microchip Technology Incorporated. All Rights Reserved.

819 NNW What's New with the PIC18 Architecture

13

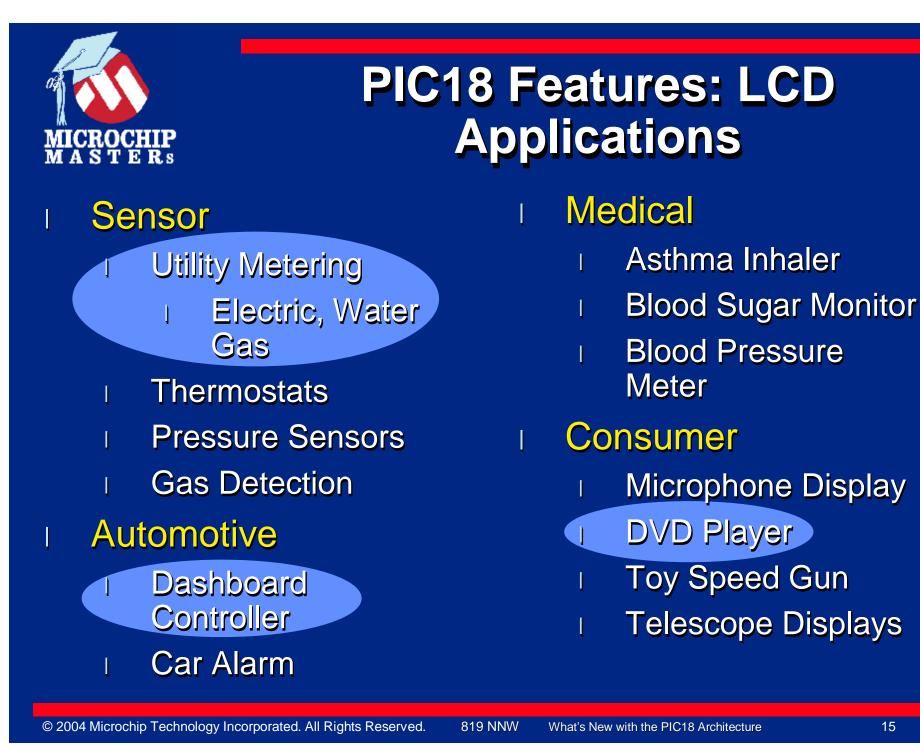

## **PIC18 Features: LCD**

#### Enhanced LCD Module

- Direct Driving of LCD Panel

- Can drive LCD in SLEEP Mode

- Software select segments/pixel

- Programmable LCD Module

- Three Clock sources

- Static, 1/2 or 1/3 bias configuration

Up to 4 Commons: Static, 1/2, 1/3, or 1/4 multiplex

| Device                      | Commons                        | Segments       | Pixels                 | <b>Program Memory</b> |

|-----------------------------|--------------------------------|----------------|------------------------|-----------------------|

| PIC18F6390                  | 4                              | 32             | 128                    | 8K                    |

| PIC18F6490                  | 4                              | 32             | 128                    | 16K                   |

| PIC18F8390                  | 4                              | 48             | 192                    | 8K                    |

| PIC18F8490                  | 4                              | 48             | 192                    | 16K                   |

| © 2004 Microchip Technology | / Incorporated. All Rights Res | erved. 819 NNW | What's New with the PI | C18 Architecture 14   |

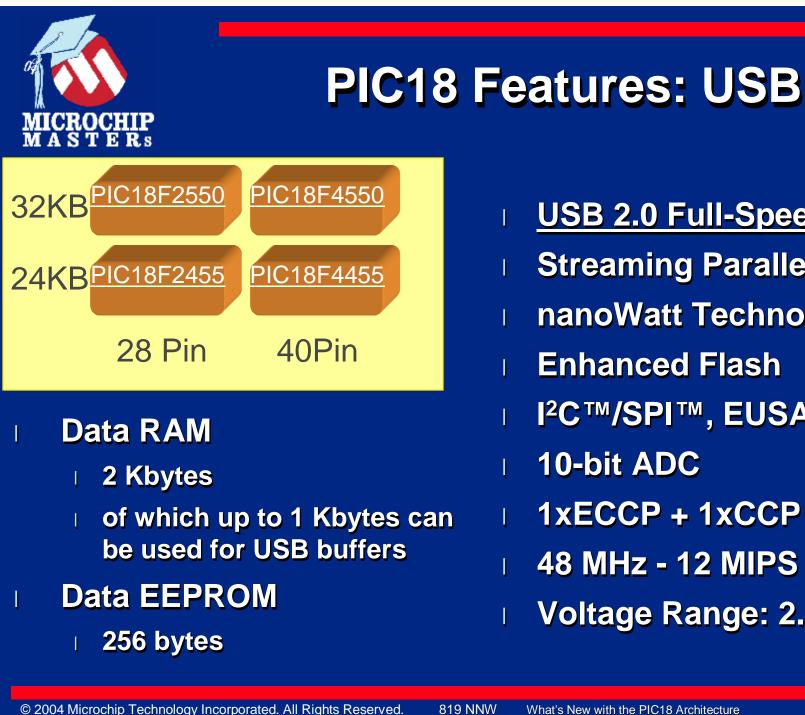

USB 2.0 Full-Speed

- **Streaming Parallel Port**

- nanoWatt Technology

- **Enhanced Flash**

- I<sup>2</sup>C<sup>™</sup>/SPI<sup>™</sup>, EUSART

- **10-bit ADC**

- $1 \times ECCP + 1 \times CCP$

- 48 MHz 12 MIPS

- Voltage Range: 2.0 5.5V

# MICROCHIP MASTERS

#### PIC18 Features Quiz

- 1. Two-Speed Start-up is used for XTAL based modes: True or False True

- 2. The BOR can be enabled by firmware: True or False True

nanoWatt Technology review **PIC18** Features **Clock System Power Managed Modes PIC18** Devices **Extended Instruction Set** Summary

What's New with the PIC18 Architecture

819 NNW

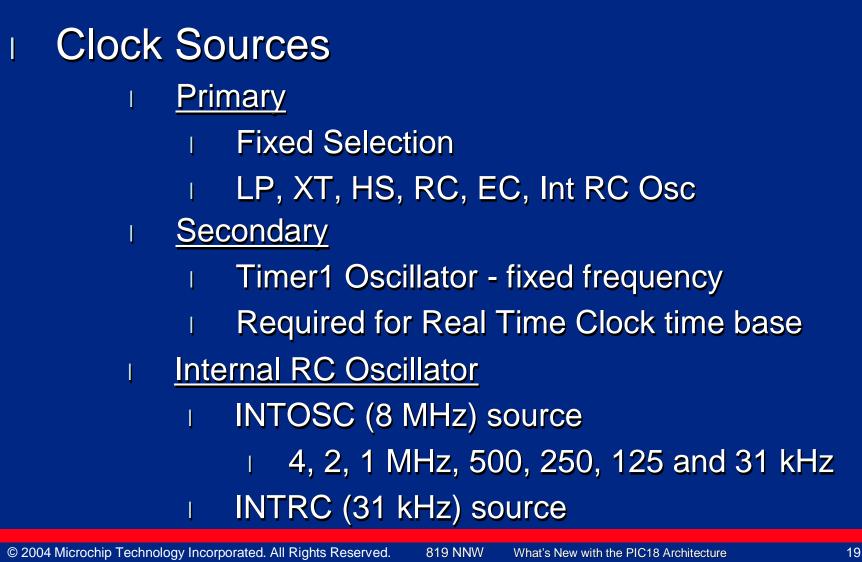

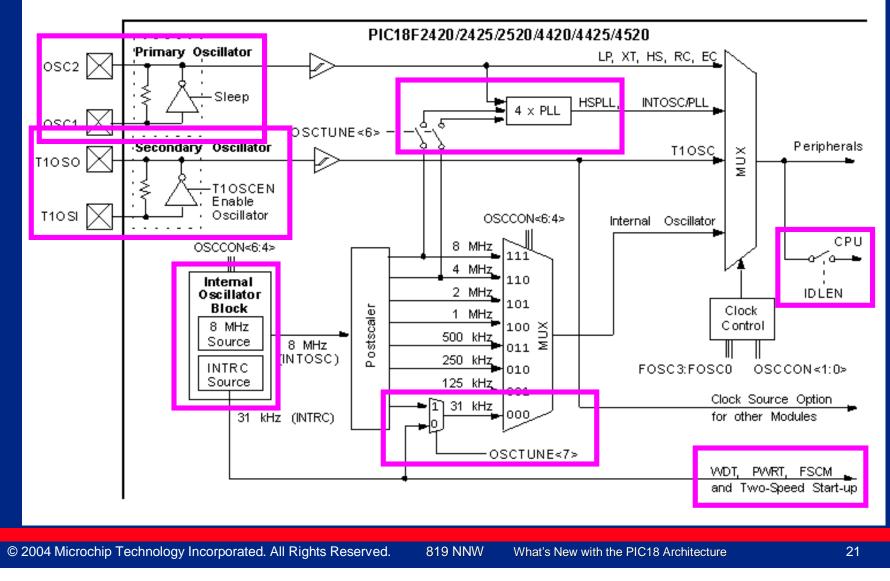

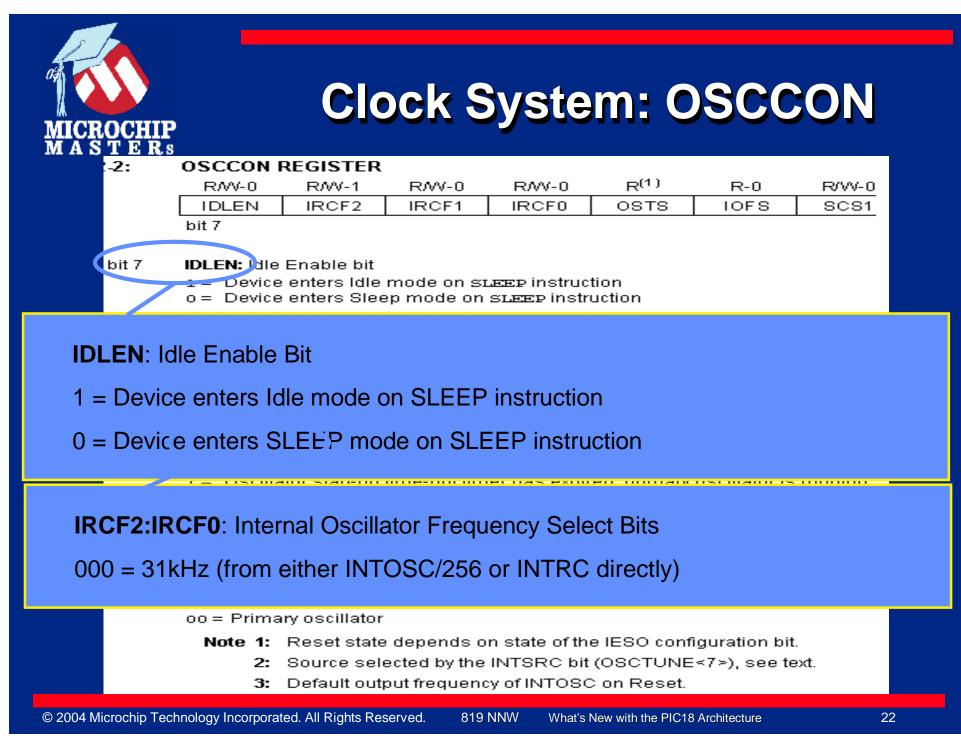

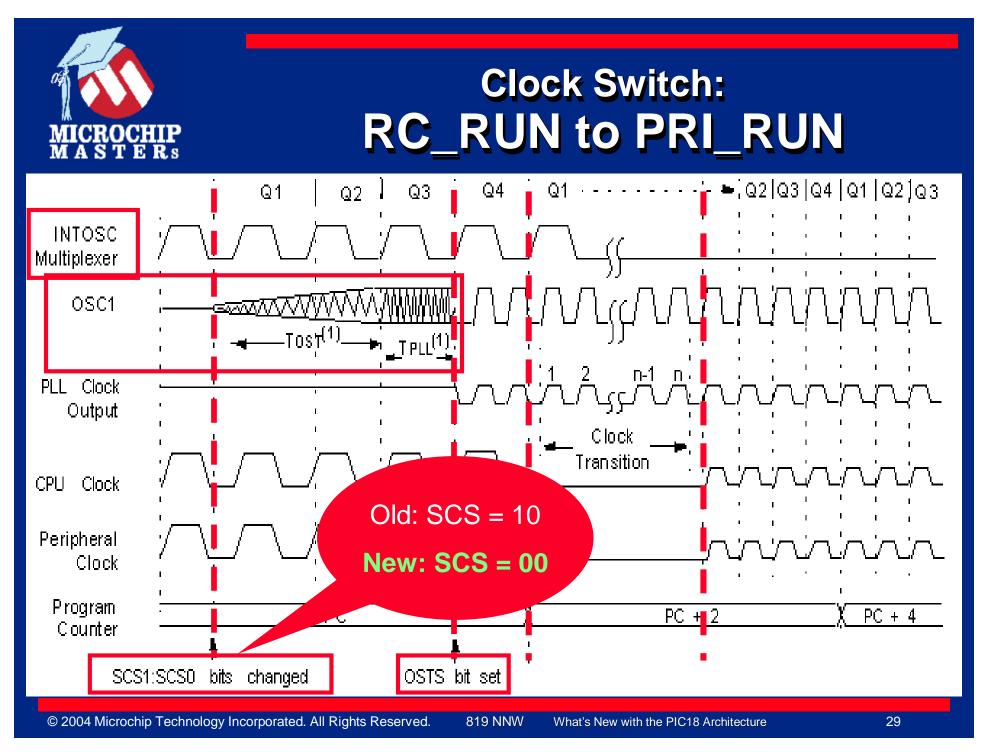

**Clock System**

## **Clock System**

#### New Internal RC Oscillator

- 2 separate RC sources

- 8 MHz (INTOSC)

- 31 kHz (INTRC)

- 2 31 kHz sources

- INTOSC 8 & 4 MHz can be routed through PLL

- 16 or 32 MHz

- Modifying IRCF<2:0> bits immediately selects a different INTOSC postscaler tap

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

#### **Clock System**

nanoWatt Technology review **PIC18** Features **Clock System Power Managed Modes PIC18** Devices **Extended Instruction Set** Summary

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

<u>3 Categories</u>

4 RUN - 3 clock sources

4 IDLE - 3 clock sources

4 SLEEP - no clocks

## Total = 7 Modes

819 NNW

© 2004 Microchip Technology Incorporated. All Rights Reserved.

What's New with the PIC18 Architecture

- PRI\_RUN Mode

- Config Word defines Primary Clock Source

FOSC3:FOSC0 (\_CONFIG1H<3:0>) 10 modes

- Crystal Oscillator LP, XT, HS, HSPLL

- External Clock EC, ECIO

- External RC Oscillator RC, RCIO

- Internal RC Oscillator INTIO1, INTIO2

- SEC\_RUN Mode

- Clock switching mechanism in other PIC18 controllers

- Timer1 source, Primary oscillator is disabled

- RC\_RUN Mode

- IRCF<2:0> selects clock speed

- IOFS set after 1us (typ.) delay if Freq  $\neq$  31 kHz

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW W

What's New with the PIC18 Architecture

| MICROCHIP<br>MASTERS<br>I RUN MO | Power Managed Mo<br>des                                                                                                                              | odes     |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| I Entry                          |                                                                                                                                                      |          |

| de<br>in<br>  Exit:<br>  C       | onfigure the SCS<1:0> bits (OSCCON<br>esired clock source & cxecute a SLEE<br>struction<br>onfigure the SCS<1:0> bits (OSCCON<br>esired clock source | Ê-       |

| Mode                             | Peripheral/CPU Clock                                                                                                                                 | SCS bits |

| PRI_RUN                          | Primary Osc & Running                                                                                                                                | 00       |

| SEC_RUN                          | T1OSC & Running                                                                                                                                      | 01       |

| RC_RUN                           | Int RC Osc Running                                                                                                                                   | 1x       |

| © 2004 Microchip Technology In   | corporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture                                                                      | 27       |

#### PRI\_IDLE Mode

- Same clock source as PRI\_RUN

- Fastest resumption of device operation

- Wake event: CPU is clocked by Primary source

#### SEC\_IDLE Mode

- Same clock as SEC\_RUN

- Wake event: CPU is clocked by Timer1

#### RC\_IDLE Mode

- Same clock as RC\_RUN

- IRCF<2:0> selects clock speed

- Wake event: CPU is clocked by Internal RC oscillator

#### IDLE Modes

- I Entry:

- Enable IDLEN = 1 (OSCCON<7>)

- Execute a SLEEP instruction

- I Exit:

- Interrupt

- WDT time-out

- RESET

| Mode     | <b>Peripheral Clock</b> | <b>CPU Clock</b> | SCS bits |

|----------|-------------------------|------------------|----------|

| PRI_IDLE | Primary Osc             | Halt             | 00       |

| SEC_IDLE | T1OSC                   | Halt             | 01       |

| RC_IDLE  | Int RC Osc              | Halt             | 1x       |

|          |                         |                  |          |

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

What's New with the PIC18 Architecture

31

#### Switch from PRI\_RUN to PRI\_IDLE

bsf OSCCON,IDLEN ; select IDLE mode

sleep ; enters\_PRI\_IDLE mode

"Execution pauses here" "CPU not clocked, peripherals clocked from primary clock source" "Waits for wake event"

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

with the PIC18 Architecture

| <b>Peripheral Functions</b>                         | SLEĘP            | IDĻE         |

|-----------------------------------------------------|------------------|--------------|

| Flash Write                                         |                  |              |

| A/D                                                 | $\checkmark$     | $\checkmark$ |

| USART RX                                            | V,               | $\checkmark$ |

| MSSP RX                                             | V,               | $\checkmark$ |

| Timer 0/1/3 Counter                                 | V,               | $\checkmark$ |

| T1/3 Oscillator                                     |                  |              |

| Capture/Compare                                     | V,               | $\checkmark$ |

| Comparator                                          |                  | V,           |

| WDT,BOR,LVD,MCLR                                    |                  |              |

| PWM/Compare w/output                                |                  | V,           |

| Timer0/1/3 Timer mode                               |                  |              |

| Timer 2                                             |                  | V,           |

| USART Sync TX,async                                 |                  |              |

| MSSP master mode                                    |                  | V,           |

| A/D (sys clock)                                     |                  |              |

| USB                                                 |                  | V,           |

| CAN                                                 |                  | Ň,           |

| LCD                                                 |                  | V            |

| © 2004 Microchip Technology Incorporated. All Right | ts Reserved. 819 | NNW What's N |

#### Why use Idle Mode?

- Save Power

- Peripheral Run/ CPU off

- Fast Wake-up

#### SLEEP Mode

- Legacy SLEEP mode in all Microchip<sup>®</sup> controllers

- CPU/Peripherals clock disabled

- Only power managed mode where no system clock sources are running

- Entry:

- IDLEN bit = 0 (POR default)

- Execute SLEEP instruction

SLEEP Mode (cont'd)

Exit:

No clock is selected, execution resumes when Primary becomes ready

Execution will resume with the clock source selected by the SCS bits

Immediately code execution if 2-Speed Startup or FSCM is enabled

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

#### Exit by Interrupt

CPU/Peripherals are clocked using selected clock until Primary becomes ready

Execution will resume with the clock source selected by the SCS bits

#### Exit by Reset

- Primary clock is started

- Execution pauses until primary becomes ready

- Immediate code execution if 2-Speed Startup or FSCM is enabled

- OSTS bit = 1 when Primary is providing clock

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

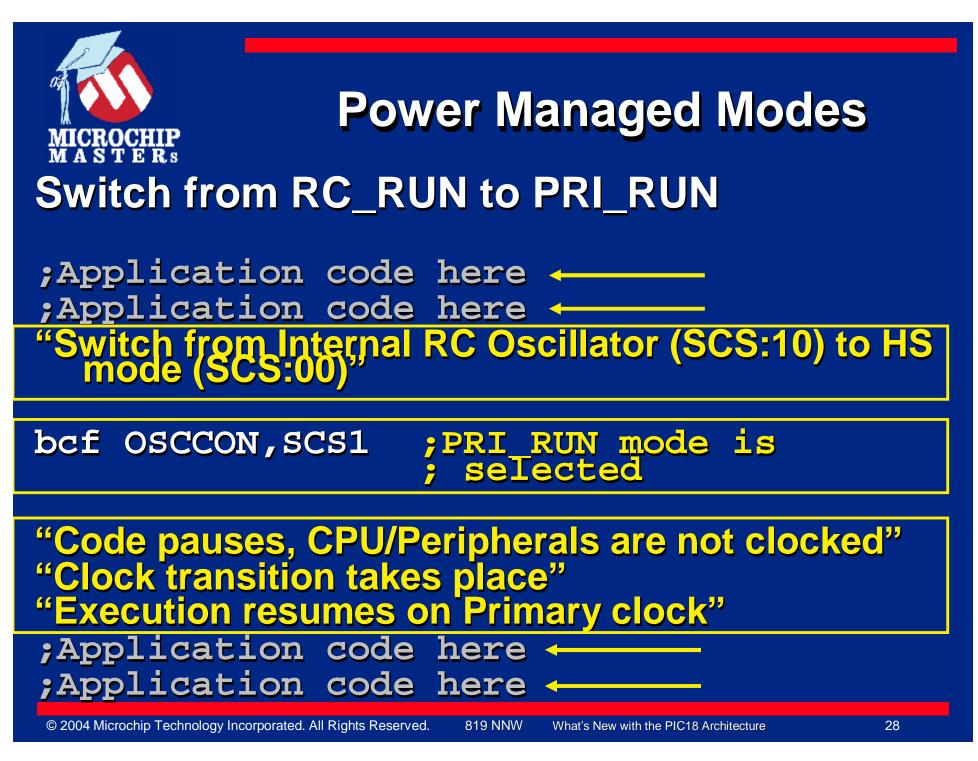

### **Power Managed Modes**

- Exit by WDT Time-out

- I TO bit is cleared (RCON <3>)

- Exit depend on CPU operating condition

- Executing code (all RUN modes)

819 NNW

- Device Reset

- No Code execution (SLEEP & IDLE modes)

Exit from power managed mode

© 2004 Microchip Technology Incorporated. All Rights Reserved.

What's New with the PIC18 Architecture

### Power Managed Modes Quiz

- 1. SEC\_RUN mode uses the Internal RC Osc: True or False False

- 2. A SLEEP instruction must be executed when switching from PRI\_RUN to RC\_RUN: True or False

#### False

3. Which mode keeps the peripherals clocked but disables the CPU clock?

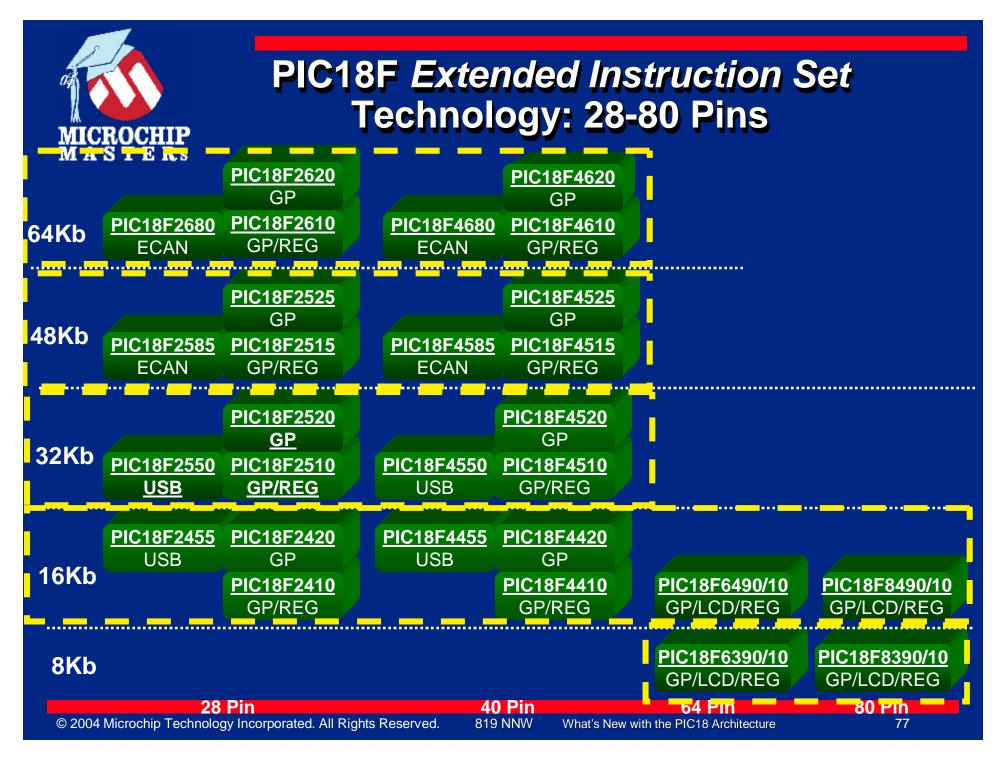

nanoWatt Technology review **PIC18** Features **Clock System Power Managed Modes PIC18 Devices PIC18F Extended Architecture** Summary

# CROCHIP

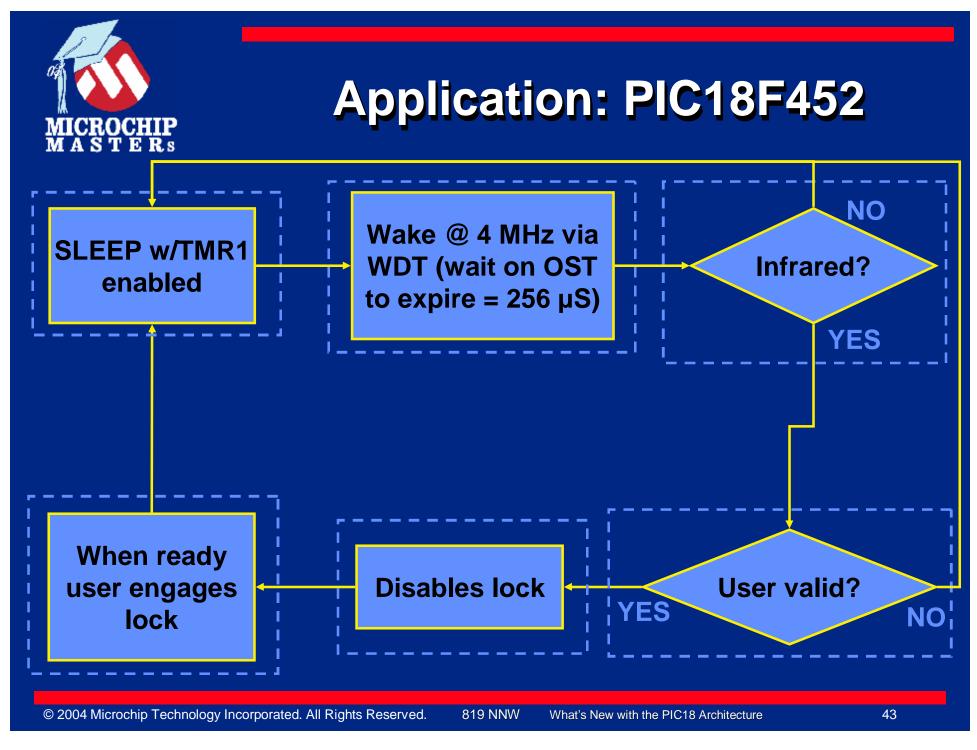

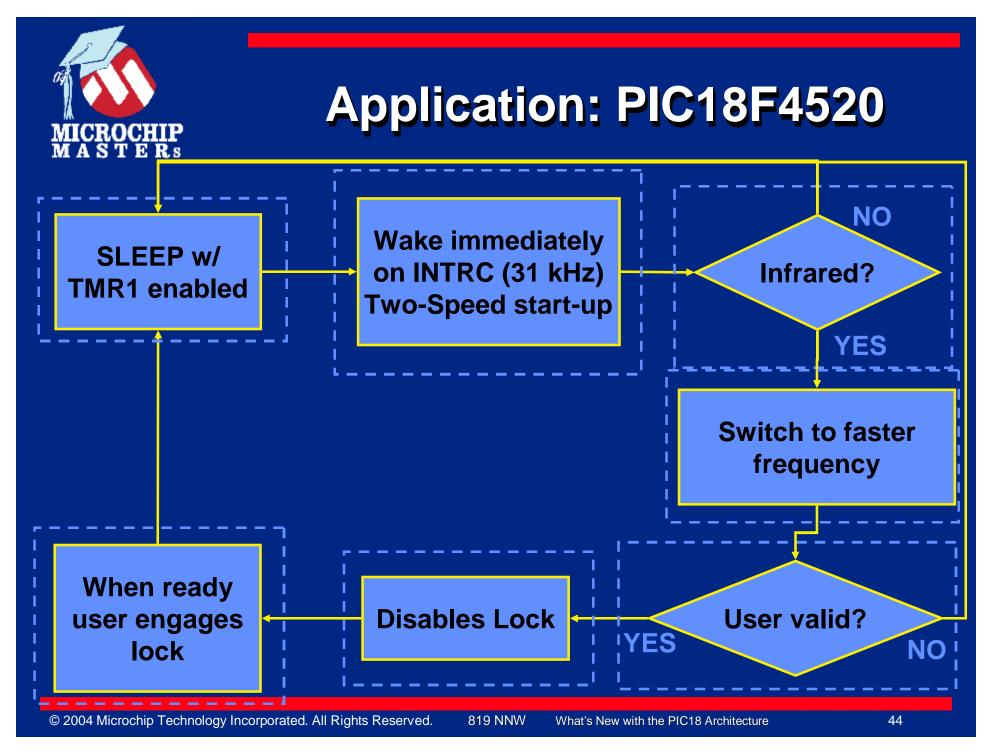

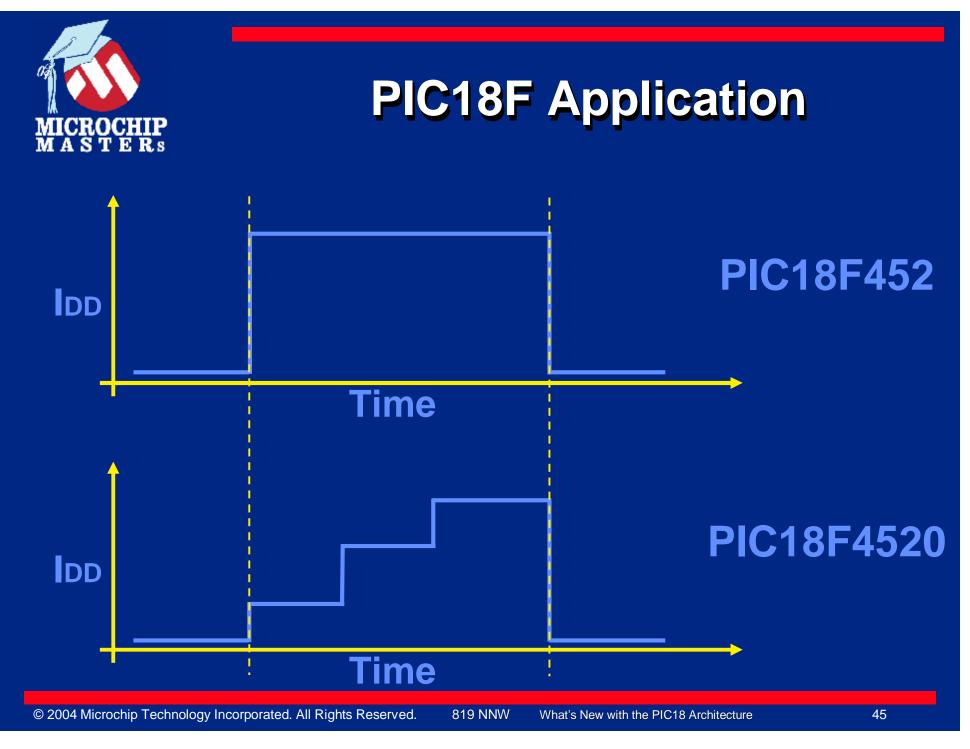

### **PIC18F** Application

"Lock Box"

- Purpose: Key Storage

- **Residential/Commercial**

- Operation

- Waits on user input

- Decodes user id, logs name & time

- **Opens locking mechanism**

- Short duty cycle

- **Battery powered**

- Multiple users

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

### **PIC18F** Application

Lock Box Firmware

- Operating modes

- SLEEP and wake on a regular period

- Check valid Infrared signal, not valid go back to SLEEP

- If valid, increase frequency & receive

- Valid user: lock disengages

nanoWatt Technology review **PIC18** Features **Clock System Power Managed Modes PIC18** Devices **PIC18F Extended Architecture** Summary

#### PIC18F Architecture Extensions Agenda

- Background/Motivation

- What is the extended architecture?

- + New addressing mode

- + New instructions

- How to enable the extensions

- Silicon support

- Tools support

- Impact of the extensions

- Who should/shouldn't use the extensions?

# MICROCHIP M A S T E R S

### Background

The existing PIC18 architecture provides a number of features that support high-level languages:

- byte-wide program memory addressing

- indirection registers

- pre/post increment/decrement

- single-cycle multiply

- PLUSW2 addressing

Some areas where we still saw room for improvement:

- stack access (multiple use of WREG)

- function pointers

- cross-bank stack manipulations

#### To provide a memory-efficient model for high-level language support, including reentrant code

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

# MICROCHIP M A S T E R S

### **The Solution**

#### PIC18F Architectural Enhancements:

- A new addressing mode (literal indexed)

- Several new instructions

These extensions greatly simplify the code that is needed for high-level language constructs

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

What's New with the PIC18 Architecture

51

### Why Do I Care?

Understanding compiler-generated code

Interfacing to C code in assembly language

Application in standalone assembly code

#### PIC18F Architecture Extensions Agenda

- Background / Motivation

- What is the extended architecture?

- + New addressing mode

- + New instructions

- How to enable the extensions

- Silicon support

- Tools support

- Impact of the extensions

- Who should / shouldn't use the extensions?

### **Presentation of Extensions**

For each extension, we will provide the following information:

- Example of code on existing architecture

- Description of new instructions/addressing

- Comparison showing improvement

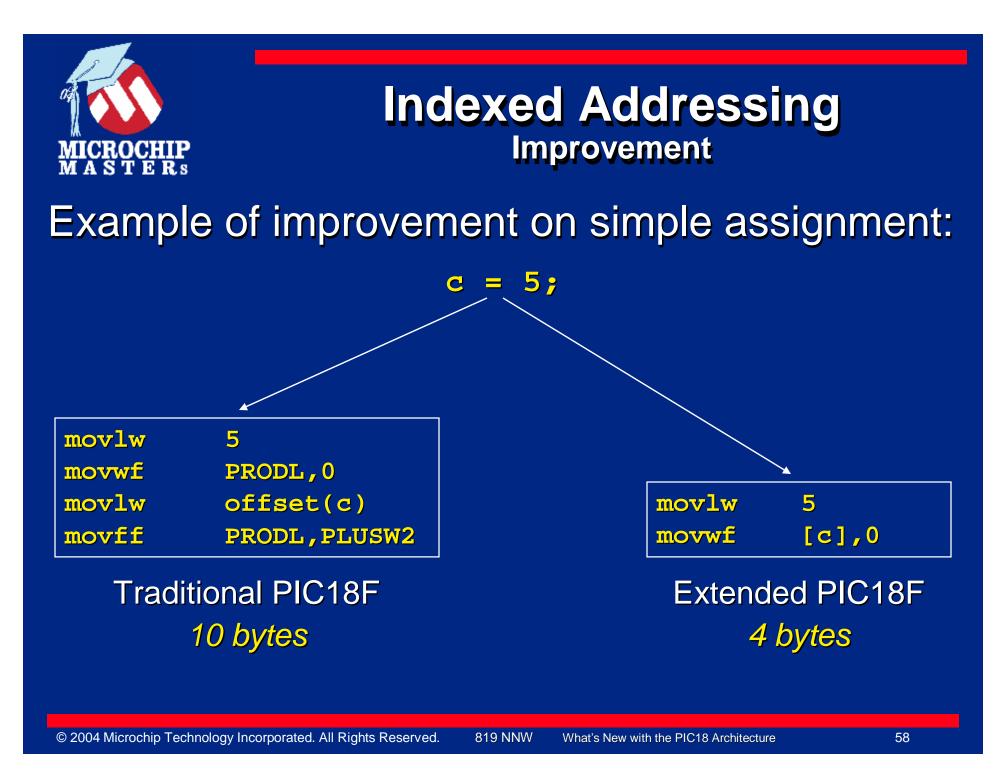

#### Indexed Addressing Existing PIC18

Performing a simple assignment to a stackbased variable: c = 5;

generates 10 bytes of instructions: movlw 5

movwf PRODL,0

movlw offset(c)

movff PRODL,PLUSW2

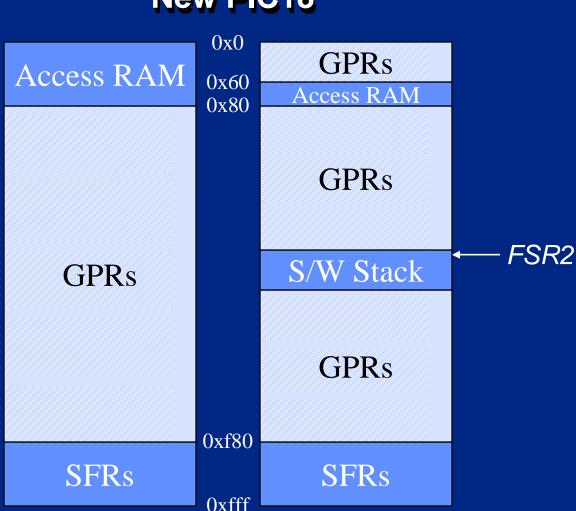

#### Indexed Addressing New PIC18

Indexed literal addressing remaps the access RAM window to be a stack offset window

= banked addressing

= unbanked addressing

#### Traditional PIC18F Extended PIC18F

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

What's New with the PIC18 Architecture

#### Indexed Addressing New PIC18

57

Assembler syntax:

opcode [offset],f

Example:

addwf [12],1 ; add WREG to location (FSR2+12)

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

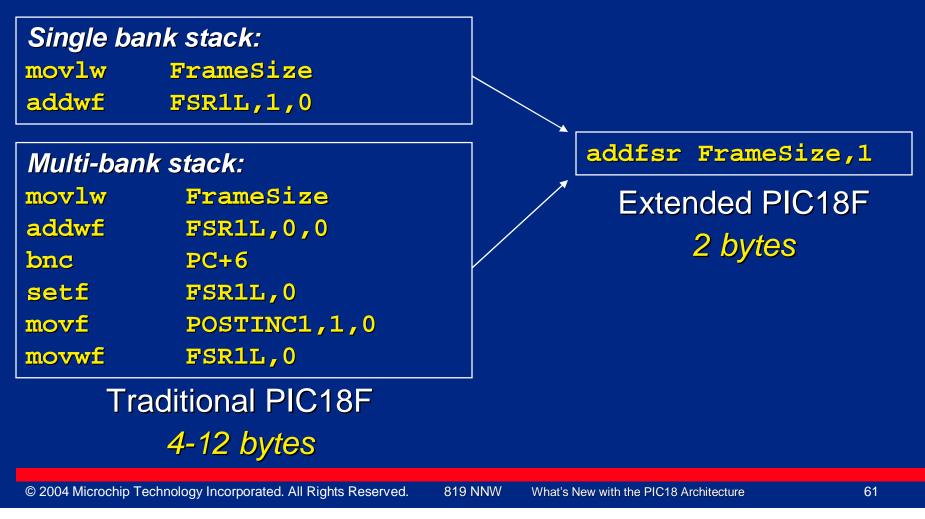

#### **Stack Allocation** Existing 18F Architecture

# Stack allocation overhead (4 bytes) is required on most functions:

| movlw  | FrameSize        |  |

|--------|------------------|--|

| addurf | <b>HOD17 1</b> ( |  |

# The penalty is even worse (12 bytes) if the stack is allowed to cross banks:

| movlw | FrameSize    |

|-------|--------------|

| addwf | FSR1L,0,0    |

| bnc   | PC+6         |

| setf  | FSR1L,0      |

| movf  | POSTINC1,1,0 |

| movwf | FSR1L,0      |

|       |              |

# MICROCHIP M A S T E R S

#### Stack Allocation New PIC18

| Assembler synta                             | IX:                         |                  |                 |            |      |

|---------------------------------------------|-----------------------------|------------------|-----------------|------------|------|

| addfsr                                      | literal,                    | n                |                 |            |      |

| subfsr                                      | literal,                    | n                |                 |            |      |

| Operation:<br>FSR <b>n</b> = FSR            | n+/-liter                   | al               |                 |            |      |

| Example:                                    |                             |                  |                 |            |      |

| addfsr                                      | 20,2                        | ; add            | 20              | to         | FSR2 |

| © 2004 Microchip Technology Incorporated. A | II Rights Reserved. 819 NNV | V What's New wit | h the PIC18 Arc | chitecture | 60   |

#### Stack Allocation Improvement

Example of improvement for function prologue:

#### Stack Allocation w/ return

Assembler syntax: literal addulnk subulnk literal **Operation:** FSR2 = FSR2 +/- literal return **Example:** subulnk 14 subtract 14 from FSR2 2 and return 2 © 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture 62

#### Move Stack to Global Existing PIC18

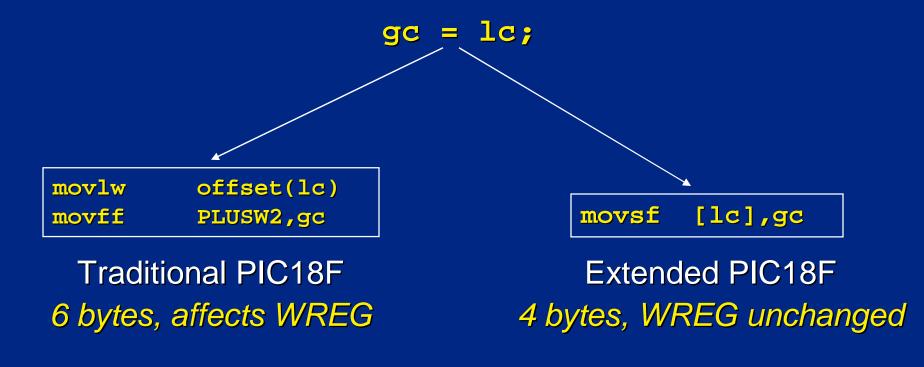

Moving a local variable's contents into a global variable: gc = lc;

Produces the following code:

movlwoffset(lc)movffPLUSW2, gc

#### Move Stack to Global New PIC18

Assembler syntax: movsf [src], dst **Operation:** dst = (FSR2 + src)**Example:** movsf [5], 0xac ; move the contents of (FSR2 + 5) into memory ; location 0xac © 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture 64

#### Move Stack to Global Improvement

#### Example of improvement:

# MICROCHIP MASTERS

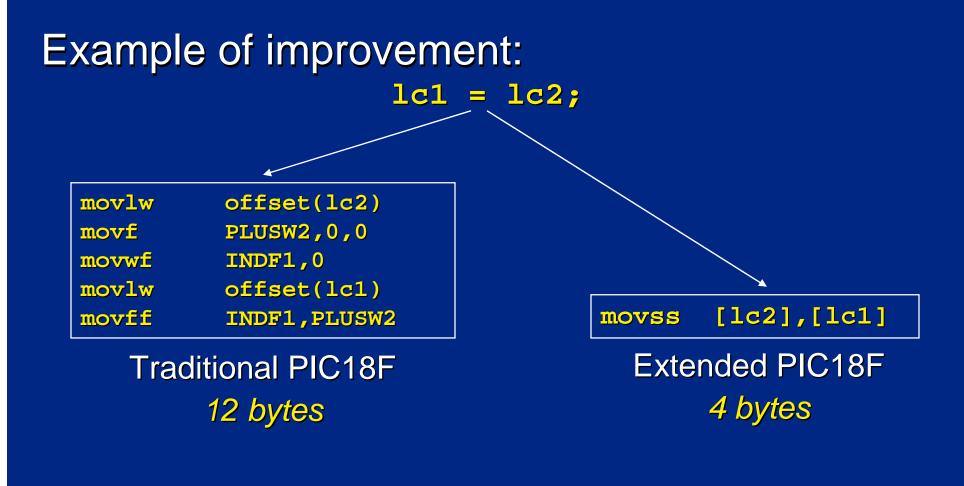

#### Move Stack to Stack Existing PIC18

Moving a local to another local variable: lc1 = lc2;

Produces the following code:

| movlw | offset(lc2)    |

|-------|----------------|

| movf  | PLUSW2,0,0     |

| movwf | INDF1,0        |

| movlw | offset(lc1)    |

| movff | TNDE1 . PLUSW2 |

#### Move Stack to Stack New PIC18

67

Assembler syntax: [src], [dst] MOVSS **Operation:** (FSR2 + dst) = (FSR2 + src)**Example:** movss [3], [5] ; move the contents of (FSR2 + 5) into (FSR2 + 3)© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

# MICROCHIP MASTERS

#### Move Stack to Stack Improvement

#### Function Pointer Invocation Existing PIC18

Invoking a function pointer: fn();

#### Produces the following code:

| bra   | PC+12         |

|-------|---------------|

| movff | fn+2,PCLATU   |

| movff | fn+1,PCLATH   |

| movlb | fn            |

| movf  | <b>fn,0,1</b> |

| movwf | PCL,0         |

| rcall | PC-10         |

|       |               |

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

What's New with the PIC18 Architecture

#### Function Pointer Invocation New PIC18

#### Assembler syntax: callw

### Operation: PC = PCLATU:PCLATH:WREG

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

# Function Pointer Invocation

# Example of improvement:

| bra   | PC+12       |

|-------|-------------|

| movff | fn+2,PCLATU |

| movff | fn+1,PCLATH |

| movlb | fn          |

| movf  | fn,0,1      |

| movwf | PCL,0       |

| rcall | PC-10       |

Traditional PIC18F 18 bytes, 2 branches movff fn+2,PCLATU

movff fn+1,PCLATH

movlb fn

movf fn,0,1

callw

Extended PIC18F 14 bytes, 0 branches

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

What's New with the PIC18 Architecture

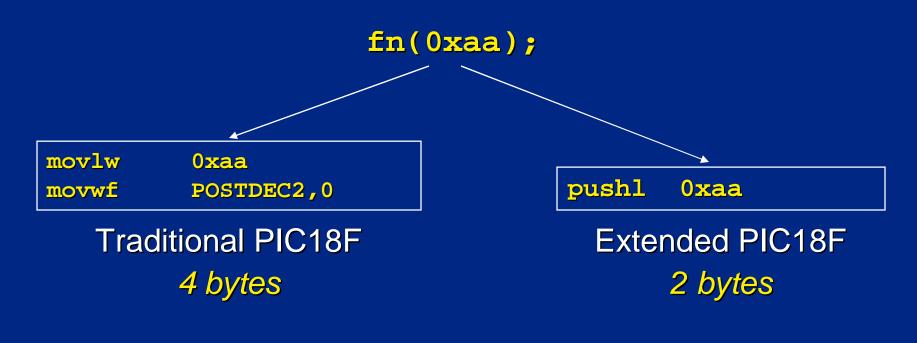

#### Passing a Literal Parameter Existing PIC18

Pushing a literal value onto a downward-growing stack: fn(0xaa);

Produces the following code:movlw0xaamovwfPOSTDEC2,0

#### Passing a Literal Parameter New PIC18

# Assembler syntax:

Operation: POSTDEC2 = 11t

Example:

pushl 23 ; Store 23 to (FSR2) and ; decrement FSR2

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

What's New with the PIC18 Architecture

#### Passing a Literal Parameter Improvement

#### Example of improvement:

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

#### PIC18F Architecture Extensions Agenda

- Background / Motivation

- What is the extended architecture?

- + New addressing mode

- + New instructions

- How to enable the extensions

- Silicon support

- Tools support

- Impact of the extensions

- Who should / shouldn't use the extensions?

### **Enabling the extensions**

#### A single configuration bit selects between:

#### Traditional Mode

New instruction opcodes are interpreted as NOPs

Fast memory references in the range [0,0x5f] address general purpose access RAM

**Default for Development Tools**

#### Extended Mode

New instructions are available

Fast memory references in the range [0,0x5f] address FSR2 offsets

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

# **Tools Support**

Software tools are available NOW:

- I MPASM<sup>™</sup> Assembler

- I MPLAB® IDE / SIM

- MPLAB C18

Hardware tools are available NOW:

- In-Circuit Debugger (ICD2)

- Programmer (PRO MATE<sup>®</sup> 2)

819 NNW

Emulator (ICE 2000/4000)

© 2004 Microchip Technology Incorporated. All Rights Reserved.

What's New with the PIC18 Architecture

# MICROCHIE MASTERS

### What Mode to Use

Use Extended Mode When...

- Re-entrancy is required

- Starting a new design

- Code is mostly written in C

- Portability to non-extended cores is not needed

- RAM space is critical

Use Traditional Mode When...

- The static model is O.K.

- Modifying an existing design

- Code is mostly written in ASM

- Code must also work on nonextended cores

- RAM space is not critical

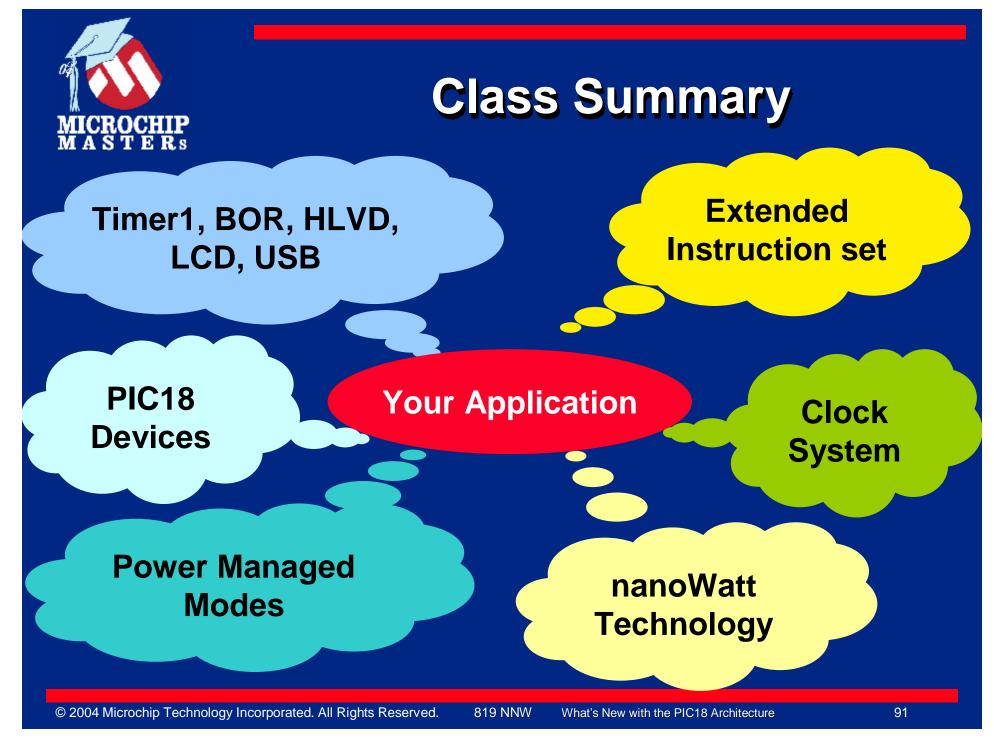

## Summary

- The PIC18F architecture has been extended with:

- + a new addressing mode (indexed literal)

- + new instructions

- These extensions provide efficient high-level language support

- 100% backward-compatible behavior is available

- Tools are available now

- Applicability of the extensions will depend on the project

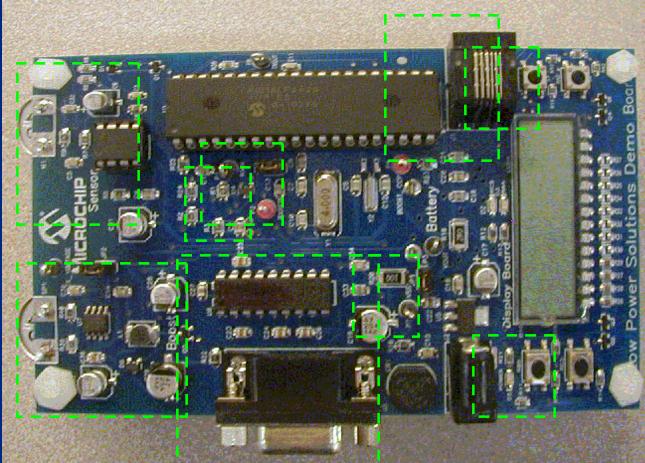

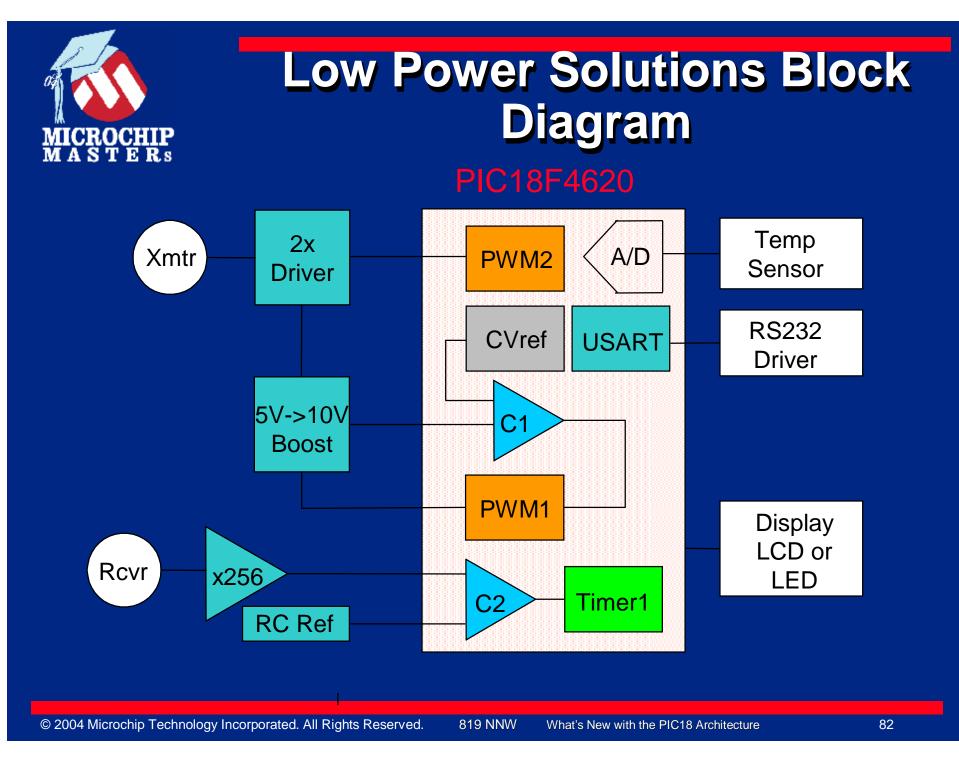

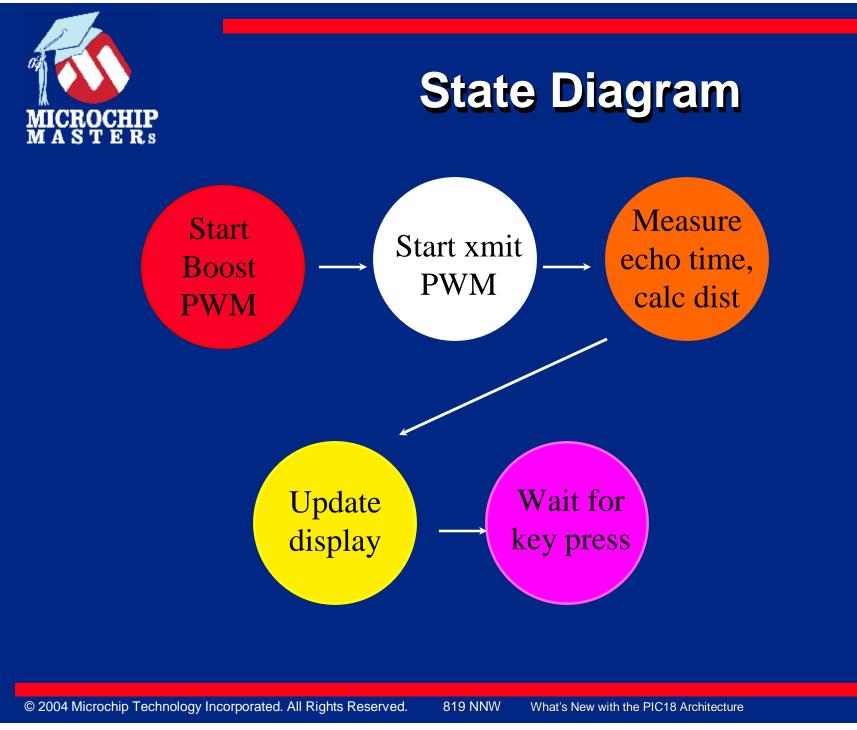

### **Ultrasonic Range Finder**

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

81

# Lab: Putting It All Together

- Purpose: To analyze an application and reduce its power consumption.

- Determine where power managed modes can be used

- Adjust clock frequency to minimize power consumption

- Maintain performance

- Measure system and PICmicro current consumption by connecting current meter to appropriate jumper.

Disable unnecessary system components

LEDRA4\_OFF; //nW: Turn off LED DISABLE\_TEMP;//nW: Turn off temp sensor DISABLE\_USART; //nW: Turn off USART driver

Select INTOSC as Primary Oscillator in Config Word

TRIS unused I/Os as outputs for INTOSC

Use INTOSC as primary oscillator and select 4MHz frequency.

int Fosc = 4;

//Frequency in MHz

TRISAbits.TRISA6 = 0; TRISAbits.TRISA7 = 0; OSCCON = 0b01100000; while(!OSCCONbits.IOFS);

//4MHz INTOSC

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW

What's New with the PIC18 Architecture

#### Disable boost after transmit

DisableBoost();

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

Replace button while-loop with Sleep and PortB interrupton-change wake-up

#### // while(SW1\_NOT\_PRESSED);

TRISBbits.TRISB7 = 0; TRISBbits.TRISB6 = 0; Disable\_Ints(); WREG = PORTB; INTCONbits.RBIF = 0; INTCONbits.RBIE = 1; Sleep(); INTCONbits.RBIE = 0;

Replace 100ms for-loop delay with TMR2 rollover at Fosc=512Khz.

- 100ms settling time is required between samples.

- Fosc >= 512KHz required to minimize LCD T3 interrupt latency.

### // for(SampleDelay=0;SampleDelay<190\*Fosc; SampleDelay++);

© 2004 Microchip Technology Incorporated. All Rights Reserved. 819 NNW What's New with the PIC18 Architecture

#### Lab: Tip 5 Continued

$\Theta S C O N$  sh = OSCCON; OSCCON = 0b00110000;while(!OSCCONbits.IOFS); TMR2 = 0;PR2 = 0xFF;T2CON = 0b00100101;PIR1bits.TMR2IF = 0; PIE1bits.TMR2IE = 1;while(T2CONbits.TMR2ON) Sleep(); PIE1bits.TMR2IE = 0;OSCCON = OSCCON\_sh; while(!OSCCONbits.IOFS);

//Store previous value

//512KHz INTRC, Sleep

//~100ms rollover time

//1:5 post, 1:4 pre, on

//Restore value

//Wait for switch

What's New with the PIC18 Architecture

# MICROCHIP M A S T E R S

#### <u>Demo Boards</u>

- I PICDEM™ 4

- PICDEM MC

- I PICDEM Full Speed USB

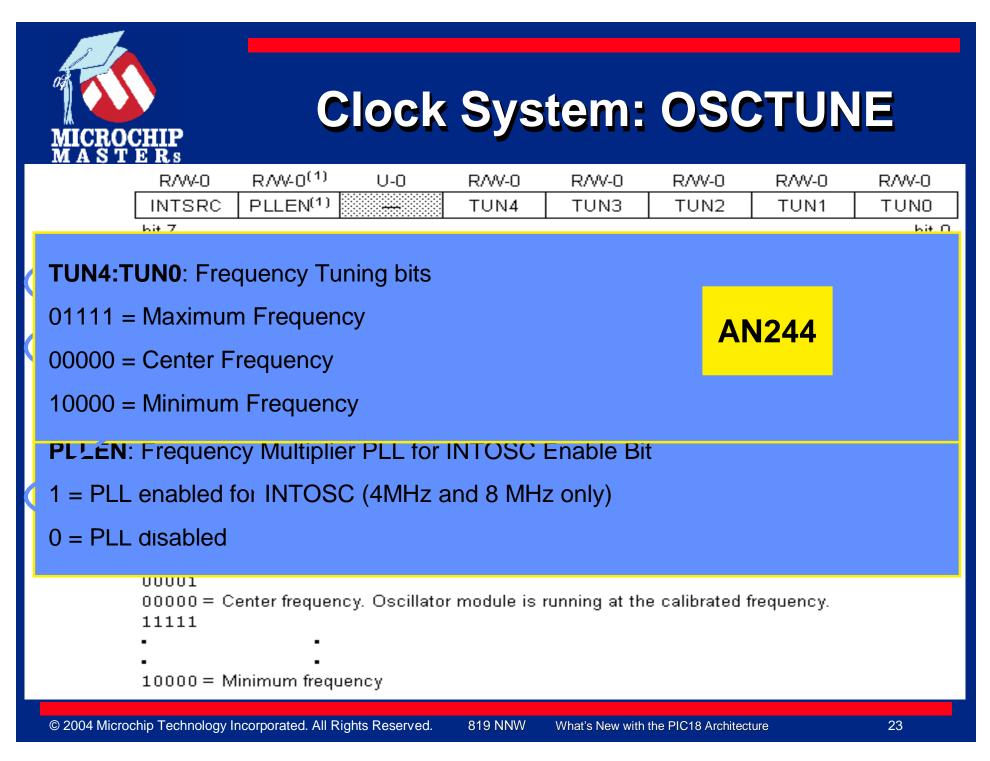

#### Application Notes

- Internal RC Oscillator Calibration AN244

- **USB Power Management ANTBD**

- RS-232 to USB Migration ANTBD

- USB Mass Storage Class ANTBD

- J1939 C Library AN930

- Brushless DC Motor Control AN899