# 11089 PS4

# SMPS Basics Using the dsPIC® SMPS Digital Signal Controllers (DSCs)

## Class Objective

#### When you finish this class you will:

- Understand the Intelligent Power Peripherals on SMPS devices

- Learn how digital PID control loops are implemented

- Understand the functional blocks of SMPS firmware

- Understand Power-up Sequencing

# **Agenda**

- General Overview of the SMPS dsPIC30F **Processors**

- IPP PWM: Architecture and Programming

- Data Monitor and Control Interface

- I ab 1

- IPP ADC: Architecture and Programming

- Faults and Current Limiting Features

- Lab 2

- Buck Demo Board: PID control loop and firmware

- Lab 3

- Sequencing

# **General Overview**

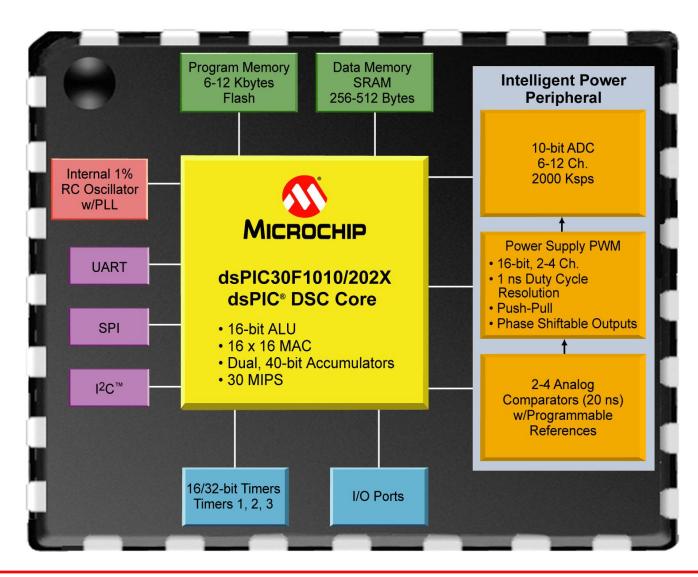

## The SMPS dsPIC® DSC Family

## The SMPS dsPIC® DSC Family

- 30 MIPs MCU + DSP core

- High Speed A/D: 10-bit, 2 MSPS

- High Resolution PWM 1.05 nsec resolution

- High Speed Analog Comparators

- Internal FRC + PLL

- Extended Temp (125°C) Operation

- Flash based controller

- Small footprint package 6 x 6 mm

# IPP PWM **Architecture** and **Programming**

- High resolution PWM: 12 bits at 234 kHz

- 1.05 ns duty cycle resolution

- Individual deadtime values for each PWM

- Positive and negative deadtime

- 4.4 nsec resolution

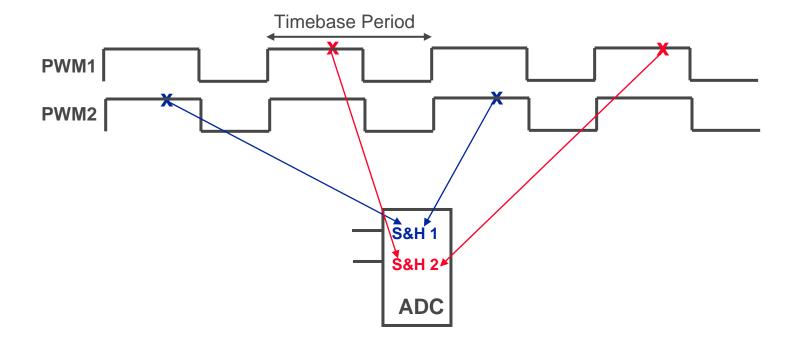

- Extensive ADC triggering options

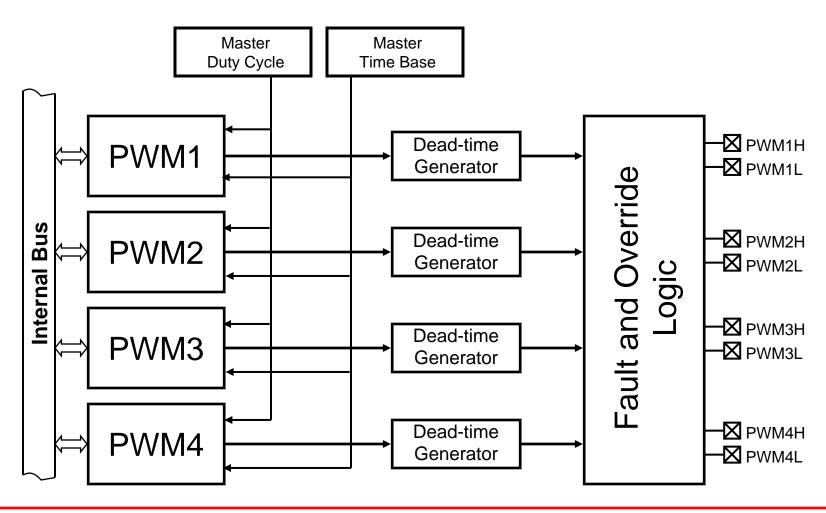

- Four PWM generators with eight I/O and Four independent time bases

- Duty cycle resolution of 1.05 nsec @ 30 MIPS

- Dead-time resolution of 4.2 nsec @ 30 MIPS

- Frequency resolution of 8.4 nsec @ 30 MIPS

#### Supported PWM modes:

- Standard Edge-Aligned PWM

- Complementary PWM

- Push-Pull PWM

- Multi-Phase PWM

- Variable Phase PWM

- Fixed Off-Time PWM

- Current Reset PWM

- Current-Limit PWM

- Independent Time Base PWM

- On-the-Fly changes to:

- PWM frequency

- PWM duty cycle

- PWM phase shift

- Output override control

- Independent current-limit and fault inputs

- Special event triggers

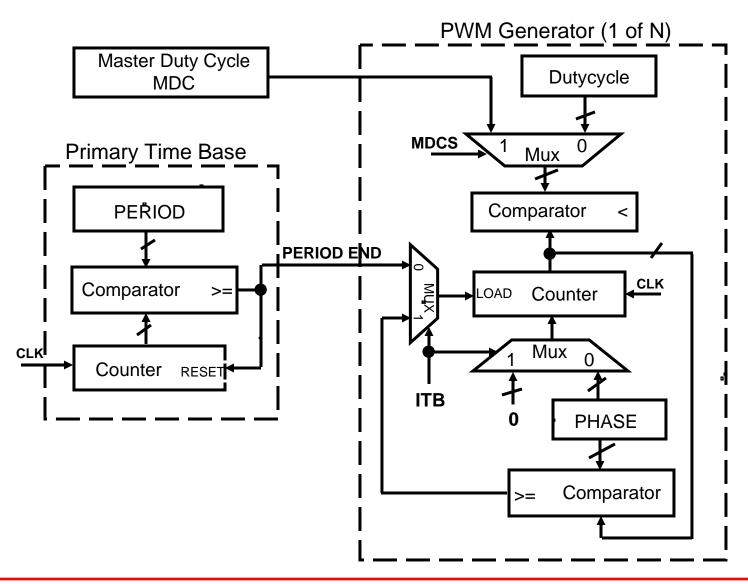

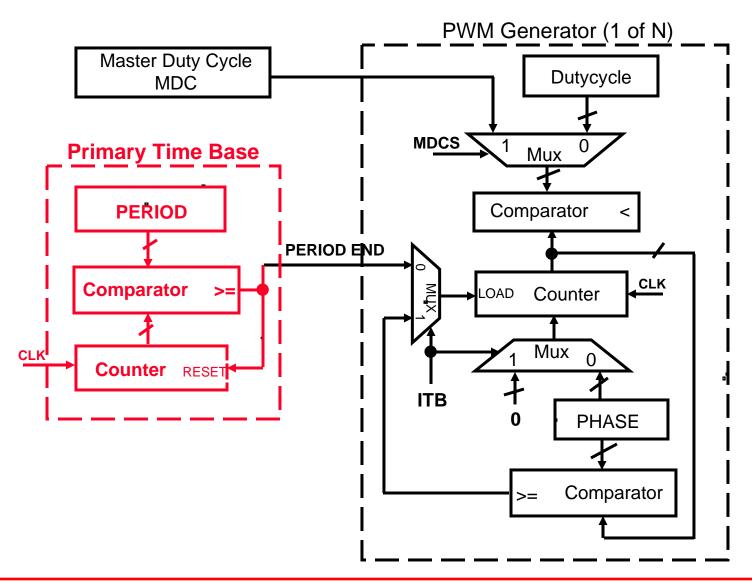

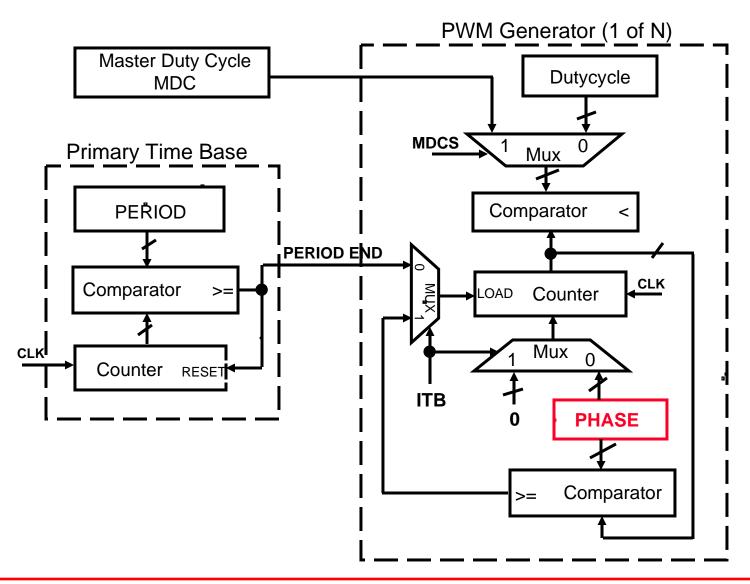

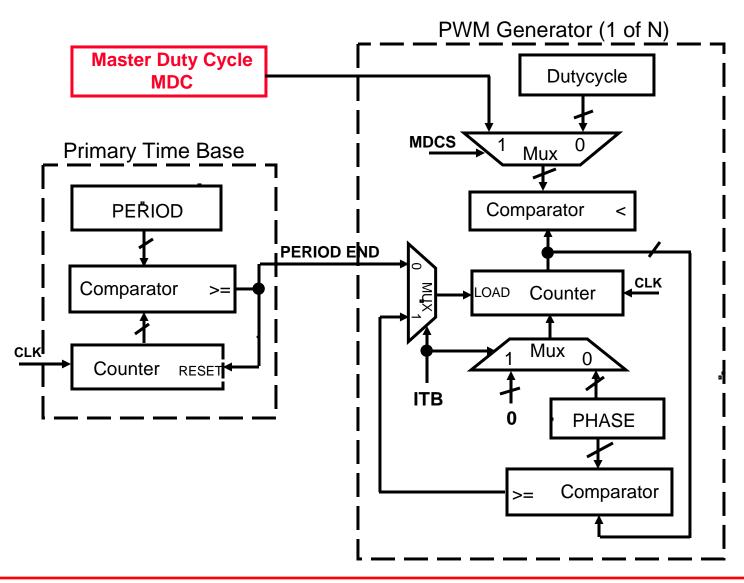

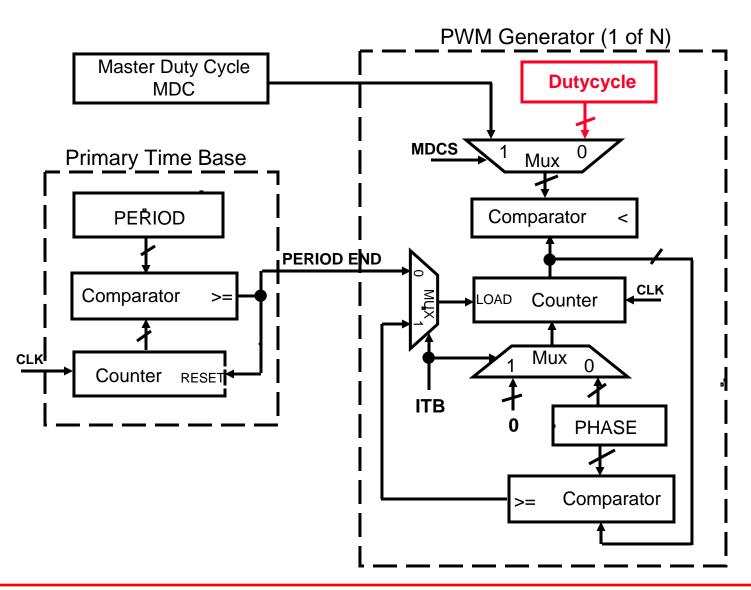

#### Basic PWM Architecture

- PWM Frequency Generation

- Primary Time Base (PTMR) counter

- Individual Time Base Counter (PHASEx)

- PWM Duty Cycle Generation

- Master Duty Cycle (MDC) Register

- Individual Duty Cycle Register

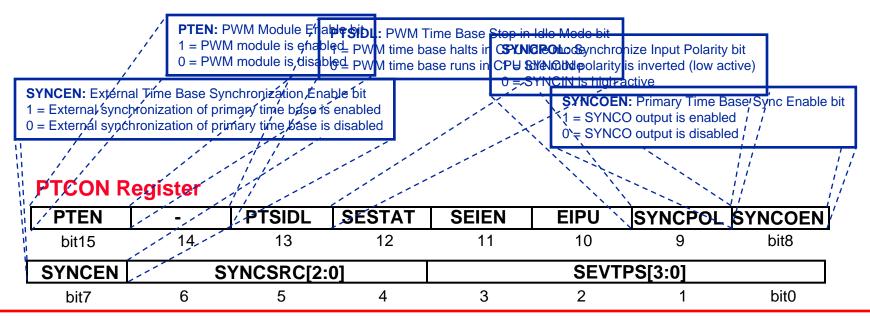

#### The PTCON Register: controls the general operation of the peripheral

- Enables the module

- Controls IDLE behavior

- Controls external synchronization features

#### The PTPER register defines the primary time base period for the PWM generators

- The least significant 3 bits are not implemented

- Bit 3 (LS implemented bit) represents 8.4ns @ 30 MIPS

#### PTPER Register

|       | 911111 |            |       |         |    |   |      |

|-------|--------|------------|-------|---------|----|---|------|

|       |        |            | PERIO | D[15:8] |    |   |      |

| bit15 | 14     | 13         | 12    | 11      | 10 | 9 | bit8 |

|       | Р      | ERIOD[7:3] |       |         |    | _ |      |

| bit7  | 6      | 5          | 4     | 3       | 2  | 1 | bit0 |

# The Master Duty Cycle register defines the Duty Cycle common to all modules

May be used by any PWM as a source for the duty cycle

#### **Duty Cycle Computation**

To get a 50% Duty Cycle: MDC = PTPER >> 1

#### **MDC** Register

|       |          |    | MDC[ | 15:8] |    |   |      |

|-------|----------|----|------|-------|----|---|------|

| bit15 | 14       | 13 | 12   | 11    | 10 | 9 | bit8 |

|       | MDC[7:0] |    |      |       |    |   |      |

| bit7  | 6        | 5  | 4    | 3     | 2  | 1 | bit0 |

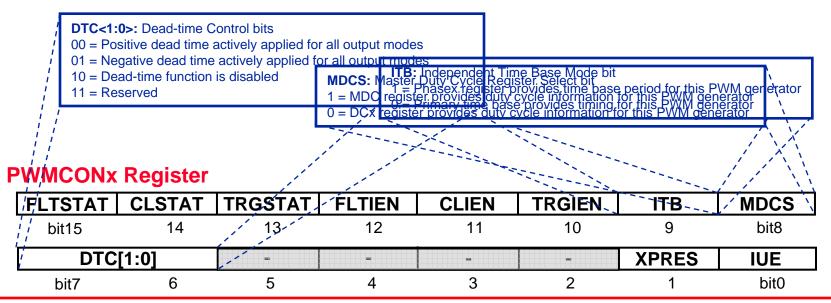

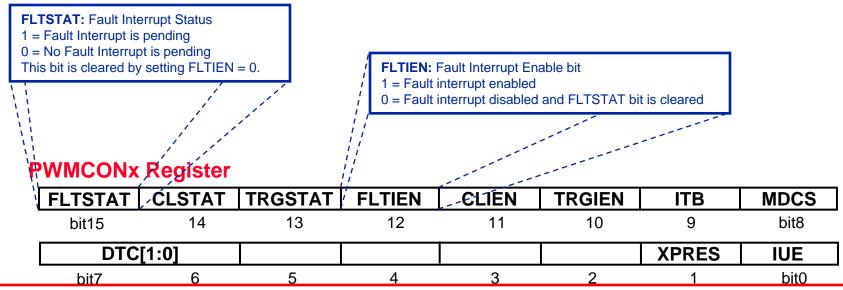

#### The PWMCONx register controls the general operation of each PWM module

- Enables independent time base mode

- Selects the source of the duty cycle

- Defines the operation of the deadtime logic

# The PDCx register sets the Duty Cycle for each PWM module

- The dutycycle resolution is 1.05 nsec @30 MIPS

- The dutycycle value may be updated at anytime during the PWM cycle, if the IUE bit is set in the PWMCONx register

#### **PDCx Register**

|       | <del>5</del> |    |      |       |    |   |      |

|-------|--------------|----|------|-------|----|---|------|

|       |              |    | PDC[ | 15:8] |    |   |      |

| bit15 | 14           | 13 | 12   | 11    | 10 | 9 | bit8 |

|       |              |    | PDC  | [7:0] |    |   |      |

| bit7  | 6            | 5  | 4    | 3     | 2  | 1 | bit0 |

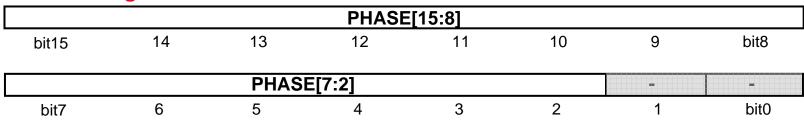

#### The PHASEx register:

- Each PWM generator has its own PHASE register

- It can be used either as a phase-shift value or as the independent Time Base Period

- The phase resolution is 4 nsec @30 MIPS

- The value moves the PWM signal "earlier" in time

- The phase value may be updated at anytime during the PWM cycle; the new phase value takes effect at the end of the PWM cycle

#### **PHASEx Register**

#### The DTRx/ALTDTRx registers:

- Each PWM generator has its own Dead Time Registers for rising and falling PWM edges

- The dead time resolution is 4.2 nsec @30 MIPS

| MIPS | Resolution | Dead-time Range   |

|------|------------|-------------------|

| 30   | 4.16 ns    | <b>0-17.03</b> μs |

| 20   | 6.25 ns    | <b>0-25.59</b> μs |

#### **DTRx / ALTDTRx Register**

| 100   | _  |                  | DTR | / ALTDTR[ | 13:8] |   |      |

|-------|----|------------------|-----|-----------|-------|---|------|

| bit15 | 14 | 13               | 12  | 11        | 10    | 9 | bit8 |

|       |    | DTR/ ALTDTR[7:2] |     |           |       | - | -    |

| bit7  | 6  | 5                | 4   | 3         | 2     | 1 | bit0 |

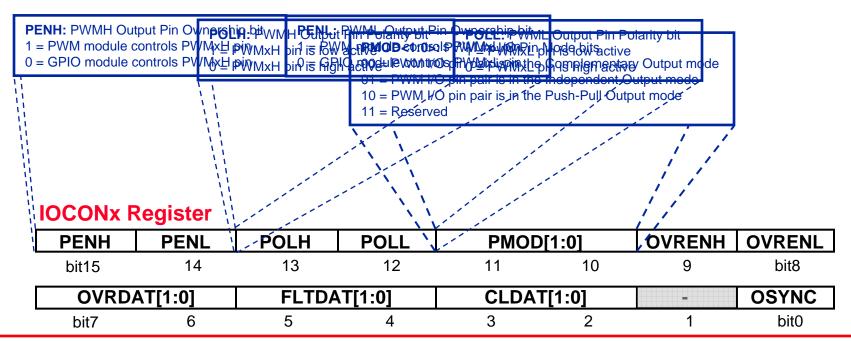

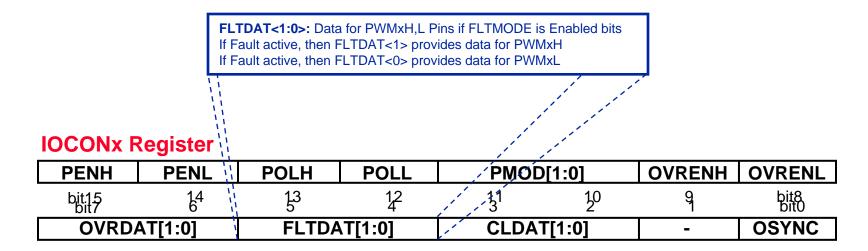

#### The IOCONx register is the I/O Control register

- Controls the ownership of the PWM pins

- Controls the polarity of the PWM pins

- Controls the pwm output mode

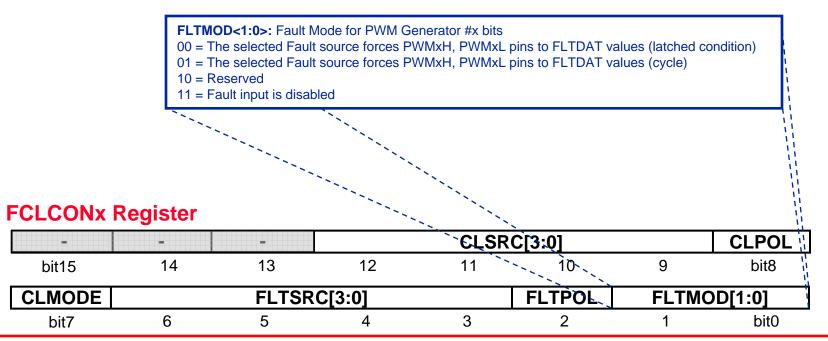

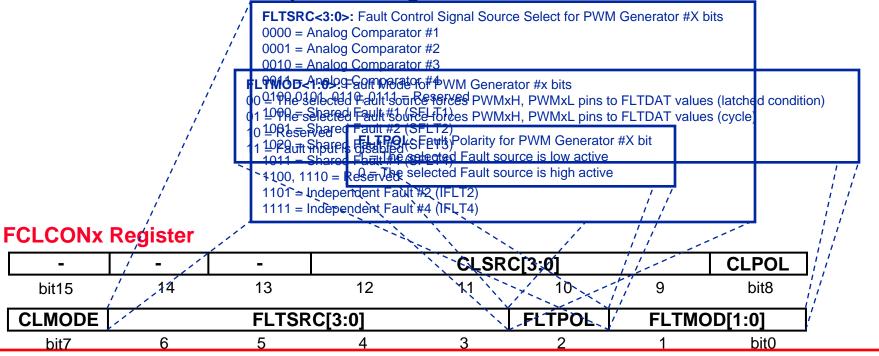

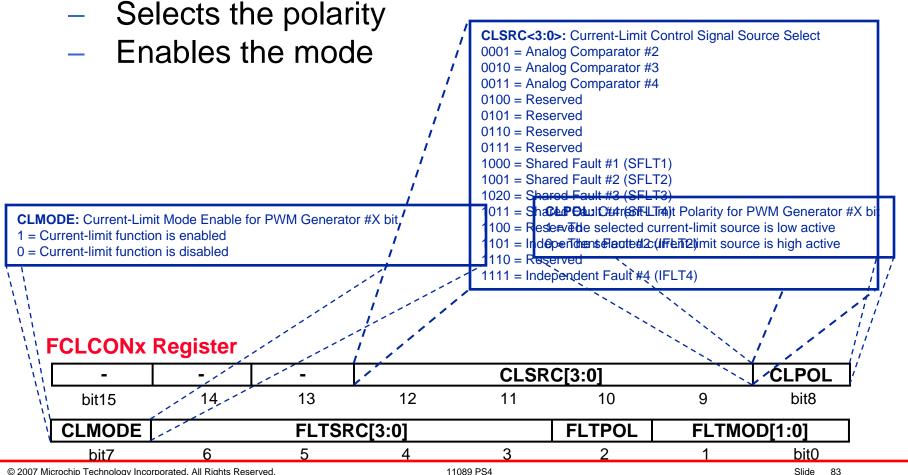

# The FCLCONx register controls the Fault and Current Limit Operations

Enables/disables the Fault operation

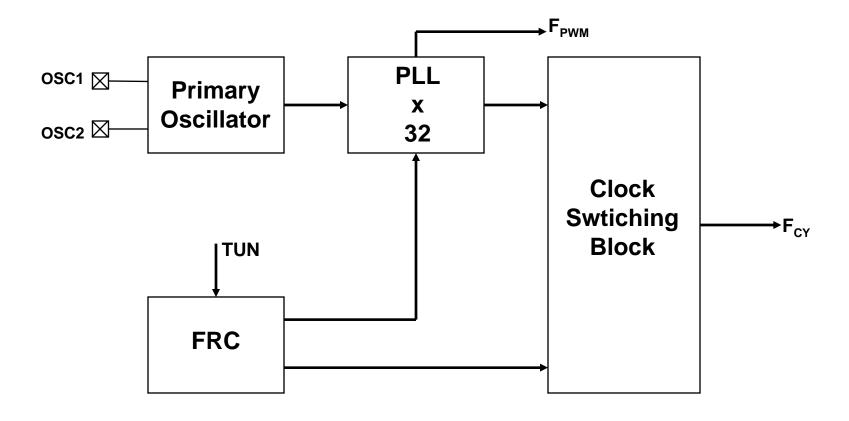

# Oscillator System

# **Oscillator System**

#### Oscillator System

- Dual Internal RC

- 9.7 and 14.55 MHz Industrial Temp

- 6.4 and 9.7 MHz Extended Temp

- 32x PLL with 480 MHz VCO

- External Source

- EC clock 6.0 to 14.55 MHz

- HS Crystal mode 6.0 to 14.55 MHz

#### Simplified Clock Block Diagram

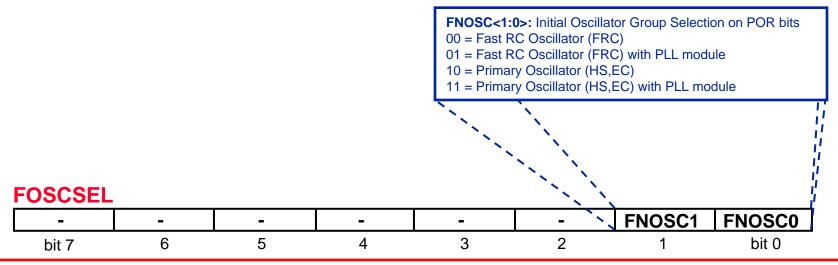

# **Oscillator System**

FOSCSEL: Oscillator Selection Configuration Bits

Oscillator Selection

# **Oscillator System**

FOSC: Osillator Selection Configuration Bits

Available Frequency Ranges

|   | FRANGE              | Temp.      | FR      | C Frequency | <i>'</i>      | PLL VC                | o                     |  |

|---|---------------------|------------|---------|-------------|---------------|-----------------------|-----------------------|--|

|   | FRANGE              | Range      |         | (Nominal)   |               | (Nominal)             |                       |  |

|   | 1 - High Dongo      | Industrial | 1       | 4.55 MHz    | 466           | MHz (480 N            | /IHz max)             |  |

|   | 1 = High Range      | Extended   | 9       | ).7 MHz     | 310           | MHz (320 M            | /IHz max)             |  |

|   | 0 – Low Pango       | Industrial |         | 9.7 MHz     | 310           | MHz (320 N            | /IHz max)             |  |

|   | 0 = Low Range       | Extended   | 6.4 MHz |             | 205           | 205 MHz (211 MHz max) |                       |  |

|   |                     |            |         |             |               |                       |                       |  |

|   |                     |            |         |             |               |                       |                       |  |

| F | osc                 |            |         |             |               |                       |                       |  |

| F | OSC<br>FCKSM [1:0]  | FRANGE     |         |             | OSCIOFNC      | POSCN                 | MD [1:0]              |  |

|   | FCKSM [1:0] bit 7 6 | FRANGE 5   |         | -<br>3      | OSCIOFNC<br>2 | POSCN<br>1            | <b>ID [1:0]</b> bit 0 |  |

|   | FCKSM [1:0]         |            | 4       |             |               | POSCN<br>1            |                       |  |

|   | FCKSM [1:0] bit 7 6 |            | 4       |             |               | POSCN<br>1<br>FNOSC1  |                       |  |

- Summary. We have seen:

- The basic Architecture of the IPP PWM

- The registers used to program the PWM functionalities

- The clock generation system

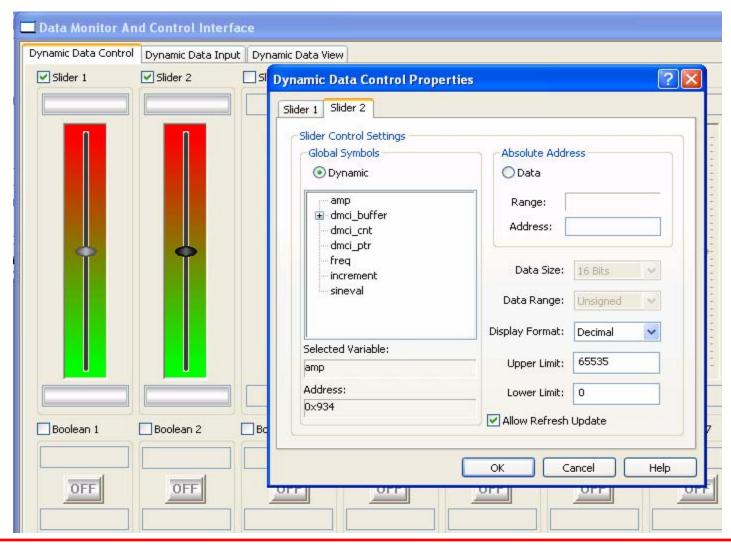

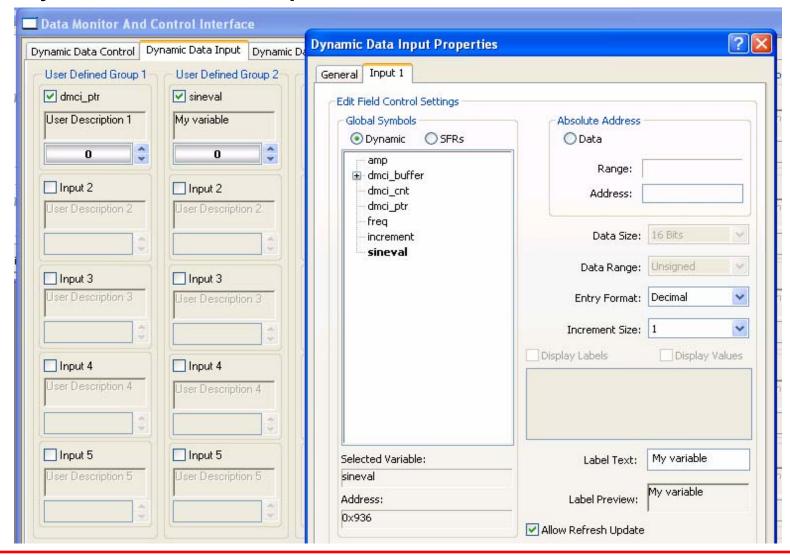

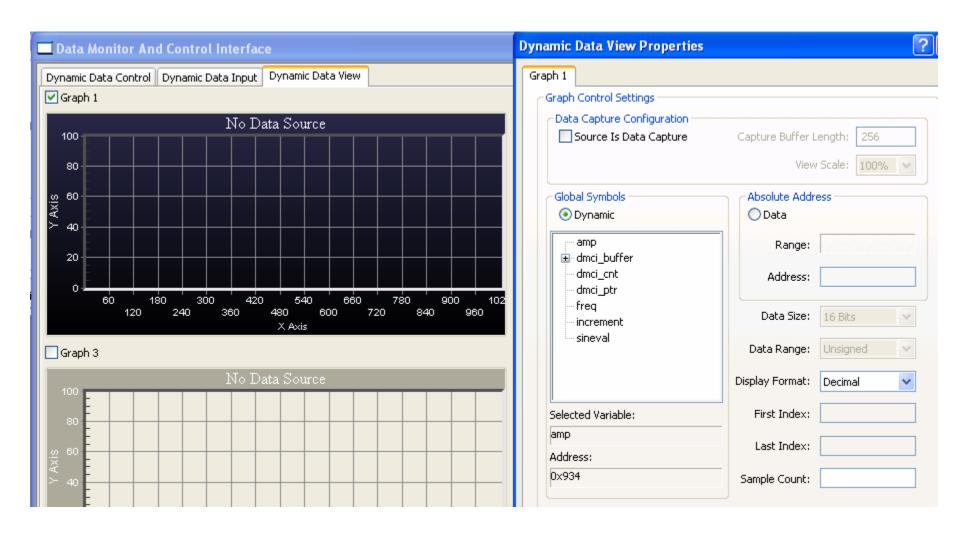

- New Graphical Tool in MPLAB® IDE

- Allows us to:

- Input variable values

- Display results graphically (up to four plots)

- The DMCI provides dynamic user configuration of:

- 9 slider controls

- 9 boolean (on/off) controls

- 35 input controls (7 groups of 5)

- 4 graphs

- A typical series of operational steps with the interface would be as follows:

- Compile the application software

- Set up the interface as desired

- Run the application

- Halt the application using the control button at the bottom of the tuning interface; the data will upload into the interface

- A typical series of operational steps with the interface would be as follows:

- If you are not satisfied with the system performance, you can change the various values on the Dynamic Data Control/Input tabs of the interface; once you are satisfied with the values, click the Start button on the dialog to update parameter values and resume the code execution

- Repeat the previous steps as required

- Once the application operation is satisfactory, you can use the Save button in the interface to save the desired parameter values to a file

#### Buttons

Run/Halt: "Run" write all values currently displayed on the Dynamic Data Control tab to the target RAM and continue code execution

"Halt" - Halt code execution, read all values from the target RAM and reflect those values on the dialog tabs

Save: Save the dialog settings to a \*.dmci file.

Load: Load the dialog settings from a \*.dmci file.

Refresh: Read all values from the target device RAM and reflect those values on the dialog tabs.

#### Buttons

Exit: Exit from the interface dialog. Note: The

dialog always opens with default values. To

save your settings, click Save. Then load

your settings after you reopen the dialog at

another time.

Help: On-line help information

#### **Dynamic Data Control**

#### **Dynamic Data Input**

#### **Dynamic Data View**

- Summary. We have seen:

- What the DMCI is

- How we can use it to change parameter values

- How we can use it to monitor the behavior of our system

- Lab 1 is intended to:

- Review the IPP PWM achitecture

- Initialize the PWM peripheral

- Use the DMCI

- In this Lab, you will:

- Part 1

- Initialize PWM 2

- Initialize PWM 3

- Part 2

- Experiment with the DMCI Interface to change the features of the duty cycle of PWM 1

PWM1 is already initialized

#### Solution

```

PWM 2

Independent time base

Independent duty cycle

Frequency 150 KHz

Complimentary output

Duty cycle = 25 %

Dead band of 50 nsec rising edge

Dead band of 100 nsec falling edge

PWMCON2 = (unsigned int) 0x0200;

PHASE2 = (unsigned int) PWM2_TBASE;

PDC2 = (unsigned int) (PWM2_TBASE >> 2);

DTR2 = (unsigned int) DTIME 50NS:

ALTDTR2 = (unsigned int) DTIME 100NS;

TRGCON2 = (unsigned int) 0x0000;

IOCON2 = (unsigned int)0xC000;

FCLCON2 = (unsigned int) 0x0003;

TRIG2 = (unsigned int) 0x0000;

LEBCON2 = (unsigned int) 0x0000

```

#### Solution

```

PWM 3

Independent time base

Independent duty cycle

Frequency 150 KHz

Push-pull output

Duty cycle = 50 %

No dead band

PWMCON3 = (unsigned int) 0x0280;

PHASE3 = (unsigned int) PWM3_TBASE;

PDC3 = (unsigned int) (PWM3_TBASE >> 1);

DTR3 = (unsigned int) 0x0000;

ALTDTR3 = (unsigned int) 0x0000;

TRGCON3 = (unsigned int) 0x0000;

IOCON3 = (unsigned int)0xC800;

FCLCON3 = (unsigned int) 0x0003;

TRIG3 = (unsigned int) 0x0000;

LEBCON3 = (unsigned int) 0x0000;

```

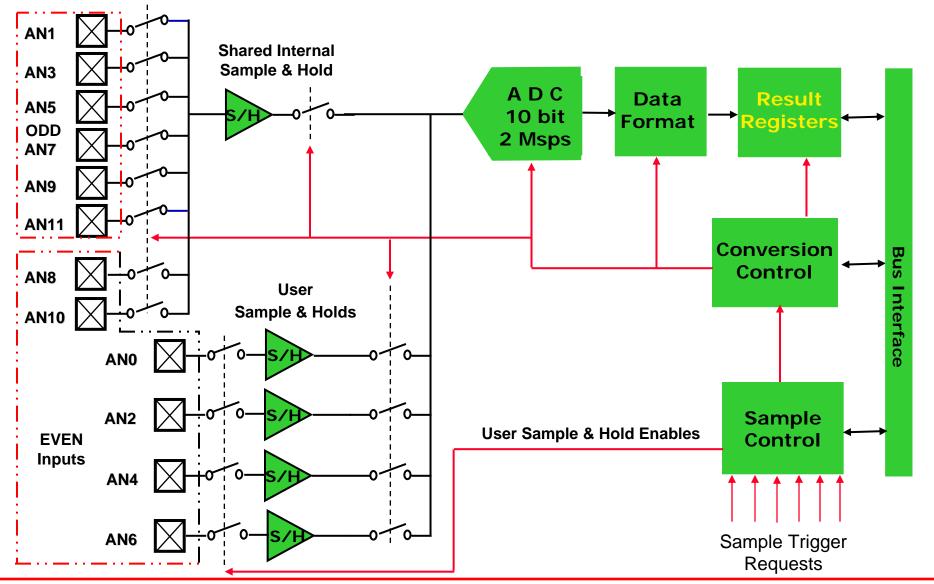

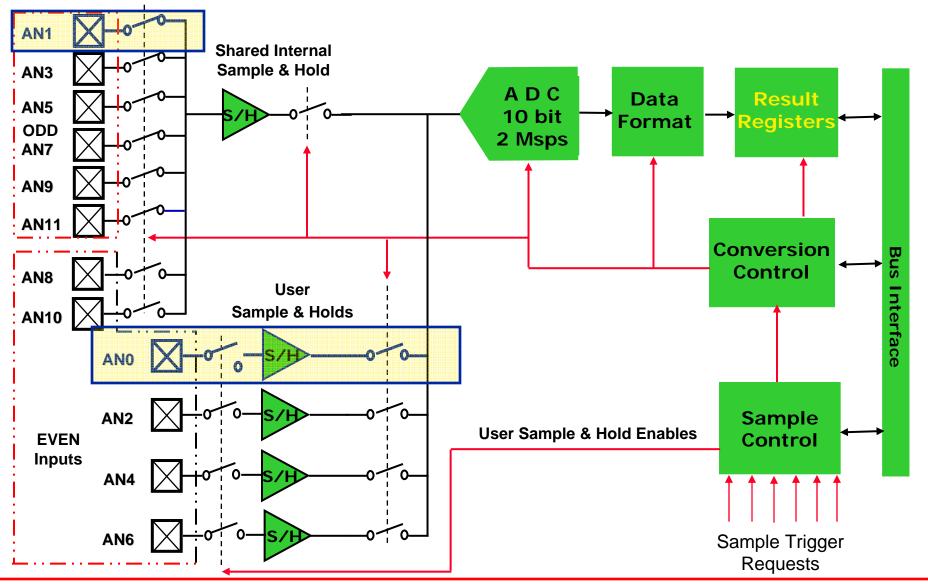

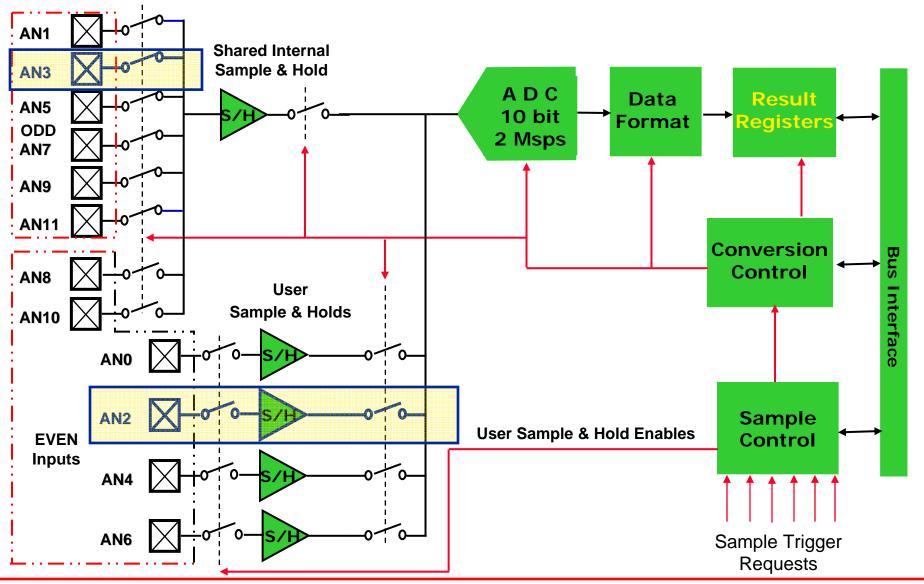

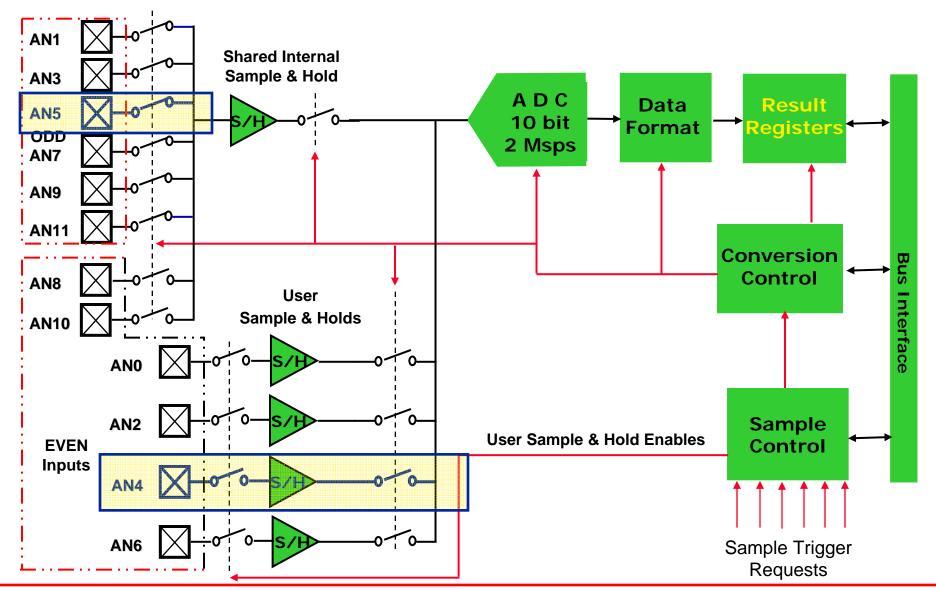

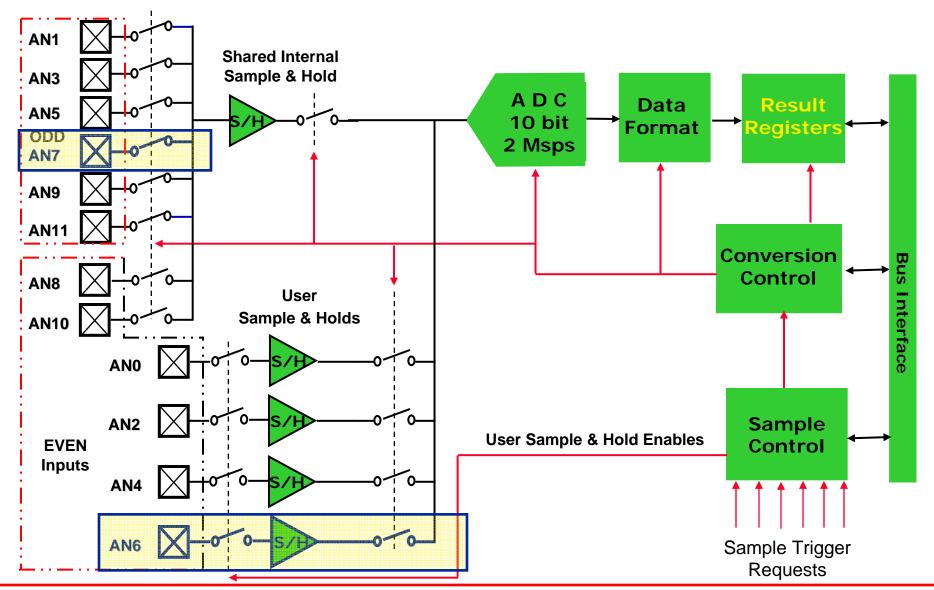

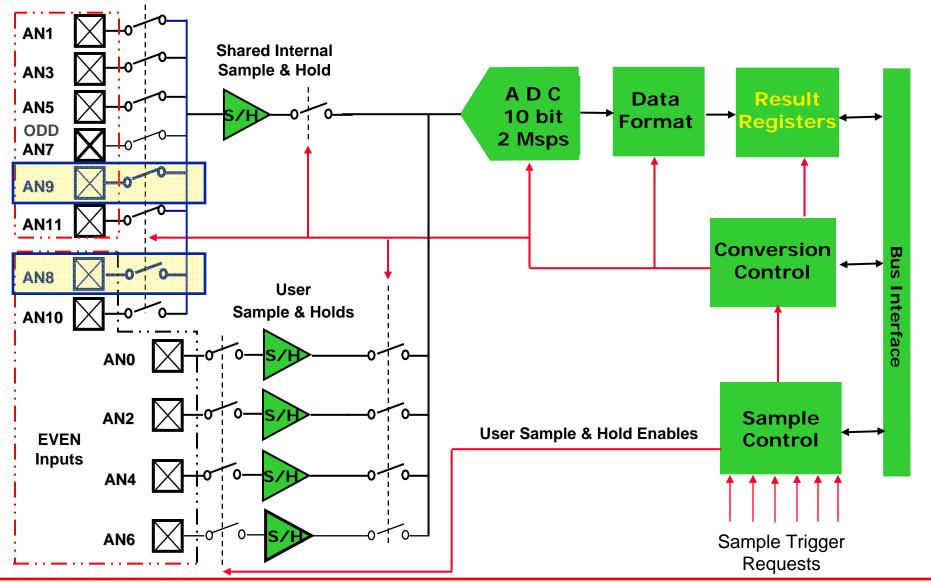

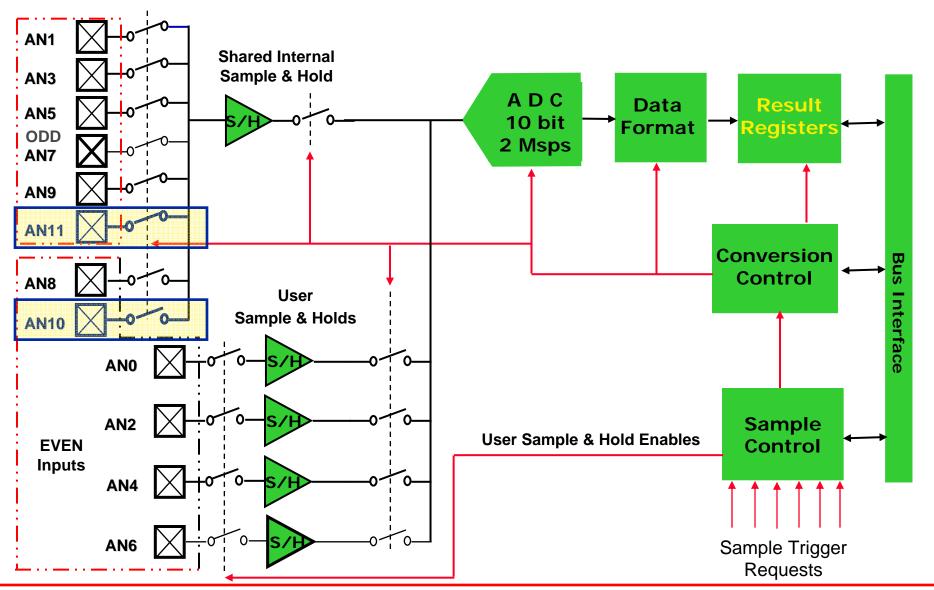

# A/D Converter

#### General Features

- 10 bit Resolution, +/- 1 bit accuracy

- 2 Million Samples / sec conversion rate

- 6 to 12 input channels

- Analog Input Range: 0 to 5V

- Low latency improves control loop stability

- Advanced Sampling Capability:

- Individual triggers for each S&H

- Samples may be simultaneous

- Samples may be uniquely timed

- Sample acquisitions are precisely timed

- The SMPS ADC samples and converts inputs independently, and asynchronously of each other

- Data capture from time critical events is simplified with sophisticated triggering capabilities

- Conversions are ALWAYS performed in "pairs" of analog inputs: (AN0, AN1), (AN2, AN3), etc ...

- Pairs represent voltage and current measurements

- Output Buffers

- Each analog input pin has an associated output data register

- The data buffers (registers) are NOT implemented as a **FIFO**

- They are uniquely owned by each input

- Interrupt Management

- Interrupt requests are generated on a per pair basis

- Interrupts may be generated at the completion of first or second conversion of the pair

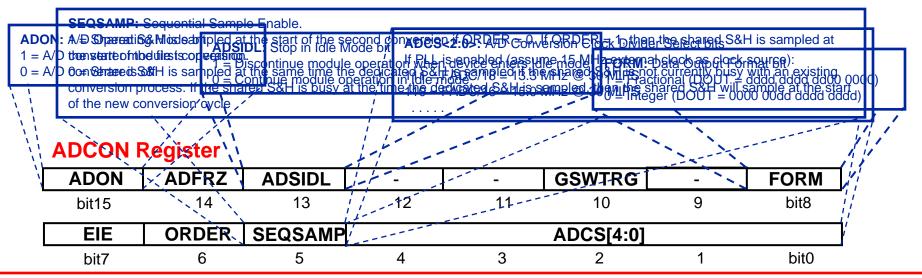

#### **ADCONx Register**

- Enables the peripheral

- Controls its operation in idle

- Defines the data output format

- Enables sequential sampling

- Defines the ADC clock

#### ADPCFG<11:0>: A/D Port Configuration Control bits

- 1 = Port pin in Digital mode, port read input enabled

- 0 = Port pin in Analog mode, port read input disabled

#### **ADPCFGx Register**

| -     | -     | -     | -     | PCFG11 | PCFG10 | PCFG9 | PCFG8 |

|-------|-------|-------|-------|--------|--------|-------|-------|

| bit15 | 14    | 13    | 12    | 11     | 10     | 9     | bit8  |

| PCFG7 | PCFG6 | PCFG5 | PCFG4 | PCFG3  | PCFG2  | PCFG1 | PCFG0 |

| bit7  | 6     | 5     | 4     | 3      | 2      | 1     | bit0  |

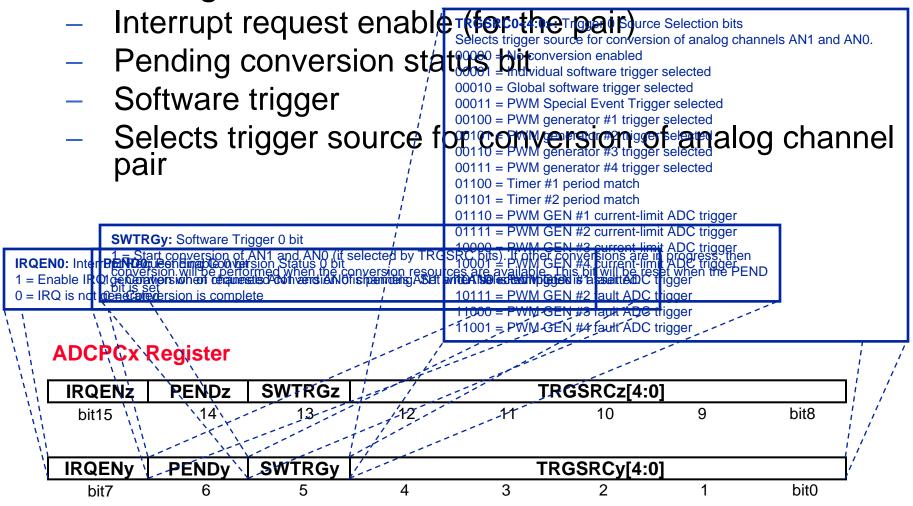

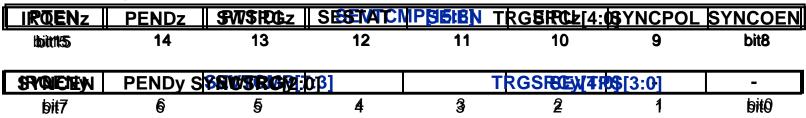

#### ADCPCx register:

- The ADCPCx registers:

- Association to the channels pairs

|                        | <b>ADCPC</b>                | 2 Regi | ster   |              |     |          |    |      |

|------------------------|-----------------------------|--------|--------|--------------|-----|----------|----|------|

| Channels AN10 and AN11 | IRQENz                      | PENDz  | SWTRGz |              | TRO | SRCz[4:0 | 0] |      |

|                        | bit15                       | 14     | 13     | 12           | 11  | 10       | 9  | bit8 |

| Channels AN8 and AN9   | IRQENy                      | PENDy  | SWTRGy | TRGSRCy[4:0] |     |          |    |      |

|                        | bit7                        | 6      | 5      | 4            | 3   | 2        | 1  | bit0 |

| ADCPC1 Register        |                             |        |        |              |     |          |    |      |

| Channels AN6 and AN7   | IRQENz                      | PENDz  | SWTRGz | TRGSRCz[4:0] |     |          |    |      |

|                        | bit15                       | 14     | 13     | 12           | 11  | 10       | 9  | bit8 |

| Channels AN4 and AN5   | IRQENy PENDy SWTRGy TRGSRCy |        |        | SRCy[4:0     | 0]  |          |    |      |

|                        | bit7                        | 6      | 5      | 4            | 3   | 2        | 1  | bit0 |

|                        | <b>ADCPC</b>                | 0 Regi | ister  |              |     |          |    |      |

| Channels AN2 and AN3   | IRQENz                      | PENDz  | SWTRGz | TRGSRCz[4:0] |     |          |    |      |

|                        | bit15                       | 14     | 13     | 12           | 11  | 10       | 9  | bit8 |

| Channels AN0 and AN1   | IRQENy                      | PENDy  | SWTRGy | TRGSRCy[4:0] |     |          |    |      |

|                        | bit7                        | 6      | 5      | 4            | 3   | 2        | 1  | bit0 |

#### Interrupts

The ADC module provides a common or "Group" interrupt request that is the OR of all of the enabled interrupt sources within the module

| Global Interrupt Flag Status Register    | IFS0: ADIF      |

|------------------------------------------|-----------------|

| Global Interrupt Enable Control Register | IEC0: ADIE      |

| Interrupt Priority Control Register      | IPC2: ADIP[2:0] |

#### Interrupts

- Each ADCPC register has two IRQENx bits, one for each analog input pair; if the IRQEN bit is set, an interrupt request is made to the interrupt controller when the requested conversion is completed

- When an interrupt is generated, an associated PxRDY bit in the ADSTAT register is set

| ADC Pair x Interrupt Flag Status Register      | IFS2: ADCPxIF  |  |  |

|------------------------------------------------|----------------|--|--|

| ADC Pair x Interrupt Enable Control Register   | IEC2: ADCPxIE  |  |  |

| ADC Dair v Interrupt Drigrity Control Degister | IPC9: ADCPxIP  |  |  |

| ADC Pair x Interrupt Priority Control Register | IPC10: ADCPxIP |  |  |

- Sample and Conversion

- The ADC module assigns two ADC clock periods for the sampling process

- When operating at 24 MHz clock, the sampling period is:

- $2 \times 41.6 \text{ nsec} = 83.3 \text{ nsec}$ .

- Sample and Conversion

- Each ADC pair specified in the ADCPCx registers initiates a sample operation when the selected trigger event occurs

- The conversion of the sampled data occurs as resources become available

- The actual conversion process requires 10 additional ADC clocks

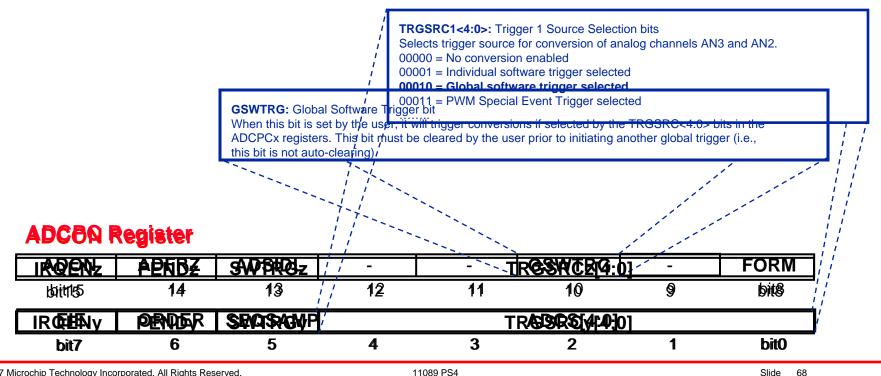

- Global Software Trigger

- Start Conversion Setting a Bit

- Select the Trigger Source per Pair

- Individual Software Trigger

- Select the Trigger Source per Pair

- Enable the Interrupt Request

- Start Conversion Setting a Bit

- ISR Code: ADCInterrupt

#### **ADCPCx Register**

| IRQENz | PENDz | SWTRGz | TRGSRCz[4:0] |    |    |   |      |  |

|--------|-------|--------|--------------|----|----|---|------|--|

| bit15  | 14    | 13     | 12           | 11 | 10 | 9 | bit8 |  |

| IRQENy | PENDy | SWTRGy | TRGSRCy[4:0] |    |    |   |      |  |

| bit7   | 6     | 5      | 4            | 3  | 2  | 1 | bit0 |  |

- Special Event Trigger (Master Period/Duty)

- Set Value in PWM Peripheral Register SEVTCMP

- Set Interrupt Enable bit and Postscaler in PWM Register PTCON

- Select ADC Trigger Source in ADC Register ADCPCx

- ISR Code: PWMSpEventMatchInterrupt

#### SPOEDWAREGUISEE'r

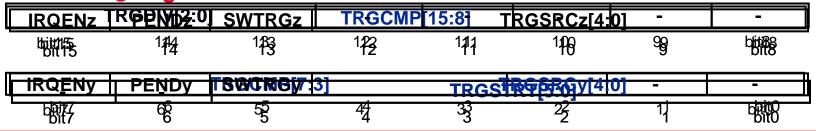

- Individual Triggers (Individual Period/Duty)

- Set Value in PWM Peripheral Register TRIGx

- Select the Trigger Output Divider in PWM Peripheral Register TRGCONx

- Select the Postscaler for Staggering Operation in PWM Peripheral Register TRGCONx

- Select ADC Trigger Source in ADC Register ADCPCx

#### ARGCO Registerster

Triggers can be staggered relative to other PWM generated triggers on a PWM Period Basis

### IPP ADC

Summary. We have seen:

- The basic architecture of the IPP ADC

- How to program it to get the best performances

- The triggering capabilities

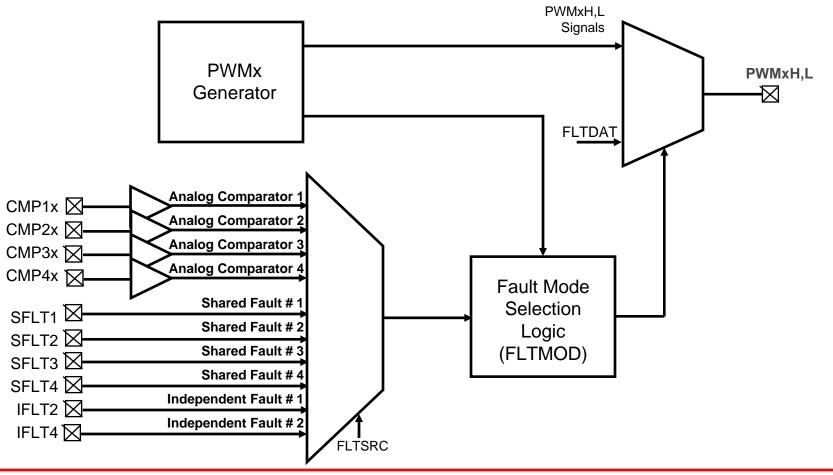

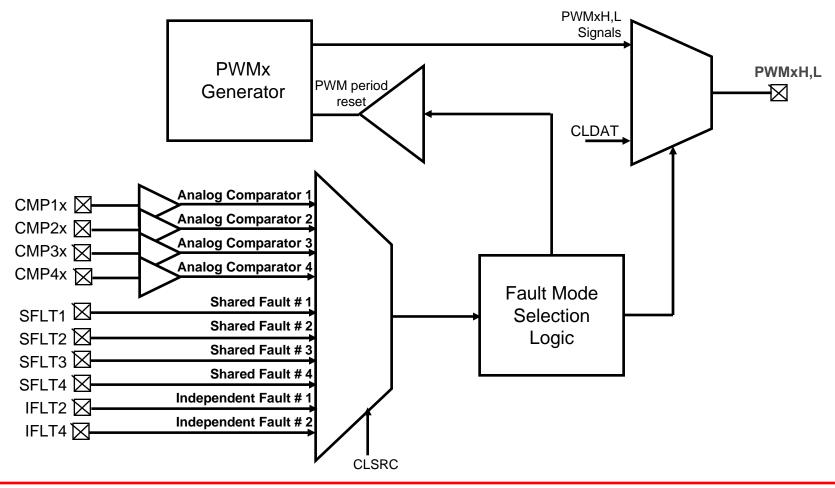

# **Fault Generation**

- The Fault pins actually serve two different purposes:

- Generation of Fault overrides for the PWM outputs; the action of overriding the PWM outputs is performed asynchronously in hardware

- The Fault pin inputs can be used to implement either Current-Limit PWM mode

#### Bock Diagram

#### FCLCONx register:

- Selects the fault input source for each PWM

- Selects the fault polarity

- Selects the operating mode

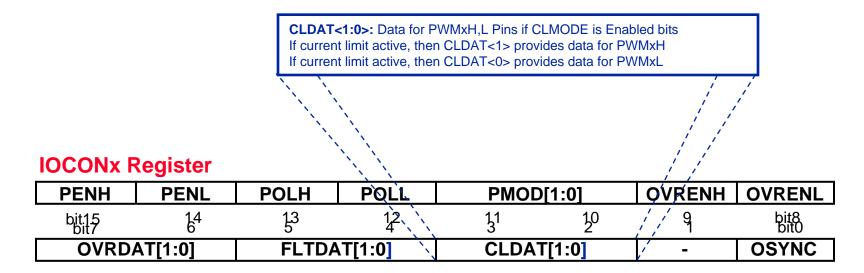

#### The IOCONx register:

Select the values output on PWMH and PWML when a **Fault Event Occurs**

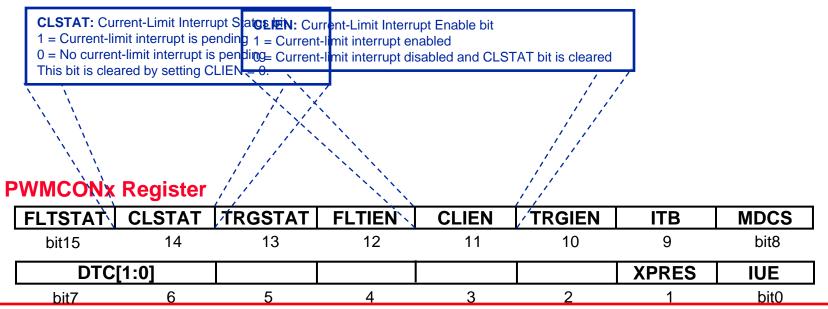

#### The PWMCON register:

- Enables the fault interrupt

- Pending Interrupt Status Bit

- The current-limit pins actually serve two different purposes

- Current-Limit PWM mode

- If the selected current-limit input signal is asserted the PWMxH,L outputs are forced to the values specified by the CLDAT<1:0> bits in the IOCONx register

- Current Reset PWM mode

- A current-limit signal resets the time base if:

- CLMOD bit is zero (current limit disabled)

- XPRES bit in the PWMCONx register is '1'

- The PWM generator is in Independent Time Base mode

- This is used in some PFC applications

#### **Block Diagram**

#### FCLCONx register:

Selects the Current limit input signal

#### IOCONx register:

Select the values output on PWMH and PWML when a Fault Event Occurs

#### The PWMCON register:

- Enables the current-limit interrupt

- Pending Interrupt Status Bit

Summary. We have seen:

- Fault operation

- Current limiting operation

### **SMPS and ICD2**

#### SMPS Devices and ICD2

- When the ICD 2 halts the device the PWM pins takes the characteristics of the GPIO that is muxed on that pin

- PWM1L and PWM1H are muxed with RE0 and RE1

- If TRISE = 0x00FF then the pins will be tri-stated on a halt

- If TRISE = 0x00FC and PORTE = 0x0000 then the pins will drive low on a halt

- We can configure how the PWM pins behave on an ICD2 halt

## **Buck Board**

- Lab 2 is intended to:

- Review the PWM Fault

- Review Current Limit capabilities

- In this Lab, you will:

- Part A

- Initialize PWM 1: fault (cycle condition)

- Initialize PWM 2: fault (latched condition)

- Cycle Condition Operation

- Part B

- **Latched Condition Operation**

- Part C

- **Optional**

### Solution

```

// PWM 1: Fault control

// Independent Time Base (ITB = 1)

// Independent duty cycle (MDCS = 0)

// Complimentary output

// Dead time disabled

// Fault input at SFLT1

// Output low in fault

// Cycle condition

PWMCON1 = (unsigned int) 0x0280;

PDC1 = (unsigned int) (PWM1_TBASE >> 1);

PHASE1 = ( unsigned int ) ( PWM1_TBASE );

DTR1 = (unsigned int) 0x0000;

ALTDTR1 = (unsigned int) 0x0000;

TRGCON1 = (unsigned int) 0x0000;

IOCON1 = (unsigned int) 0xC000;

FCLCON1 = (unsigned int) 0x0041;

TRIG1 = (unsigned int) 0x0000;

LEBCON1 = (unsigned int) 0x0000;

```

#### Solution

```

// PWM 2: Fault control

// Master Time Base (ITB = 0)

// Master duty cycle (MDCS = 1)

// Complimentary output

// Dead time disabled

// Fault input at SFLT1

// Output low in fault

// Latched condition

PWMCON2 = (unsigned int) 0x0180;

PDC2 = (unsigned int) 0x0000;

PHASE2 = (unsigned int) 0x0000;

DTR2 = (unsigned int) 0x0000;

ALTDTR2 = (unsigned int) 0x0000;

TRGCON2 = (unsigned int) 0x0000;

IOCON2 = (unsigned int) 0xC000;

FCLCON2 = (unsigned int) 0x0040;

TRIG2 = (unsigned int) 0x0000;

LEBCON2 = (unsigned int) 0x0000;

```

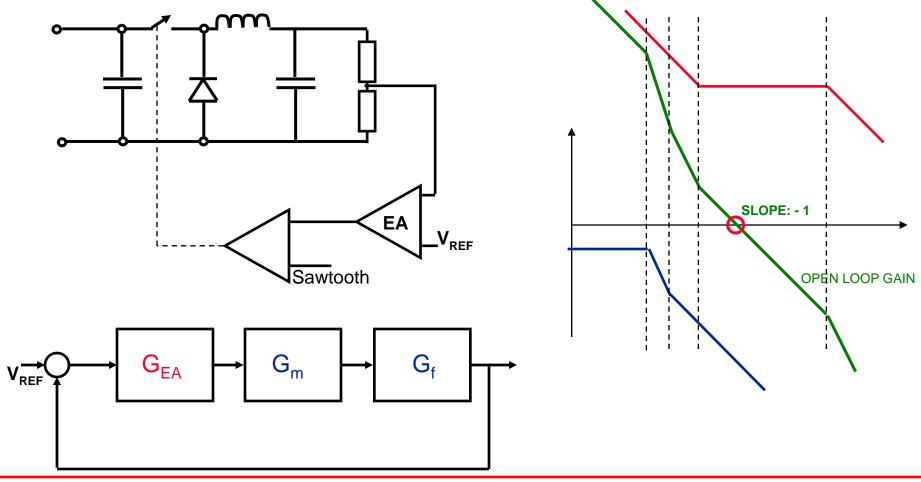

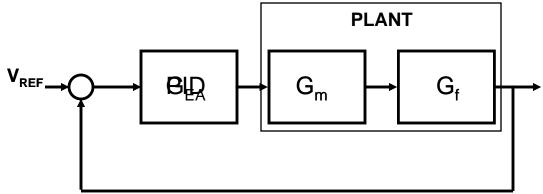

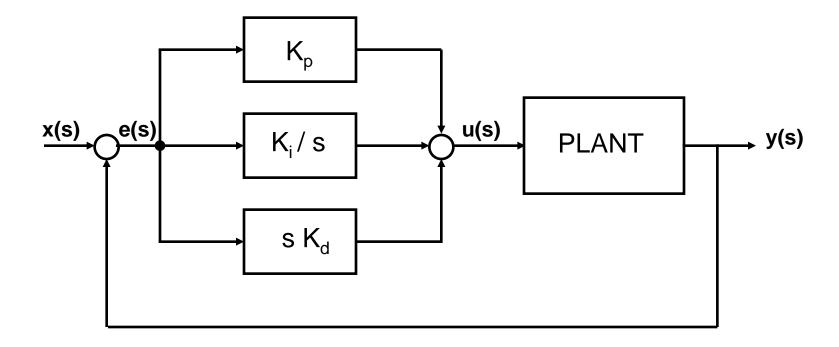

#### Classical Feedback-Loop Stabilization

#### From Analog to Digital

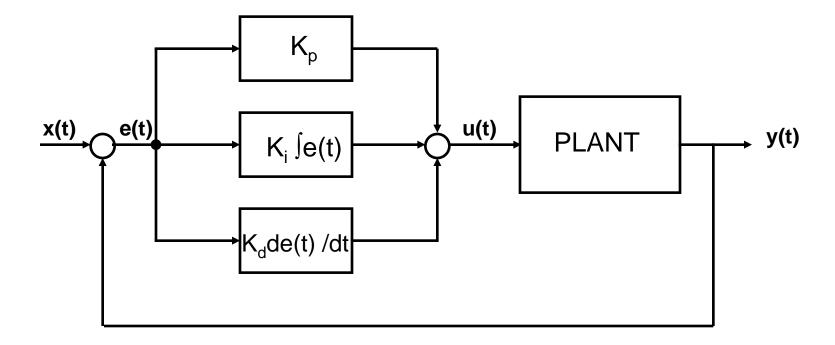

PID = Error Amplifier Gain P Proportional

I = Integrative

D = Derivative

PID Structure in Analog: TimeDomain

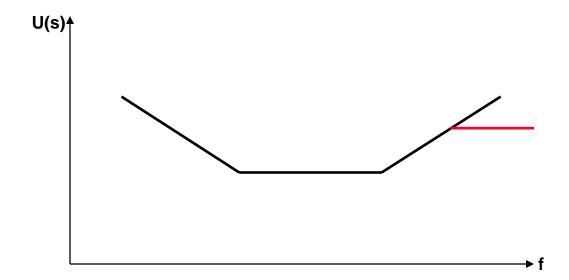

PID Structure Analog: Frequency Domain (Laplace Transform)

#### Output in the Analog Domain

$$u(t) = K_{p}e(t) + K_{i} \int e(t)dt + K_{d} \frac{de(t)}{dt}$$

$$U(s) = K_{p} + \frac{K_{i}}{s} + K_{d}s = \frac{K_{d}s^{2} + K_{p}s + K_{i}}{s}$$

$$U(s) = K_p + \frac{K_i}{s} + K_d s = \frac{K_d s^2 + K_p s + K_i}{s}$$

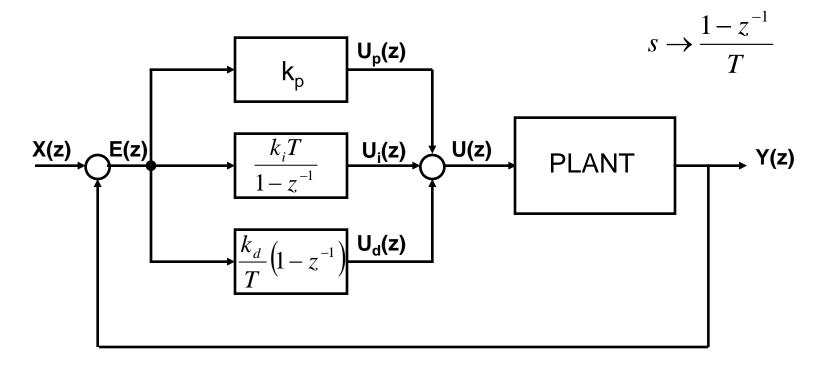

PID: Derivation from Analog Counterpart (Z Transform)

#### **PID Equations**

$$U_p(z) = k_p E(z)$$

$$U_{i}(z) = \frac{k_{i}T}{1-z^{-1}}E(z)$$

$$U_d(z) = \frac{k_d}{T} (1 - z^{-1}) E(z) \Longrightarrow$$

$$\begin{array}{c|c}

E(z) & U_p(z) \\

\hline

\end{array}$$

$$\begin{array}{c|c} \textbf{E(z)} & k_i T & \textbf{U_i(z)} \\ \hline 1 - z^{-1} & \end{array}$$

$$\begin{array}{c|c}

\hline

\mathbf{E(z)} & \overline{k_d} \left( 1 - z^{-1} \right) \\

\hline

T & \end{array}$$

$$U(z) = \left[ k_p + \frac{k_i T}{1 - z^{-1}} + \frac{k_d}{T} (1 - z^{-1}) \right] E(z)$$

#### **PID Equations**

$$U(z) = \frac{\left(k_{p}T + k_{i}T^{2} + k_{d}\right) - \left(k_{p}T + 2k_{d}\right)z^{-1} + k_{d}z^{-2}}{T\left(1 - z^{-1}\right)}E(z) \Rightarrow$$

$$U(z)(1-z^{-1}) = \left[K_A + K_B z^{-1} + K_C z^{-2}\right] E(z)$$

where

$$K_A = k_p + k_i T + \frac{k_d}{T}; K_B = -(k_p + 2\frac{k_d}{T}); K_C = \frac{k_d}{T}$$

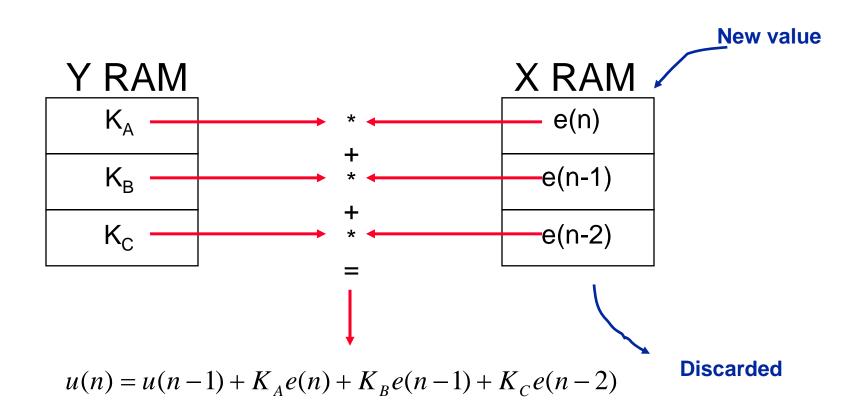

#### **PID Equations**

$$U(z)(1-z^{-1}) = [K_A + K_B z^{-1} + K_C z^{-2}]E(z)$$

$$\Rightarrow$$

$$u(n) = u(n-1) + K_A e(n) + K_B e(n-1) + K_C e(n-2)$$

#### Influence of P,I,D on Performances

| Closed Loop<br>Response | Rise Time    | Overshoot | Settling Time | Steady-State<br>Error |

|-------------------------|--------------|-----------|---------------|-----------------------|

| $K_p$                   | Decrease     | Increase  | Small Change  | Decrease              |

| K <sub>i</sub>          | Decrease     | Increase  | Increase      | Eliminate             |

| K <sub>d</sub>          | Small Change | Decrease  | Decrease      | Small Change          |

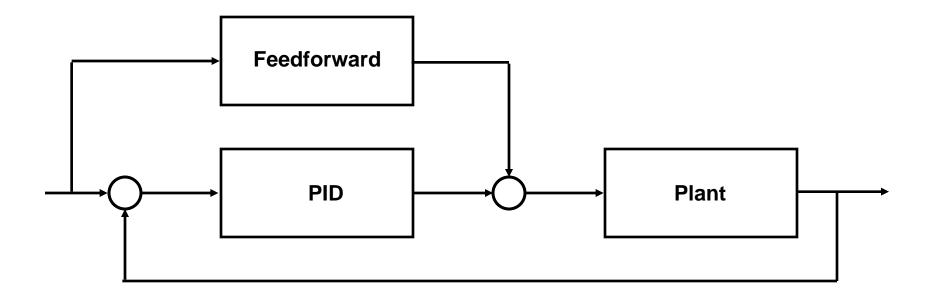

Improvements to the Basic PID Design

**FeedForward**

#### Additional Improvements

#### Also consider as errors:

- Second derivative (jerk): improves transient response

- Excess Current: reduce command if limit exceeded

- Dead Time Delay: removes offset caused by dead-time

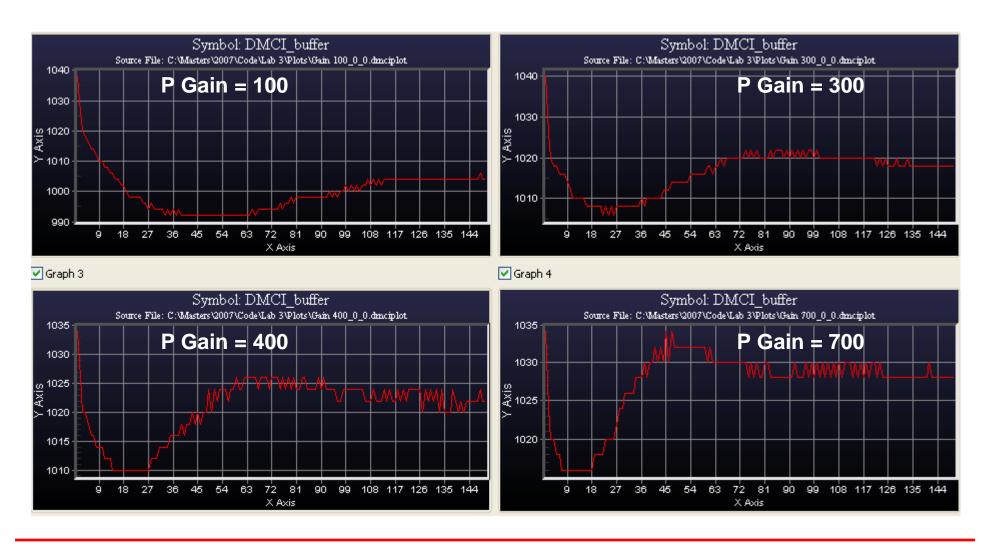

#### **Proportional Gain Effects**

# **PID Control Loop**

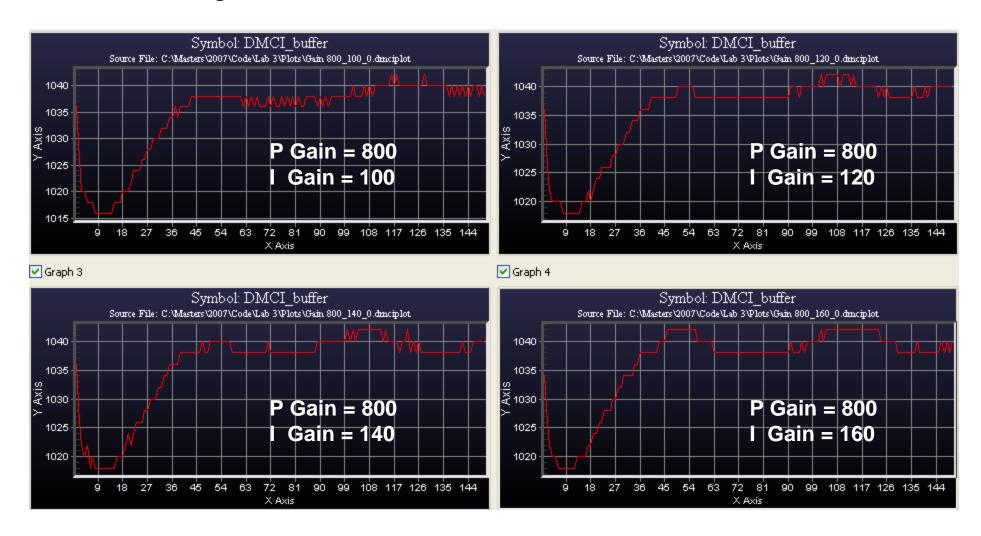

#### **Integrative Gain Effects**

## **PID Control Loop**

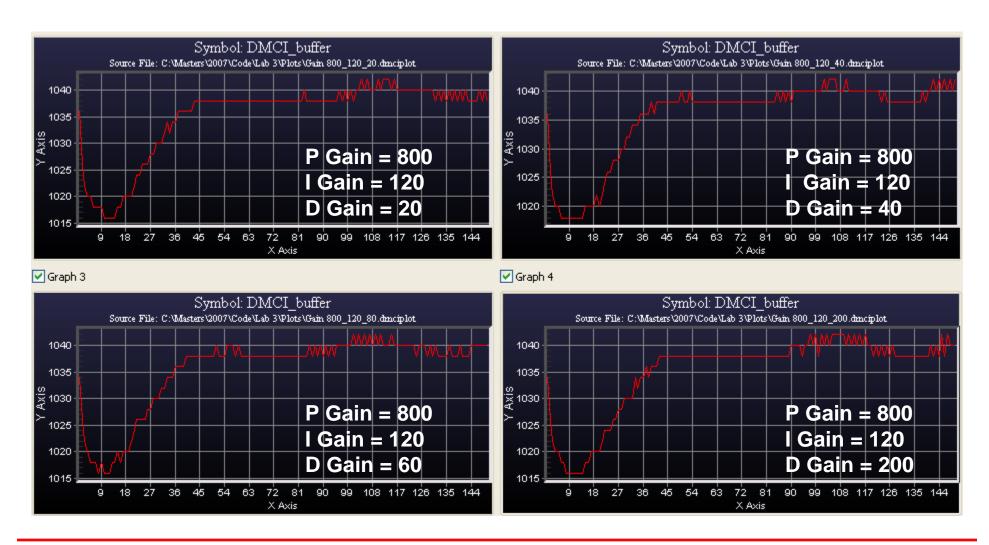

#### **Derivative Gain Effects**

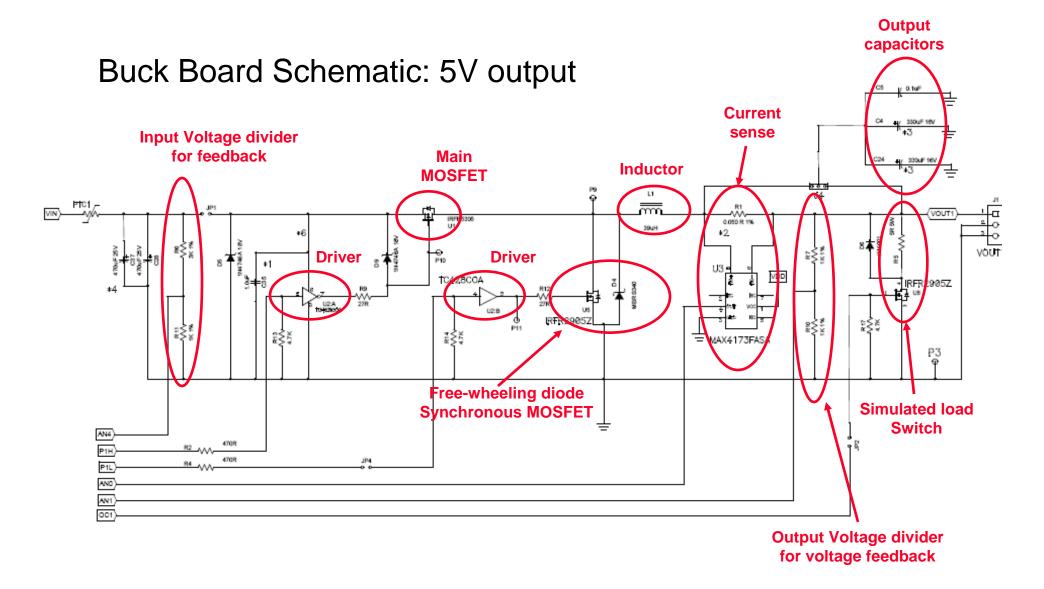

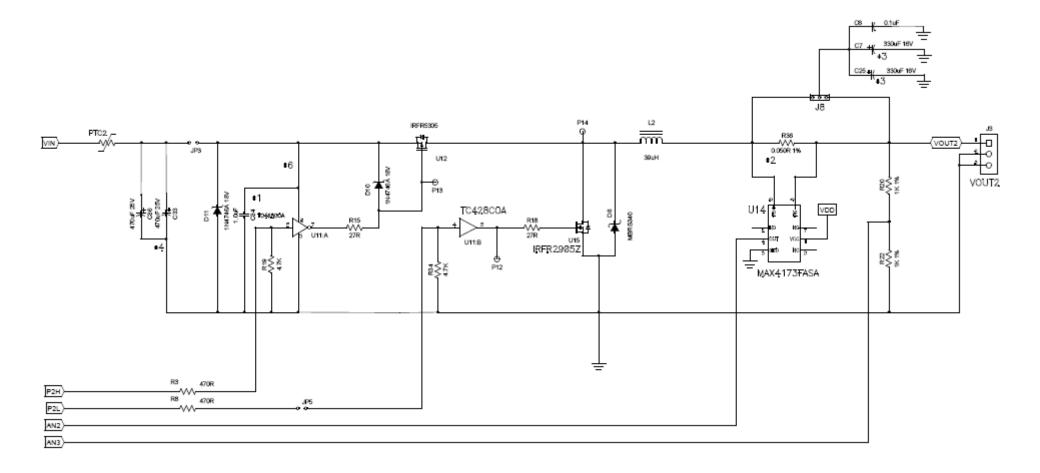

# **Buck Board Hardware**

### **Buck Board Hardware**

### **Buck Board Hardware**

Buck Board Schematic: 3.3V output

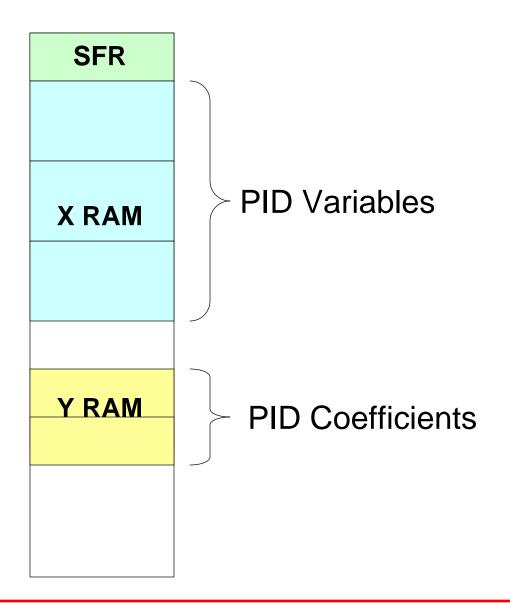

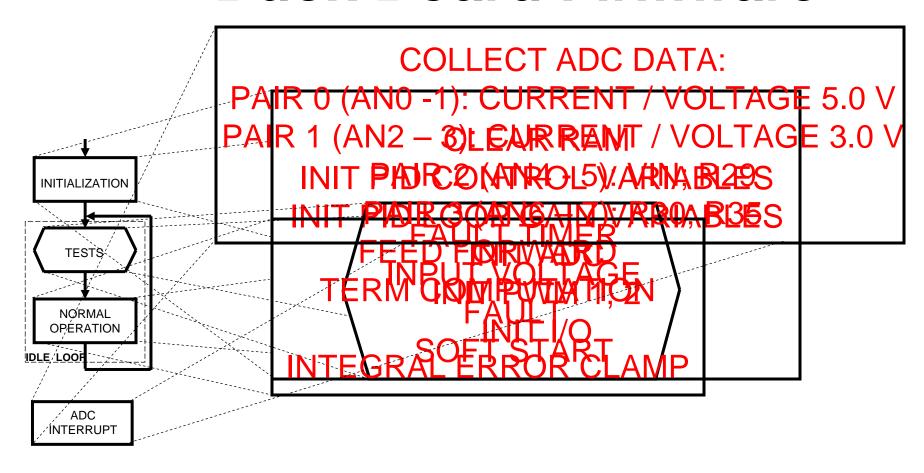

30 VOLT VARIABLES SFR SYSTEM VARIABLES 3.0 VOLT PID COEFFICIENTS XRAM PROPORTIONAL ERROR GAIN INTEGRAL\_ERROR\_GAIN DERIVATIVE ERROR GAIN JERK ERROR GAIN Y RAM EXCESS\_CURRENT\_GAIN FEED FORWARD GAIN DEAD TIME GAIN

### PID computations performed in main idle loop

#### EXCESS-CURRENT =

ACTUAL CURRENT – MAXIMUM ALLOWED CURRENT (If there is an excessive current issue, do not update integral error)

#### FD FWD VOLT CMD =

Vout = Vin \* DUTY\_CYCLE

### PID computations performed in ADC interrupt function

#### PROPORTIONAL ERROR =

COMMANDED OUTPUT – CURRENT OUTPUT VOLTAGE

#### INTEGRAL ERROR =

PROPORTIONAL ERROR > 0 ⇒ INCREMENT INTEGRATOR PROPORTIONAL ERROR < 0 ⇒ DECREMENT INTEGRATOR

#### DERIVATIVE ERROR =

CURRENT VOLTAGE ERROR – PREVIOUS VOLTAGE ERROR

#### JERK ERROR =

CURRENT DERIVATIVE ERROR – PREVIOUS DERIVATIVE ERROR

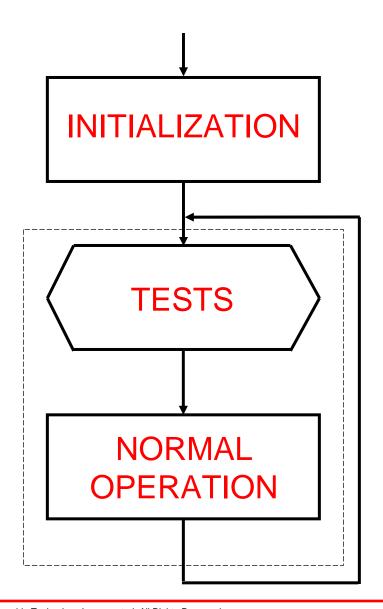

ADC INTERRUPT

#### A voltage control loop is implemented

#### PID OUTPUT =

```

PROPORTIONAL ERROR

PROPORTIONAL ERROR GAIN

INTEGRAL ERROR

INTEGRAL ERROR GAIN

DERIVATIVE ERROR

DERIVATIVE ERROR GAIN

JERK_ERROR_GAIN

JERK ERROR

EXCESS_CURRENT

EXCESS_CURRENT_GAIN

FD_FWD_VOLT_CMD_GAIN

FD FWD VOLT CMD

+

DEAD TIME

*

DEAD TIME GAIN

```

| PWM Period                 | PWM                 | PWM                | PWM                 | PWM                 | PWM                 | PWM                 |

|----------------------------|---------------------|--------------------|---------------------|---------------------|---------------------|---------------------|

| #                          | #1                  | #2                 | #3                  | #4                  | #5                  | #6                  |

| Control<br>Loop on         | 5V buck             | 3.3 V buck         | None                | 5V buck             | 3.3 V buck          | None                |

| Exec time for control loop | 2.0 us              | 2.0 us             | 0                   | 2.0 us              | 2.0 us              | 0                   |

| Period<br>length           | 2.5 us<br>(400 Khz) | 2.5 us<br>(400Khz) | 2.5 us<br>(400 Khz) | 2.5 us<br>(400 Khz) | 2.5 us<br>(400 Khz) | 2.5 us<br>(400 Khz) |

|                            |                     |                    |                     |                     |                     |                     |

|                            |                     |                    |                     |                     |                     |                     |

- 4us out of 7.5 are used in the loop computation (53%)

- There is enough room for the main loop

## **PID Control Loop**

- Summary. We have seen:

- What a PID is

- What are its performances

- How the PID has been inmplemented in the software of the Buck Demo Board

- What is the associated timing

# Lab 3

### Lab 3

# You can experience how the PID coefficients influence the system behavior

- Start with I and D gain = 0

- Increase P gain until you get an output value close to the desired one

- Increase I gain in order to decrease the residual error

- Increase D gain to reduce overshoot and settling time

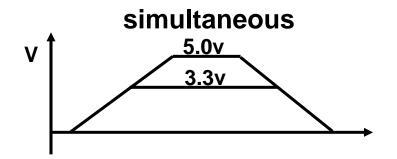

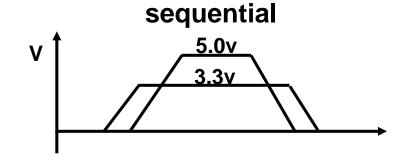

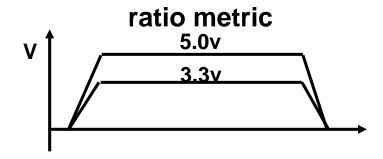

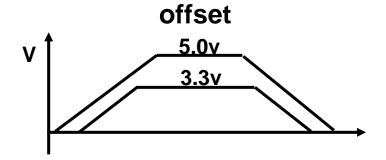

- Sequencing is the process of generating two or more voltages with a specific profile and a specific time relation between them

- Many electronic devices require their multiple supply voltages be coordinated at power on and off to protect their circuitry

- If the supply voltages are improperly applied, many integrated circuits can experience "Latch-up"

- Other systems require that specific circuitry be powered prior (to put it in a known safe state) to the rest of the load circuitry

- The most common power supply sequencing method is the simultaneous ramp up and down

- The choice of power sequencing is very dependent on the system requirements

Choose the method that meets system requirements

#### Dev Tools Used in This Class:

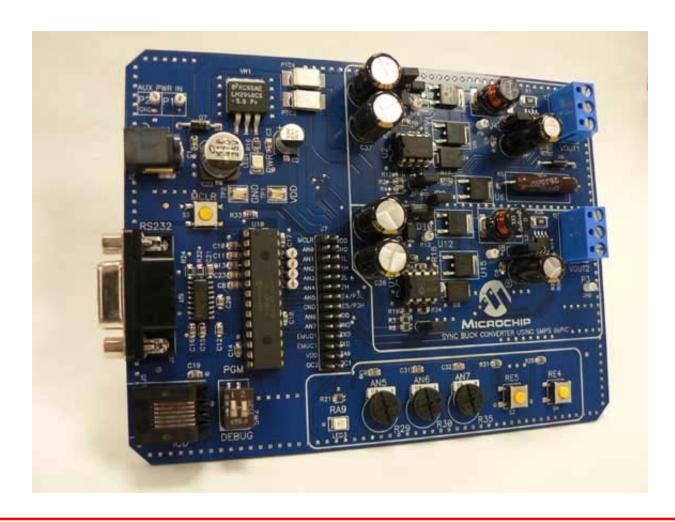

dsPICDEM™ SMPS Buck Board (DM300023)

MPLAB® ICD2 In-Circuit Debugger (DV164005)

# Thank You

### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KeeLoq, KeeLoq logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.