## **11011 EXP**

#### Advanced 16 bit Peripheral Configuration and MPLAB® C30 Programming Techniques

### **Class Objective**

# When you finish this class you will:

- Be familiar with using some of the advanced peripherals onboard Microchip's 16-bit devices

- Be familiar with using MPLAB<sup>®</sup> IDE with the C30 compiler

- Be familiar with using the Explorer16 Development Board

### Agenda

#### 16-bit Devices

- 16-bit Refresher

- CPU architecture

- New Peripherals and Features

- PPS with hands-on

- PMP with hands-on

- RTCC with hands-on

- CRC Generator with hands-on

- DMA with hands-on

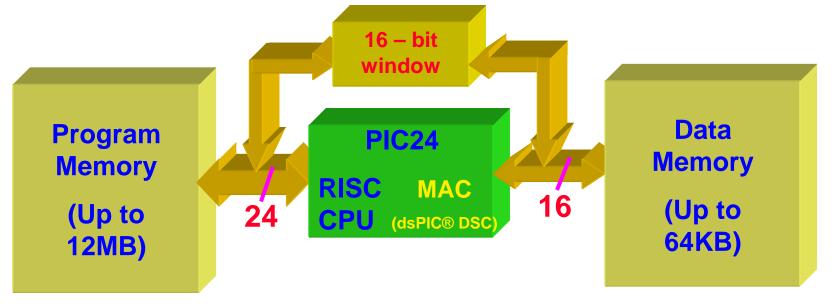

### **Harvard Architecture**

- 16-bit microcontroller

- 24-bit Instruction width

- Data Transfer Mechanism between PM and DM

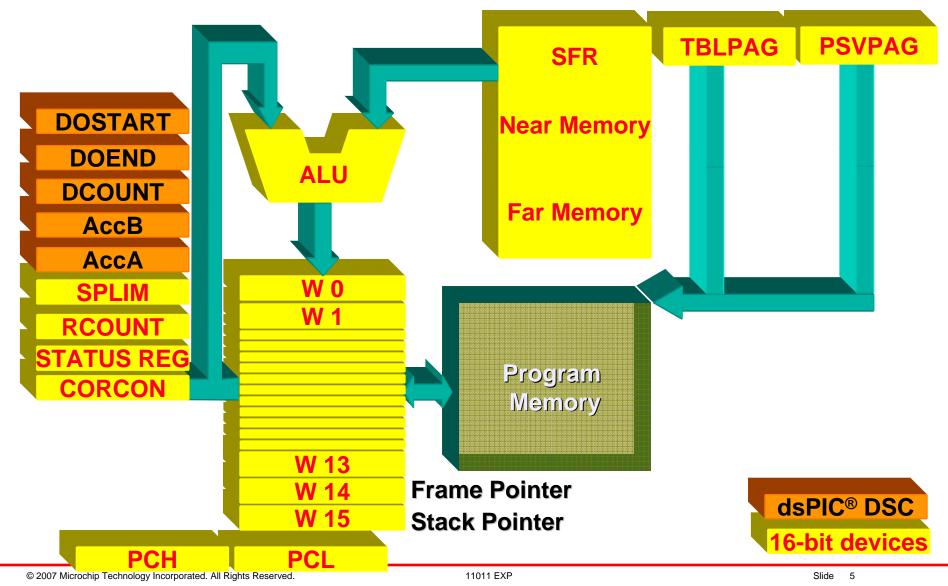

#### **16-bit Architecture** Programmers model

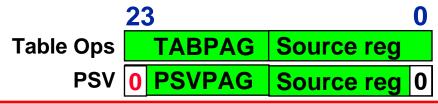

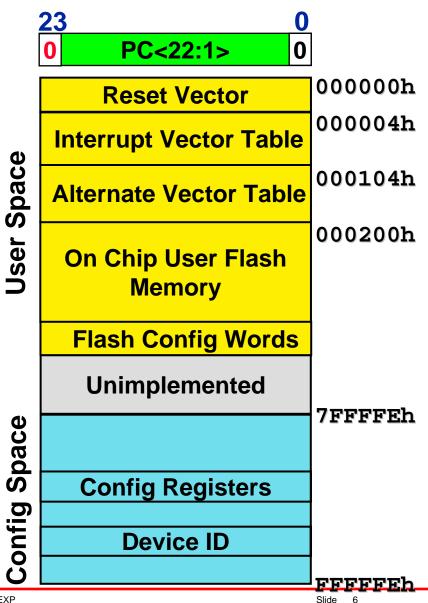

### **Program Memory**

- Maximum 12MB

- 4MB x 24-bit

- 23-bit PC (PCH & PCL)

- PC increments in words (LSB always '0')

- Reset Vector at 0

- Interrupt Vector Table from 4h to FEh

- User Code space from 200h to 7FFFEh (what ever is implemented)

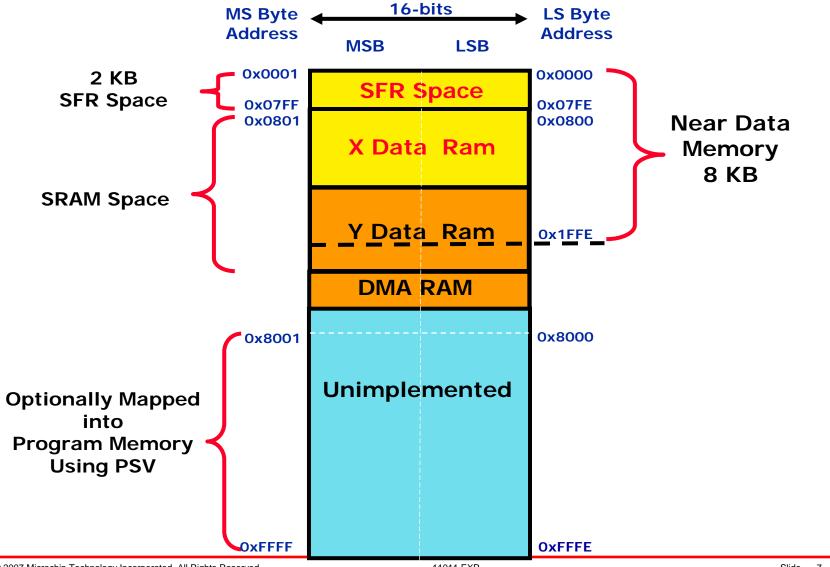

## **Data Memory Organization**

### Peripheral Pin Select (PPS)

### **Peripheral Pin Select**

### What it is...

- Pin multiplexing that allows user to select the pin out of digital functions

- Allows optimal usage of on-board peripherals

- Allows Pin Redefinition via software

### What it is not ...

- -Not a method to achieve pin compatibility

- Analog and special pad pins (e.g., PMP & I<sup>2</sup>C<sup>™</sup>) are still fixed

### **Application Example**

#### Memory

- -64K Flash

- -8K RAM

### Analog

- -2 ch ADC

- -Vref +&-

- -Comparator x 2

- Digital I/O

- -4 I/O

### Serial Channels

- I<sup>2</sup>С™

- SPI x 2

- UART x 2

- Easy... Right?

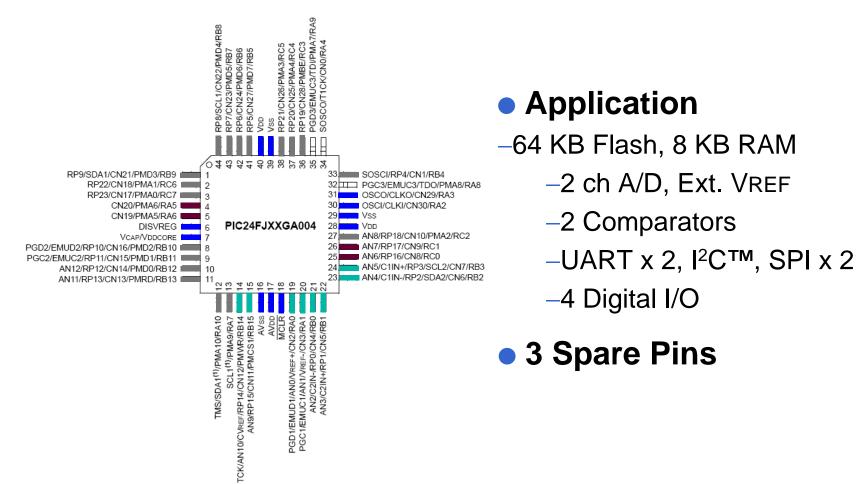

### **Application Example**

Application

- 64 KB Flash, 8 KB RAM

- 2 ch A/D, Ext. VREF

- 2 Comparators

- UART x 2, I<sup>2</sup>C<sup>™</sup>, SPI x 2

- 4 Digital I/O

### Pin multiplexing blocks functions

- UART1 and SPI1

- Comparator2 and SPI1

#### 25 spare pins

- Must use even larger pin count device

- Or write SPI in software

### Remappable Functions 16-bit MCU and dsPIC<sup>®</sup> DSC

- All SPI & UART Functions

- Timer & External Interrupt Inputs

- Input Capture & Output Compares

- Analog Comparator outputs

- PWM Fault Input pins

- Quadrature Encoder Interface Inputs

- Data Converter Interface

CAN

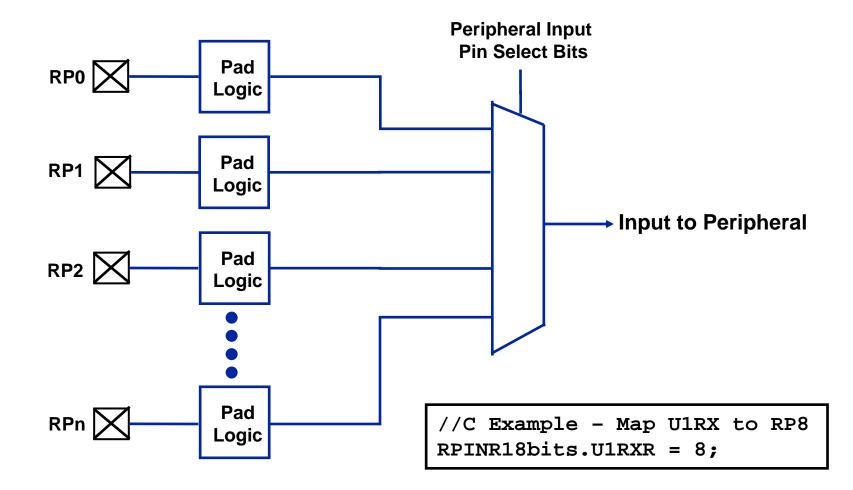

## **PPS Implementation Details**

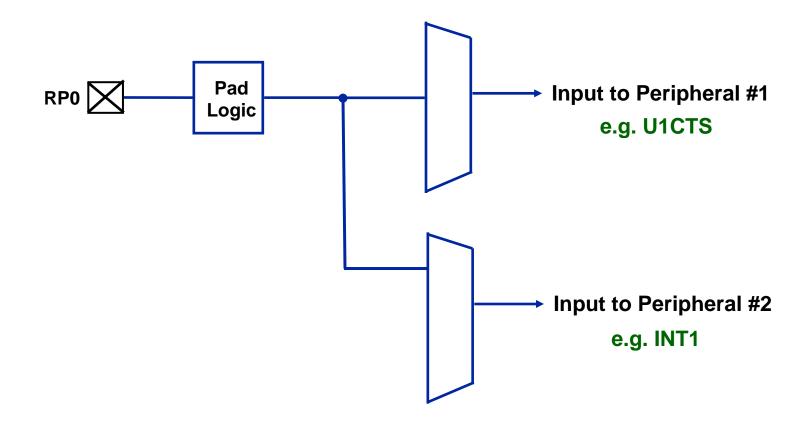

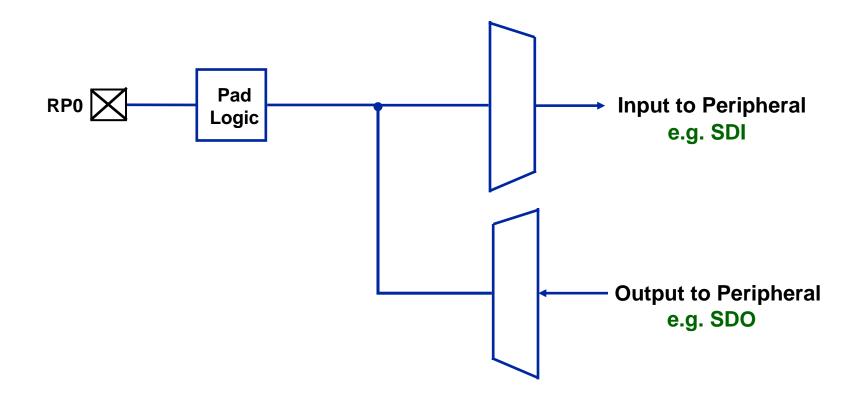

- Any function can remap to any RP pin

- Multiple functions on one pin is supported

- Inputs vs. Outputs

- Inputs assign a pin to a specific peripheral

- Outputs assign a peripheral to a specific pin

- Pinout is set in software

- Allows on-the-fly configuration or oneshot configuration

### **Remappable Inputs**

### **Remappable Inputs**

#### REGISTER 9-9: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| U-0    | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   |     | U1CTSR4 | U1CTSR3 | U1CTSR2 | U1CTSR1 | U1CTSR0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7 | -   |     |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                            |

|-----------|---------------------------------------------------------------------------------------|

| bit 12-8  | U1CTSR4:U1CTSR0: Assign UART1 Clear to Send (U1CTS) to the Corresponding RPn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                            |

| bit 4-0   | U1RXR4:U1RXR0: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits          |

|           |                                                                                       |

#### Define the location of each function used by modifying xxxxR bits in RPINRn registers

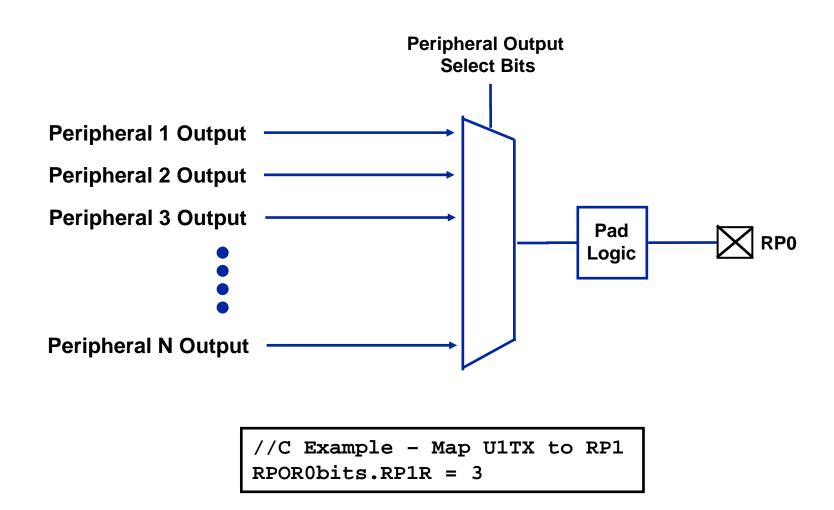

### **Remappable Outputs**

### **Remappable Outputs**

| Function             | Output Function<br>Number <sup>(1)</sup> | Output Name              |

|----------------------|------------------------------------------|--------------------------|

| NULL <sup>(2)</sup>  | 0                                        | NULL                     |

| C10UT                | 1                                        | Comparator 1 Output      |

| C2OUT                | 2                                        | Comparator 2 Output      |

| U1TX                 | 3                                        | UART1 Transmit           |

| U1RTS <sup>(3)</sup> | 4                                        | UART1 Request To Send    |

| U2TX                 | 5                                        | UART2 Transmit           |

| U2RTS <sup>(3)</sup> | 6                                        | UART2 Request To Send    |

| SDO1                 | 7                                        | SPI1 Data Output         |

| SCK1OUT              | 8                                        | SPI1 Clock Output        |

| SS10UT               | 9                                        | SPI1 Slave Select Output |

| SDO2                 | 10                                       | SPI2 Data Output         |

| SCK2OUT              | 11                                       | SPI2 Clock Output        |

| SS2OUT               | 12                                       | SPI2 Slave Select Output |

| OC1                  | 18                                       | Output Compare 1         |

| OC2                  | 19                                       | Output Compare 2         |

| OC3                  | 20                                       | Output Compare 3         |

| OC4                  | 21                                       | Output Compare 4         |

| OC5                  | 22                                       | Output Compare 5         |

### **Remappable Outputs**

#### REGISTER 9-17: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-------|-------|-------|

| —      | —   | —   | RP5R4 | RP5R3 | RP5R2 | RP5R1 | RP5R0 |

| bit 15 | -   | -   |       |       |       |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   |     | RP4R4 | RP4R3 | RP4R2 | RP4R1 | RP4R0 |

| bit 7 |     |     |       |       |       | •     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

- bit 15-13 Unimplemented: Read as '0'

- bit 12-8 **RP5R4:RP5R0:** Peripheral Output Function is Assigned to RP5 Output Pin bits (see Table 9-2 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP4R4:RP4R0:** Peripheral Output Function is Assigned to RP4 Output Pin bits (see Table 9-2 for peripheral function numbers)

#### Define the output functionality on each pin by modifying RPnR bits in RPORn registers

Visual I RTC ٢

> DSP 1/0 Por Timers

Counter

QEL **PWM** IC 0C SPI 12C UART CAN

> DCI ADC

Reset

Op Am Compara

DMA

Ext. Interf

### **Remapping Pins with VDI**

| nitializer                                                                                                          |                     |                                        |              |

|---------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------|--------------|

| s<br>S<br>Oscillator<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S | Peripheral Pin Sele | Color coding show<br>where conflicts m |              |

|                                                                                                                     | Input Function      | Pin 🔺                                  | Pin          |

|                                                                                                                     | IC5                 | RP0 (Pin 21)                           | RP0 (Pin 21) |

|                                                                                                                     | OCFA                | RP0 (Pin 21)                           | RP1 (Pin 22) |

| tor                                                                                                                 | OCFB                | RP0 (Pin 21)                           | RP2 (Pin 23) |

|                                                                                                                     | U1RX                | RP1 (Pin 22)                           | RP3 (Pin 24) |

|                                                                                                                     | U1CTS               | RP0 (Pin 21)                           | RP4 (Pin 33) |

|                                                                                                                     | U2RX                | RP0 (Pin 21)                           | RP5 (Pin 41) |

|                                                                                                                     | U2CTS               | RP0 (Pin 21)                           | RP6 (Pin 42) |

|                                                                                                                     | SDI1                | RP0 (Pin 21)                           | RP7 (Pin 43) |

|                                                                                                                     | SCK1                | RP0 (Pin 21) 🗾                         | RP8 (Pin 44) |

|                                                                                                                     |                     |                                        | ПK           |

hat pins are used and kist

ΟK

© 2007 Microchip Technology Incorporated. All Rights Reserved.

Output Function

None.

None.

U1TX

None

None.

None.

None

None

None

Cancel

? ×

٠

•

Apply

### **PPS Register Protection**

#### • HW integrity checking

– Bit flip will cause device reset

#### • I/O lock feature

RPINRn/RPORn can only be written to while the IOLOCK bit in the OSCCON register = 0; once the IOLOCK is set, the registers cannot be written

#### IOLOCK Protection

- The state of the IOLOCK bit can only be changed with an unlocking sequence

- Protection selectable by configuration bit

## **Pin Function Priority**

### • Peripheral priorities:

- 1. Analog Functions

- 2. **PPS Outputs**

- 3. **PPS Inputs**

- 4. Fixed Digital Peripheral Outputs

- 5. Fixed Digital Peripheral Inputs

ANx, Vref+/-

UART TX, SDO, OC

UART RX, SDI, IC

**I**<sup>2</sup>**C**<sup>™</sup>, **PMP**

I<sup>2</sup>C, PMP

## Initializing a PPS Application

- 1. Design Decision: Static or Dynamic RPn assignment?

- Set IOL1WAY config bit accordingly

- 2. Initialize the pinout by mapping the RPn pins to the desired peripheral input/output functions

- Map RPn pin(s)  $\rightarrow$  Peripheral Input Function(s)

- Map Peripheral Output Function(s)→RPn pin(s)

- Lock the RPn SFRs using 'lock' sequence

- **3. Configure Peripherals**

- 4. Enable Interrupts (if required)

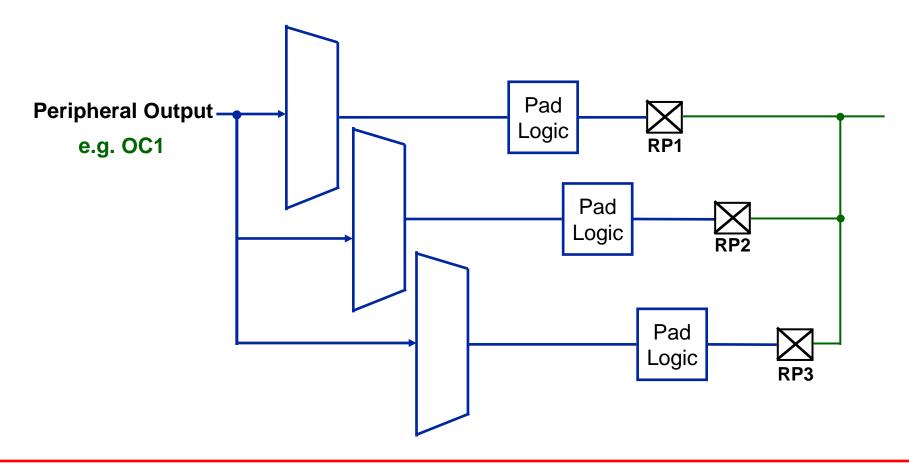

### **Cool Byproducts**

Increase drive strength by outputting same peripheral on multiple pins

### **Cool Byproducts**

Connect one signal to multiple peripheral inputs

### **Cool Byproducts**

Connect peripheral output to another input (Loopback) for debugging

### **Application Example Revisited**

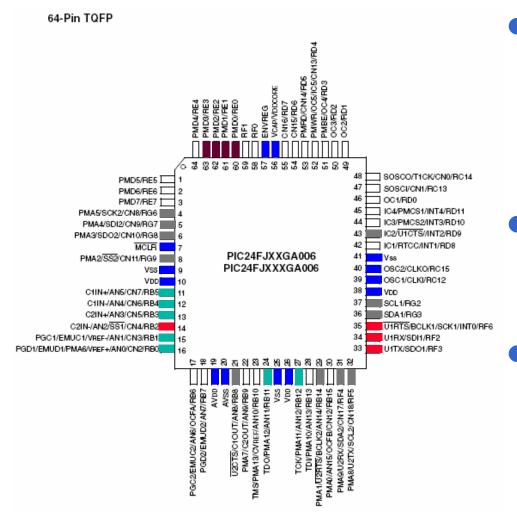

44-Pin TQFP

#### Smaller packages, simplified design and lower cost!

## Let's go Hands on

### Lab 1 Peripheral Pin Select

### Lab 1: PPS

#### • Goal:

#### Configure simple UART echo to HyperTerminal using PIC24FJ64GA004 on Explorer16

See "PIC24FJ64GA004 PIM Infosheet 51663a.pdf" to see how the 100-pin PIM socket maps to the 44-pin PIC24FJ64 device

### Lab 1 – PIM Swap

- Lab 1 uses the PIC24FJ64GA004 PIM

- To swap the processor:

- Disconnect Explorer 16 power and ICD2 connections

- Remove PIC24FJ128GA010 PIM

- Place PIC24FJ64GA004 PIM on board, making sure to properly align the notched corner

- Reconnect Power and ICD2

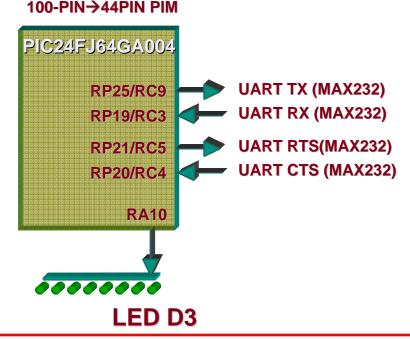

## Lab 1 – Required Mapping

### • Desired peripheral input functions:

- U2RX  $\rightarrow$  RP19 Input Function

- − U2CTS  $\rightarrow$  RP20 Input Function

### Desired peripheral output functions

- − RP25  $\rightarrow$  U2TX

- − RP21  $\rightarrow$  U2RTS

- LED/Switch I/O:

- RA10→LED D3

### Lab 1: PPS

#### • Goal:

#### Configure simple UART echo to HyperTerminal using PIC24FJ64GA004 on Explorer16

### • To Do:

-Read the handout - fill in the code sections

### Expected Result:

Typed characters echoed back to Hyperterminal (LED D3 flashes for each keystroke)

$\ensuremath{\textcircled{\sc 0}}$  2007 Microchip Technology Incorporated. All Rights Reserved.

### Parallel Master Port (PMP)

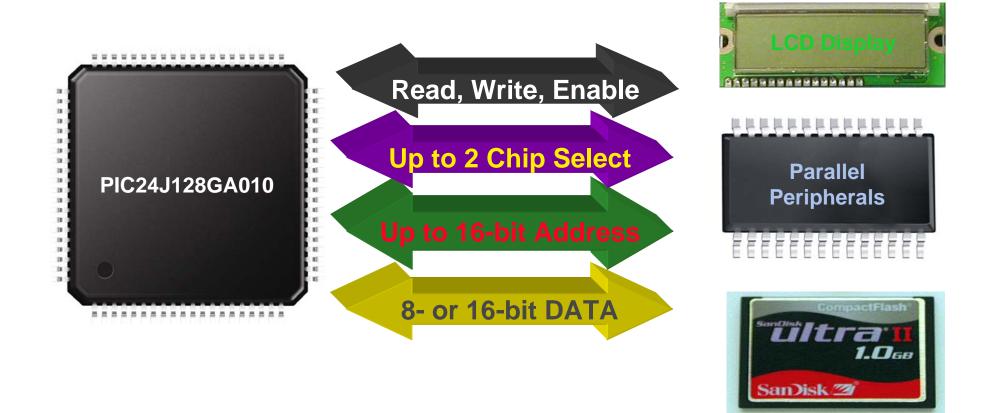

### Parallel Master Port – PMP

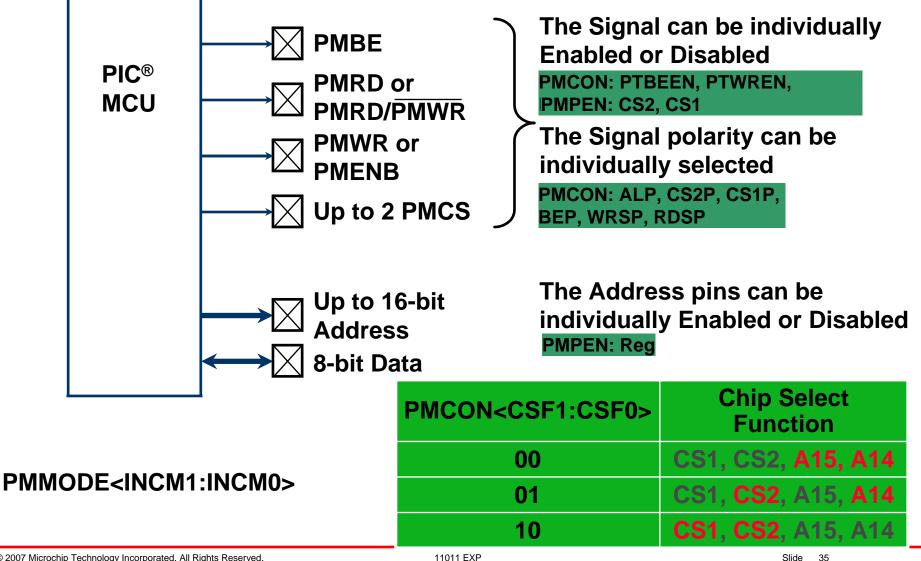

# PMP Configuration: Control Signals

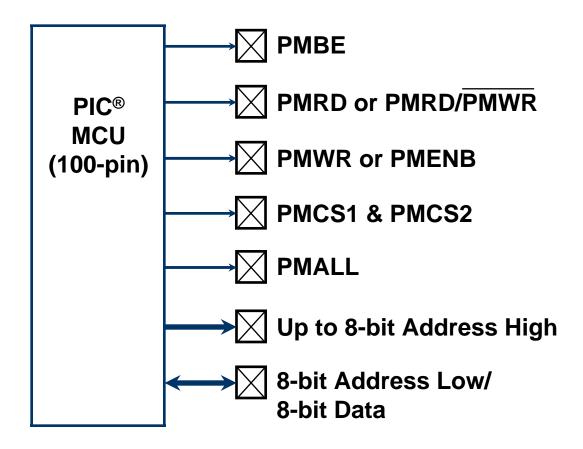

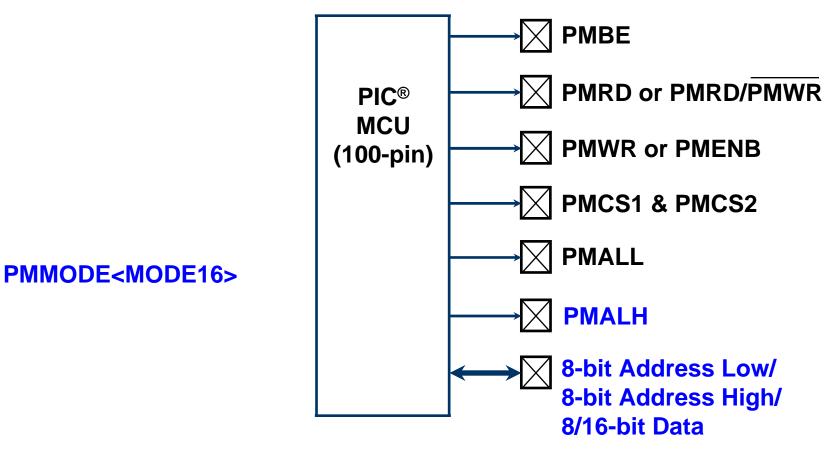

#### **PMP Configuration: Multiplexed Data Bus**

#### PMCON<ADRMUX1:ADRMUX0> = 01

### **PMP Configuration: Multiplexed Data Bus**

#### PMCON<ADRMUX1:ADRMUX0> = 10

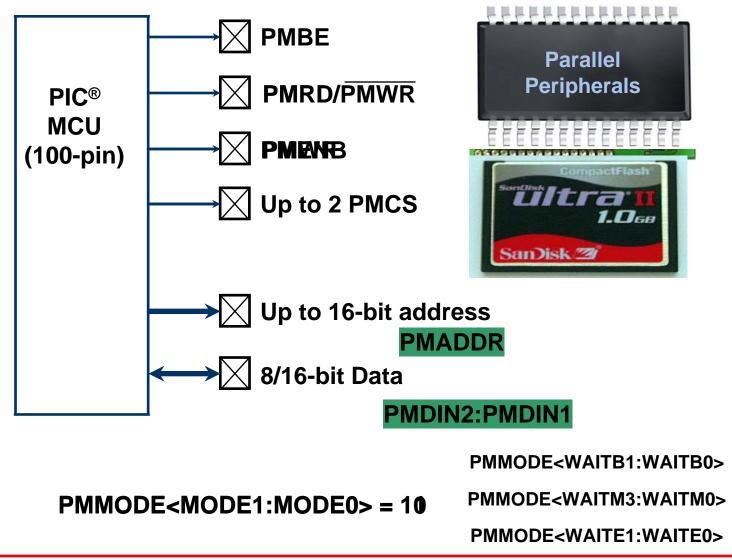

### **PMP Configuration: Standard Peripherals**

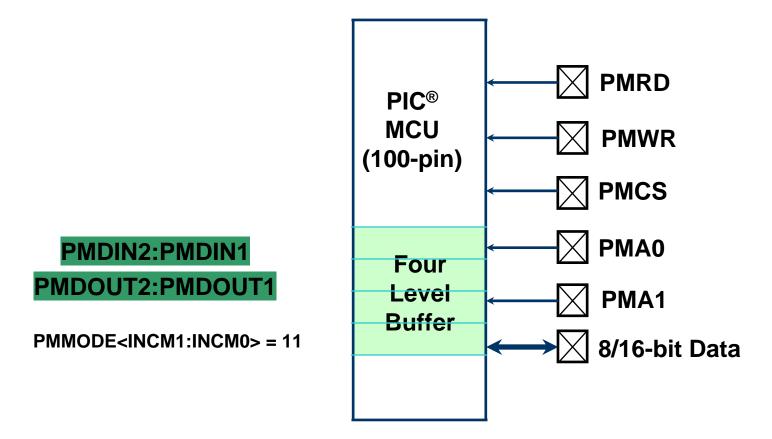

### PMP Configuration: Slave Mode

#### PMMODE<MODE1:MODE0> = 00

# **Optional Lab** The Parallel Master Port

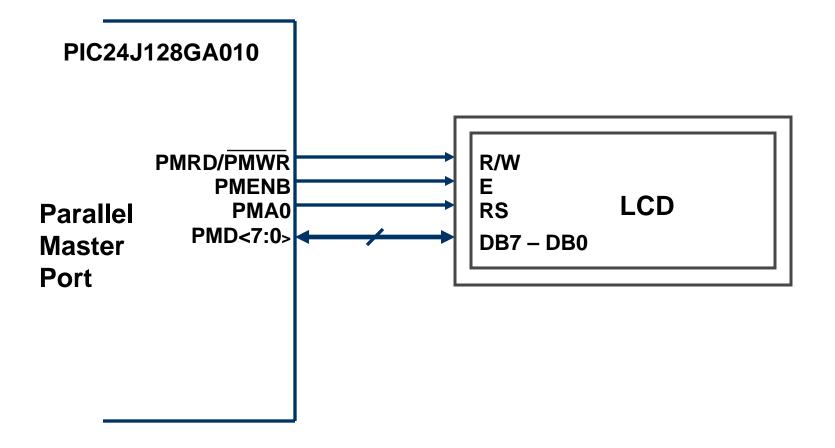

# **Opt. Lab – LCD on the PMP**

# **Opt. Lab – LCD on the PMP**

# Setup PMP for an LCD, think about:

- Signals

- Polarity

- LCD interface

- Addressing

- Timing

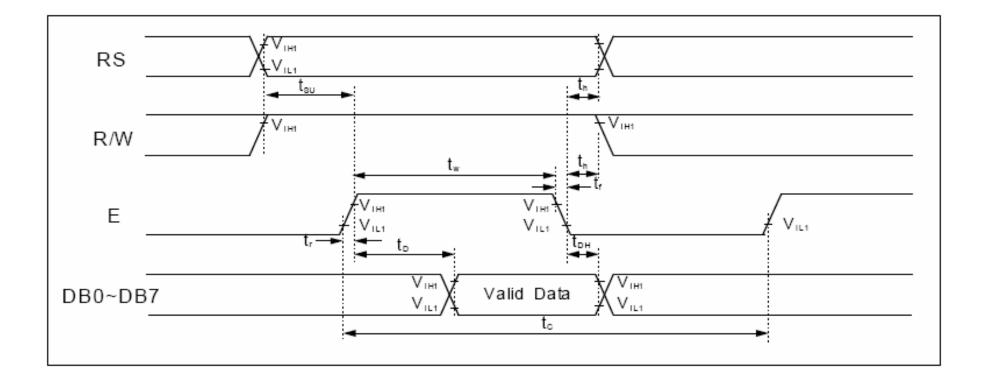

Write is active low. But remember! PMP signal we are using is PMRD/PMWR, so the pin needs to be configured as active high. RS R/W Е Valid Data DB0~DB7 Enable is active High.

# **Opt. Lab – LCD Read Timing**

# **Opt. Lab – LCD Commands**

| Instruction                   |    |     |     | Inst | ructi | on C | ode |     |     |     | Description                                                                                                                                  | Execution<br>time (fosc= |

|-------------------------------|----|-----|-----|------|-------|------|-----|-----|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| matuction                     | RS | R/W | DB7 | DB6  | DB5   | DB4  | DB3 | DB2 | DB1 | DB0 | Description                                                                                                                                  | 270 kHz)                 |

| Clear<br>Display              | 0  | 0   | 0   | 0    | 0     | 0    | 0   | 0   | 0   | 1   | Write "20H" to DDRAM and set<br>DDRAM address to "00H" from AC                                                                               | 1.53 ms                  |

| Return<br>Home                | 0  | 0   | 0   | 0    | 0     | 0    | 0   | 0   | 1   | -   | Set DDRAM address to '00H"<br>from AC and return cursor to its<br>original position if shifted.<br>The contents of DDRAM are not<br>changed. | 1.53 ms                  |

| Entry Mode<br>Set             | 0  | 0   | 0   | 0    | 0     | 0    | 0   | 1   | I/D | SH  | Assign cursor moving direction<br>and enable the shift of entire display.                                                                    | 39 µs                    |

| Display ON/<br>OFF Control    |    | 0   | 0   | 0    | 0     | 0    | 1   | D   | с   | в   | Set display(D), cursor(C),<br>and blinking of cursor(B) on/off<br>control bit.                                                               | 39 µs                    |

| Cursor or<br>Display<br>Shift | 0  | 0   | 0   | 0    | 0     | 1    | S/C | R/L | -   | -   | Set cursor moving and display<br>shift control bit, and the direction,<br>without changing of DDRAM data.                                    | 39 µs                    |

### Opt. Lab – LCD Commands (cont)

| Function Set                     | 0 | 0 | 0  | 0   | 1   | DL  | N   | F   | -   | -   | Set interface data length (DL:<br>8-bit/4-bit), numbers of display line<br>(N: 2-line/1-line) and, display<br>font type (F:5×11dots/5×8 dots) | 39 µs         |

|----------------------------------|---|---|----|-----|-----|-----|-----|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Set CGRAM<br>Address             | 0 | 0 | 0  | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 | Set CGRAM address in address<br>counter.                                                                                                      | 39 µs         |

| Set DDRAM<br>Address             | 0 | 0 | 1  | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 | Set DDRAM address in address<br>counter.                                                                                                      | 39 µs         |

| Read Busy<br>Flag and<br>Address | 0 | 1 | BF | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 | Whether during internal operation<br>or not can be known by reading BF.<br>The contents of address counter<br>can also be read.               | 0 µs          |

| Write Data to<br>RAM             | 1 | 0 | D7 | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Write data into internal RAM<br>(DDRAM/CGRAM).                                                                                                | 43 μ <b>s</b> |

| Read Data<br>from RAM            | 1 | 1 | D7 | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Read data from internal RAM<br>(DDRAM/CGRAM).                                                                                                 | 43 μ <b>s</b> |

# **Opt. Lab – LCD on the PMP**

# **Opt. Lab – LCD on the PMP**

### Goals

- Learn about the Parallel Master Port (PMP)

- Refresh knowledge of the common LCD interface

- Do some coding for PIC24

- Lab

- Add setup code to initialize the PMP

- Put your name on the display

# Real-time Clock & Calendar (RTCC)

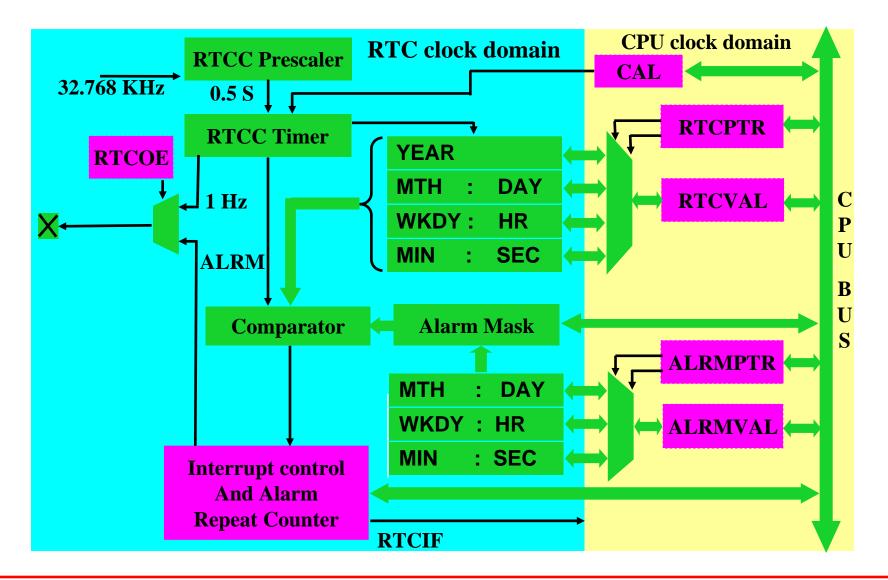

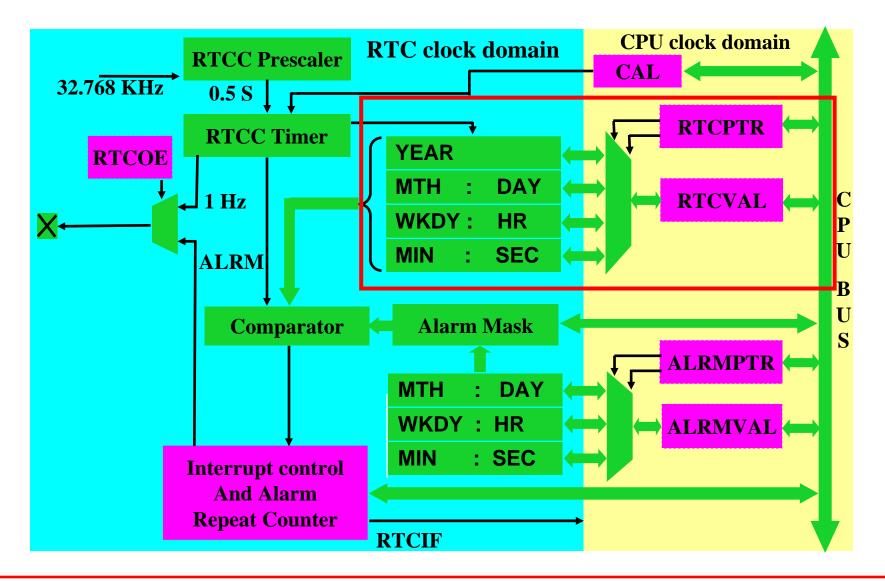

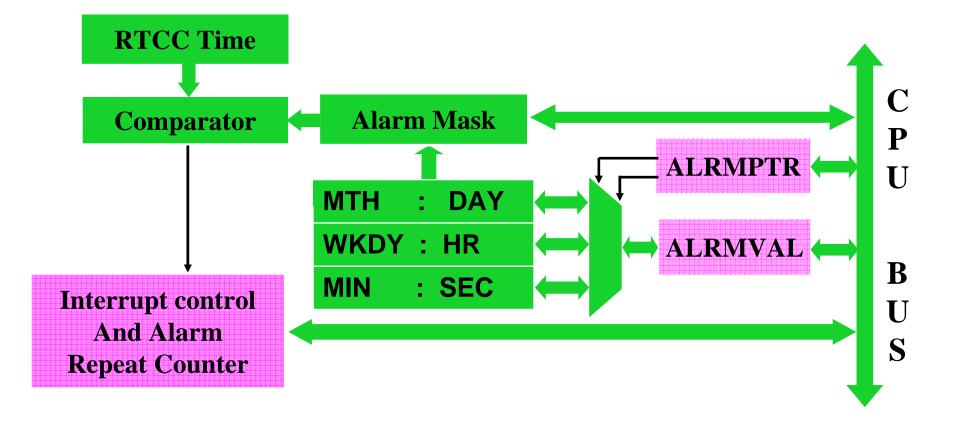

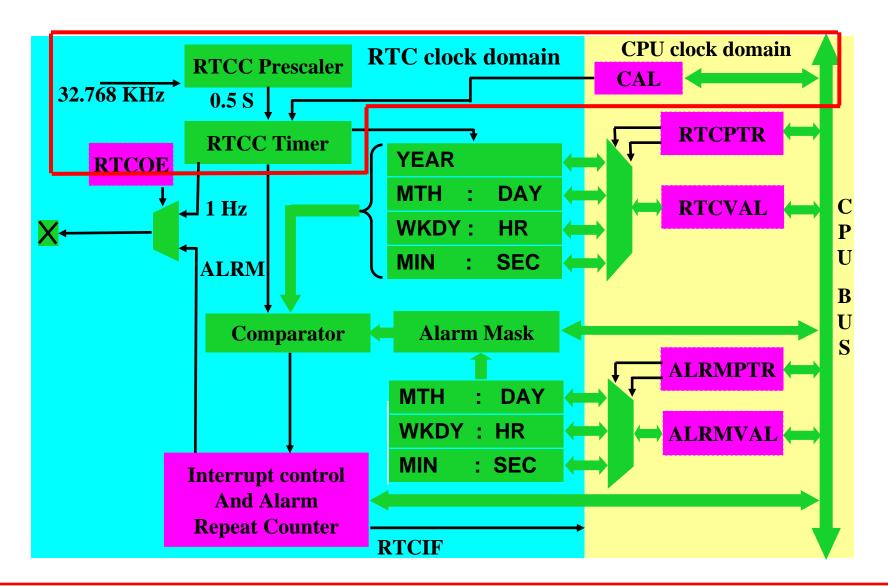

# **RTCC: Block Diagram**

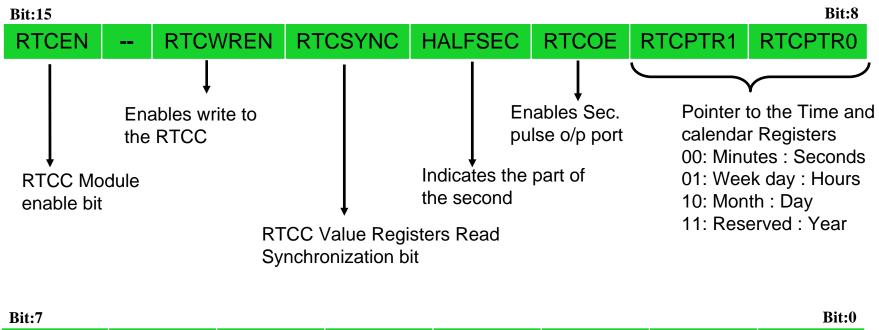

# **RTCC: Configuration**

#### **RCFGCAL: RTCC Calibration and Configuration register**

CAL7 CAL6 CAL5 CAL4 CAL3 CAL2 CAL1 CAL0

Crystal offset calibration bits (RTCC Drift calibration bits)

$\ensuremath{\textcircled{\sc 0}}$  2007 Microchip Technology Incorporated. All Rights Reserved.

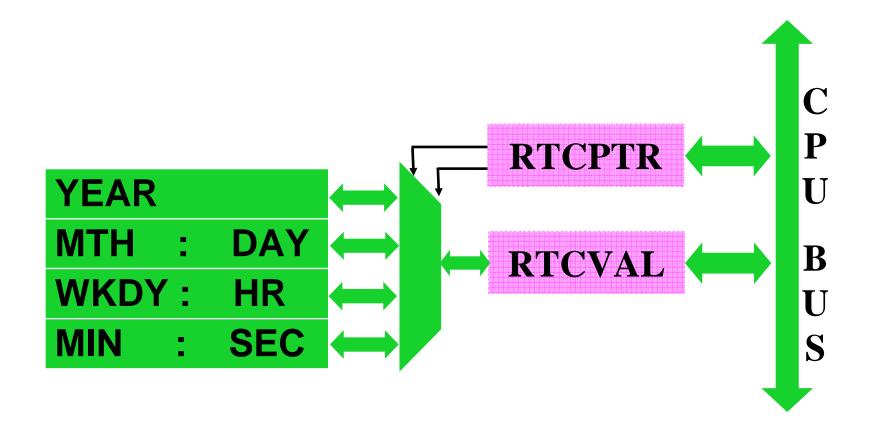

# **RTCC: Block Diagram**

**RTCVAL: RTCC Value Register**

- Pointer bits, RTCPTR<1:0>, indicate which register is read from and written to RTCVAL

- RTCPTR<1:0> auto decrements when RTCVAL<15:8> is read or written until it reaches '00'

| RTCPTR<1:0> | RTCVAL<15:8> | RTCVAL<7:0> |

|-------------|--------------|-------------|

| 11          |              | YEAR        |

| 10          | MONTH        | DAY         |

| 01          | WEEKDAY      | HOURS       |

| 00          | MINUTES      | SECONDS     |

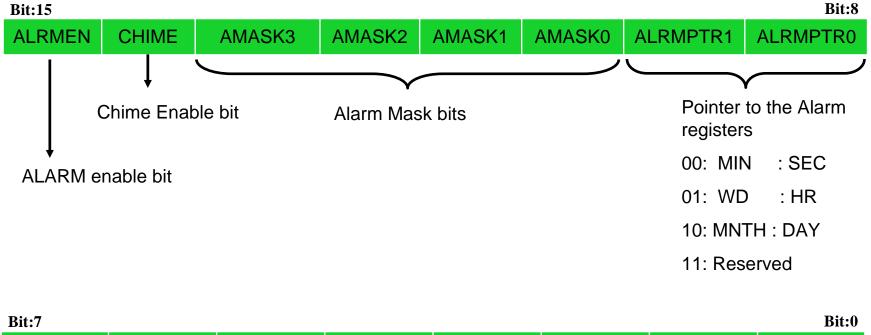

#### **ALRMVAL: RTCC Alarm Value Register**

- Pointer bits, ALRMPTR<1:0> indicate what is read from and written to ALRMVAL

- ALRMPTR<1:0> auto decrements when ALRMVAL<15:8> is read or written until it reaches '00'

| ALRMPTR<1:0> | ALRMVAL<15:8> | ALRMVAL<7:0> |

|--------------|---------------|--------------|

| 11           |               |              |

| 10           | ALRMMNTH      | ALRMDAY      |

| 01           | ALRMWD        | ALRMHR       |

| 00           | ALRMMIN       | ALRMSEC      |

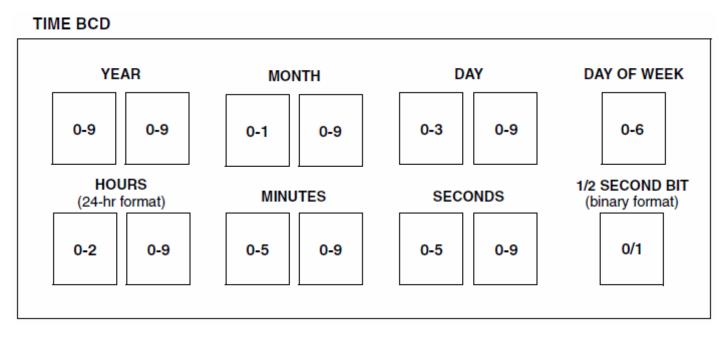

#### RTCVAL and ALRMVAL registers use BCD format

#### In BCD, each nibble (4 bits) of a word encodes a number from 0-9

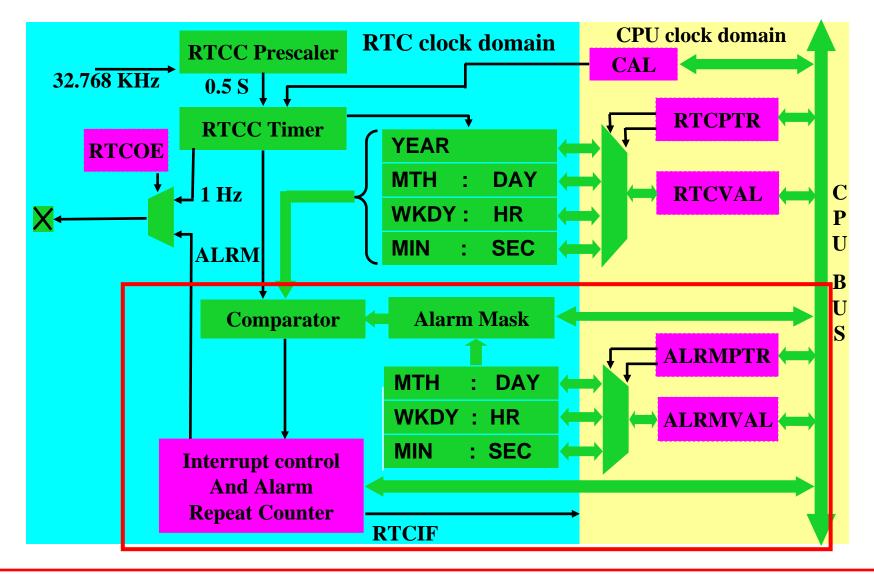

# **RTCC: Block Diagram**

**RTCC: Alarm**

# **RTCC: Configuration**

#### ALCFGRPT: RTCC Calibration and Configuration register

| ARPT7 | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|-------|-------|-------|-------|-------|-------|-------|-------|

Alarm Repeat Counter Value bits (Repeat count  $= 2^n$ )

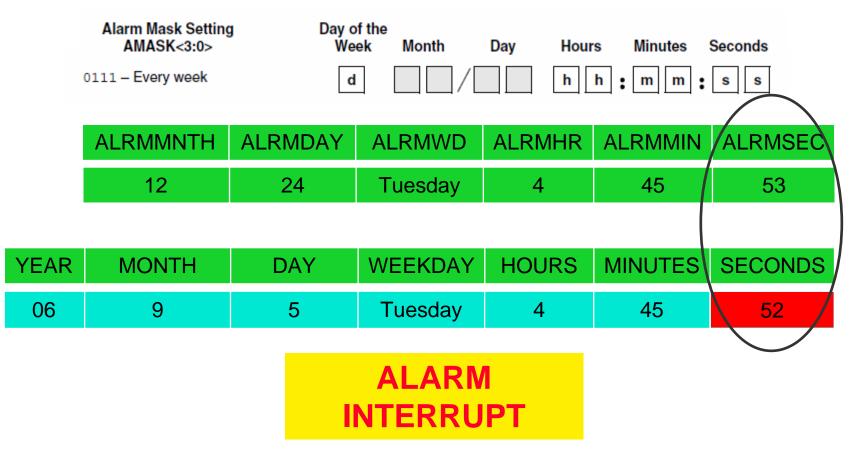

# **RTCC: Alarm**

#### AMASK<3:0> controls which registers of ALRMVAL and RTCVAL are compared to generate an alarm

| Alarm Mask Setting<br>AMASK<3:0>                          | Day of the<br>Week | Month Day | Hours Minutes Seconds  |  |  |  |  |  |

|-----------------------------------------------------------|--------------------|-----------|------------------------|--|--|--|--|--|

| 0000 – Every half second<br>0001 – Every second           |                    |           |                        |  |  |  |  |  |

| 0010 - Every 10 seconds                                   |                    |           |                        |  |  |  |  |  |

| 0011 – Every minute                                       |                    |           | ::::                   |  |  |  |  |  |

| 0100 – Every 10 minutes                                   |                    |           | ;m;\$\$\$              |  |  |  |  |  |

| 0101 – Every hour                                         |                    |           | ; m m ; s s            |  |  |  |  |  |

| 0110 – Every day                                          |                    |           | h h <b>; m m ; s s</b> |  |  |  |  |  |

| 0111 – Every week                                         | d                  |           | h h ; m m ; s s        |  |  |  |  |  |

| 1000 – Every month                                        |                    | /d d      | h h ; m m ; \$ \$      |  |  |  |  |  |

| 1001 – Every year <sup>(1)</sup>                          |                    | m m / d d | hh ; mm ; s s          |  |  |  |  |  |

| Note 1: Annually, except when configured for February 29. |                    |           |                        |  |  |  |  |  |

# **RTCC: Alarm**

# Chime allows ARPT to rollover from 00 to FF Alarms can be repeated indefinitely

# **RTCC: Block Diagram**

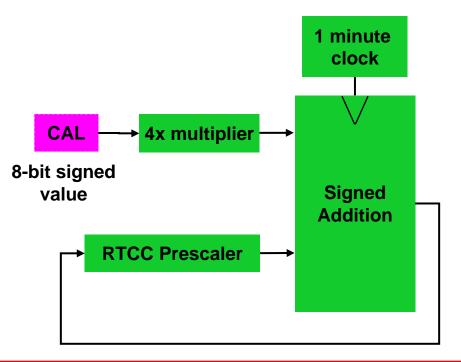

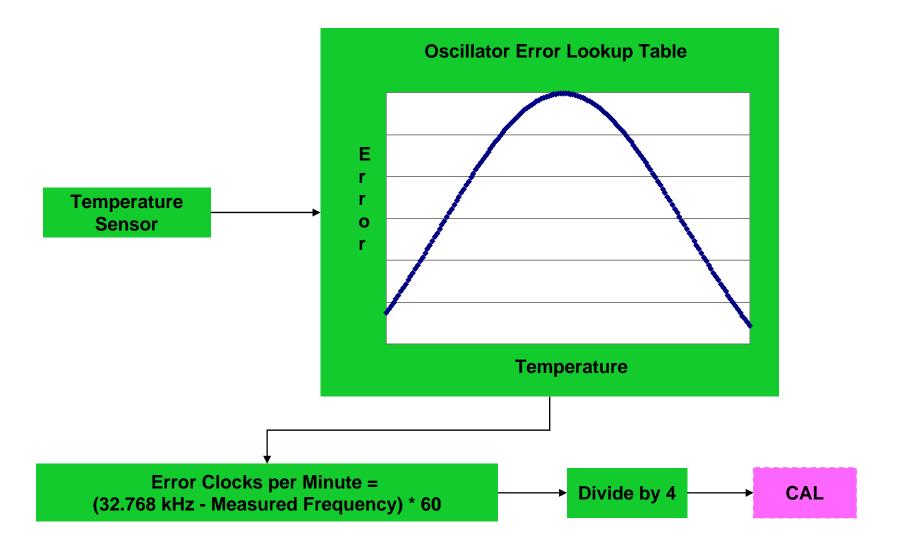

# **RTCC: Clock Calibration**

# **RTCC: Clock Calibration**

Calibrating the RTCC allows for accuracy with error less than 3 seconds per month

### **RTCC: Temperature Compensation**

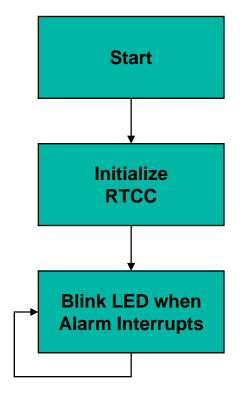

# Lab 2

# Real-time Clock and Calendar

### Lab 2 – RTCC

# Lab 2 – RTCC

### Goals

- Learn about the Real-Time Clock and Calendar (RTCC)

- Do some more coding for PIC24

- Three parts to this lab

- Add code to unlock RTCC registers (rtcc.c)

- Add code to set the time (rtcc.c)

- Add code to set an alarm (rtcc.c)

### Programmable Cyclic Redundancy Check Generator (CRC)

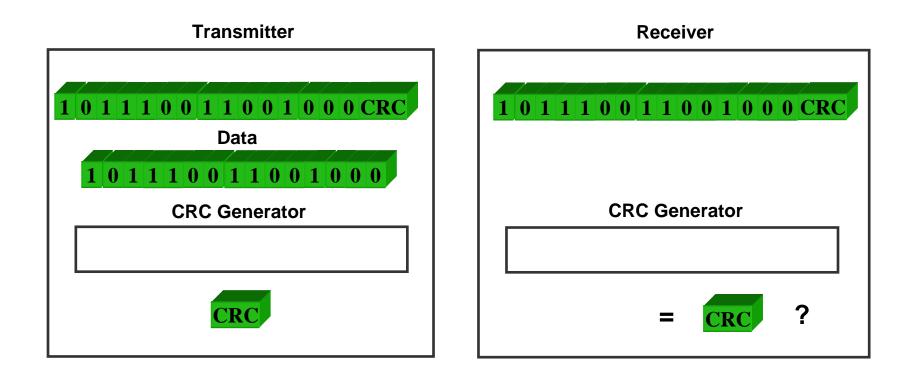

# What Is CRC?

- CRC Cyclic Redundancy Check

- CRC provides a simple and powerful method for the detection of errors in memory and communications

- CRC is a technique to detect errors but not for correcting errors

# **CRC Checksum**

- The CRC Checksum is appended to the end of the data

- The receiver runs the data through a CRC Generator and compares the result with the received CRC checksum

# **CRC Messages**

- The CRC method treats the data as a polynomial

- For example, if data is 11100101

- Data: 1 1 1 0 0 1 0 1

- Poly: x7 x6 x5 x4 x3 x2 x 1

- So the data polynomial will be

x7+x6+x5+x2+1

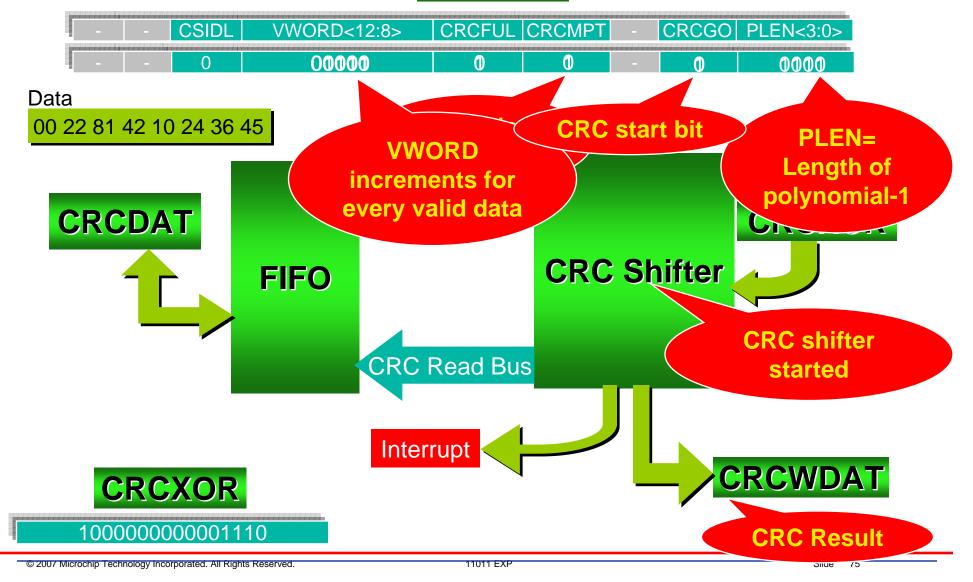

## Configuring The CRC Generator Registers

## • Generator Polynomial Example

- Polynomial =  $x^{16} + x^{15} + x^3 + x^2 + x + 1$

- Polynomial Length (PLEN) is the highest order term minus one (i.e. 15)

- CRCXOR Register is configured by setting a 1 for polynomial terms between [15:1] (i.e. 0x800E)

x<sup>15</sup> x<sup>14</sup> x<sup>13</sup> x<sup>12</sup> x<sup>11</sup> x<sup>10</sup> x<sup>9</sup> x<sup>8</sup> x<sup>7</sup> x<sup>6</sup> x<sup>5</sup> x<sup>4</sup> x<sup>3</sup> x<sup>2</sup> x<sup>1</sup> N/A

0 0 0 0 0 0 0 0 0 0 0 1 1 1 0

# **Programmable CRC Generator**

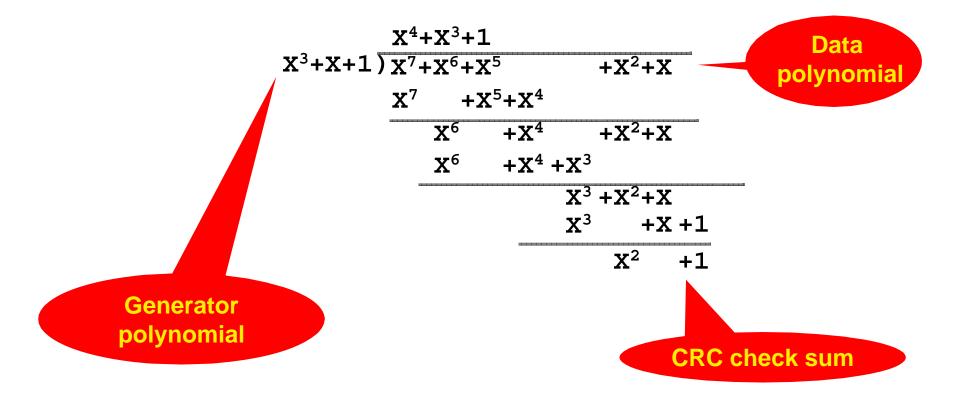

- For example,

- Assume data polynomial to be x<sup>7</sup>+x<sup>6</sup>+x<sup>5</sup>+x<sup>2</sup>+x

- Assume a generator polynomial to be  $x^3+x+1$

#### CRCCON

## Lab 3 Programmable CRC Generator

$\ensuremath{\textcircled{\sc c}}$  2007 Microchip Technology Incorporated. All Rights Reserved.

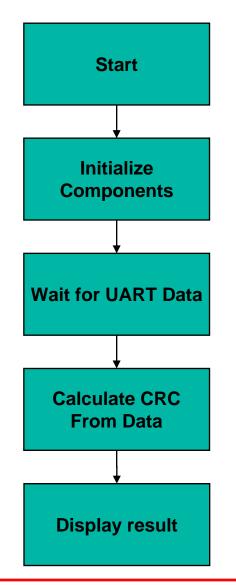

# Lab 3 CRC

# Lab 3 – CRC

## Goals

- Learn about the Programmable CRC Generator

- Do some more coding for PIC24

- Three parts to this lab

- Add code to configure the CRC generator for the polynomial  $x^{16} + x^{15} + x^2 + 1$  (main.c)

- Add code to start CRC generator (main.c)

- Check results of CRC generation and verification on LCD Display

# DMA

## **Direct Memory Access**

© 2007 Microchip Technology Incorporated. All Rights Reserved.

11011 EXP

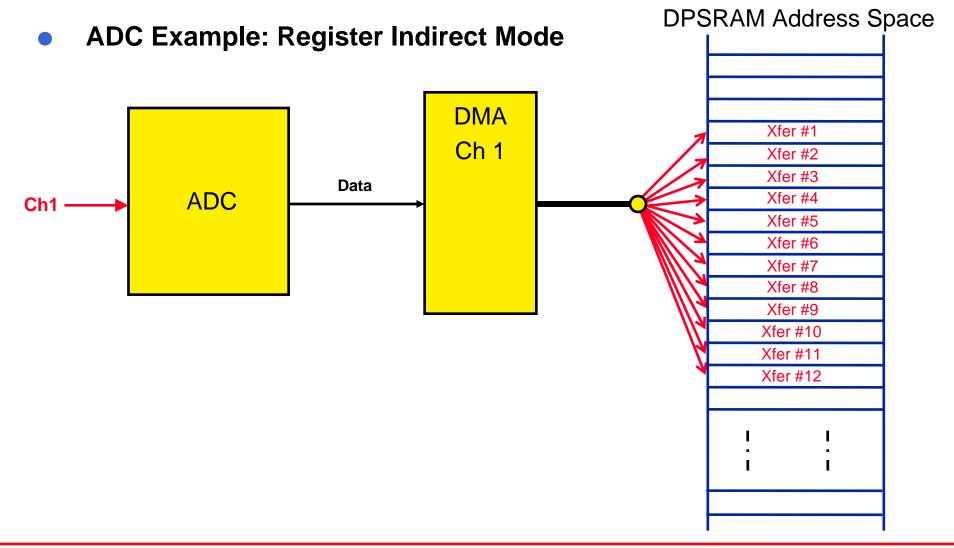

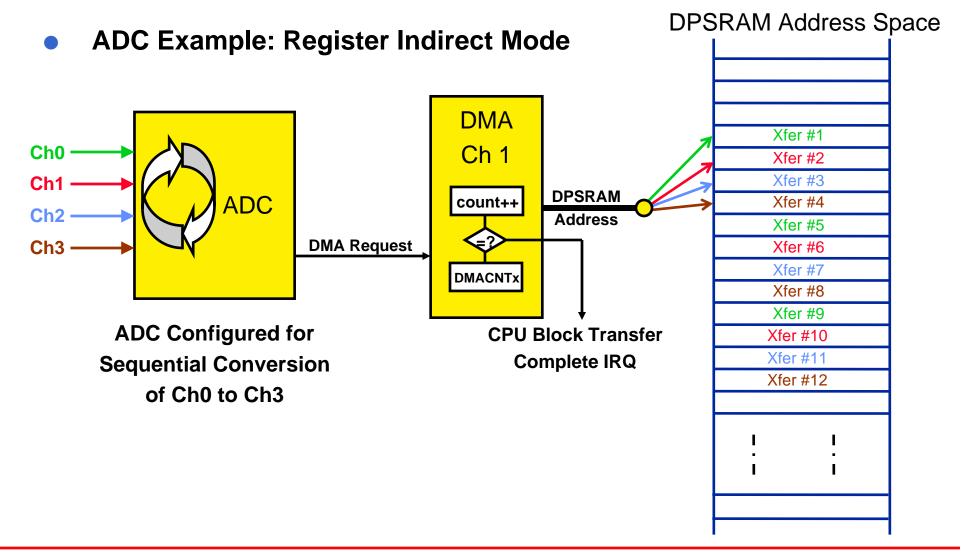

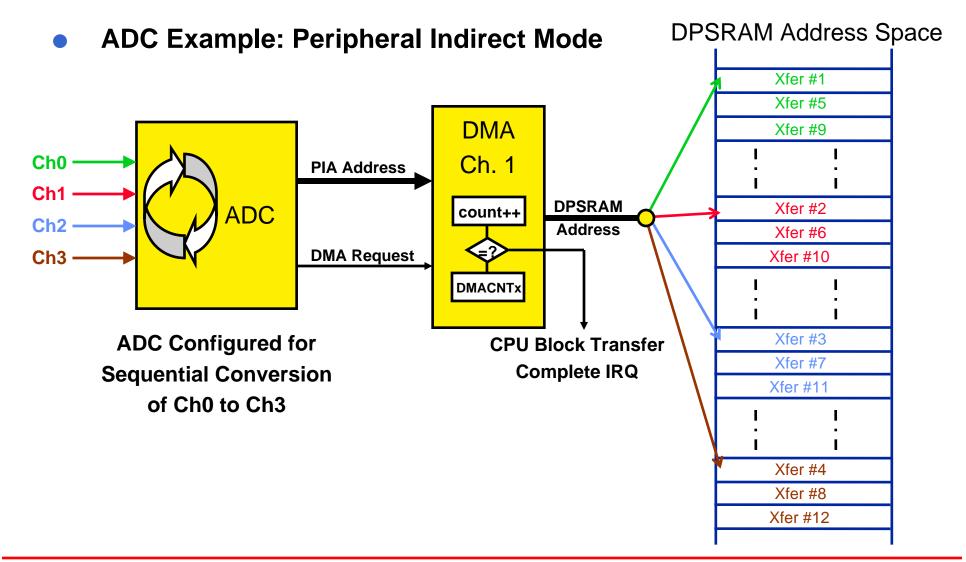

## **DMA Example: ADC**

# **DMA Features**

- 8 DMA channels

- Register indirect with post increment addressing mode

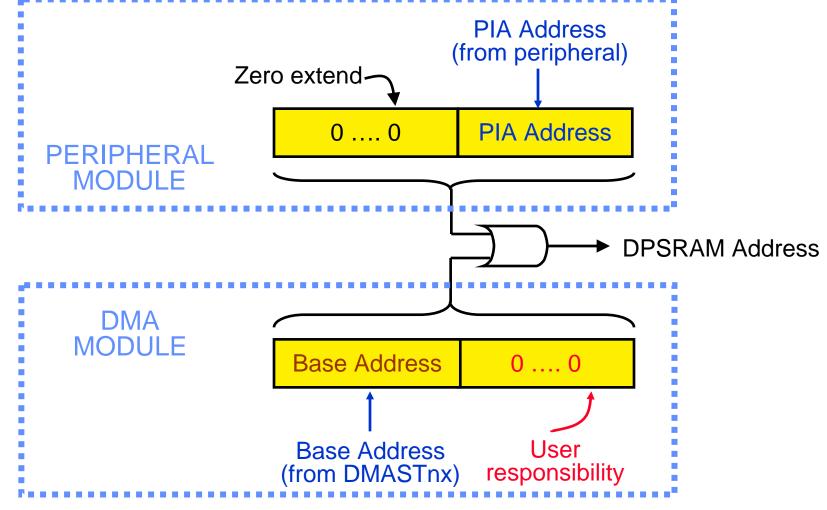

- Peripheral indirect addressing mode

- Peripheral generates destination address

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- Fixed priority channel arbitration

- Manual or Automatic transfers

- One-shot or Auto-Repeat transfers

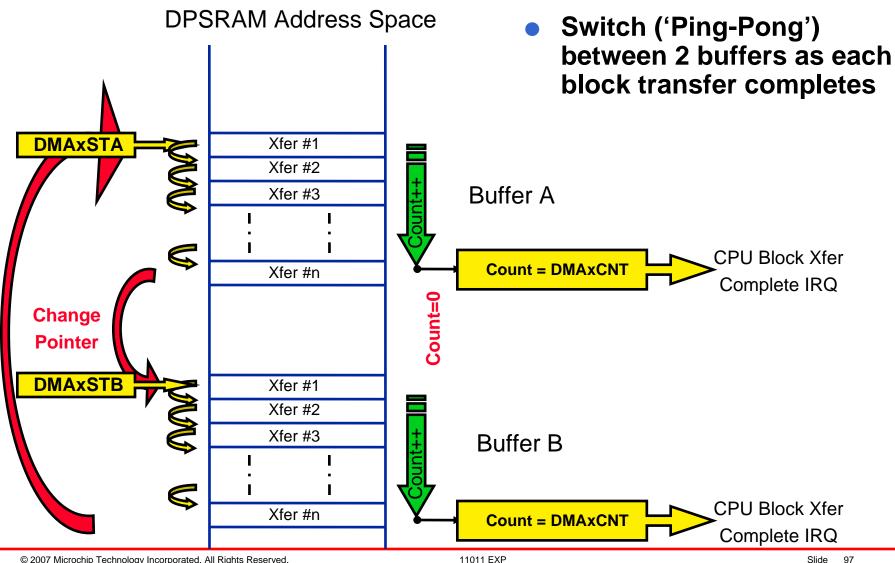

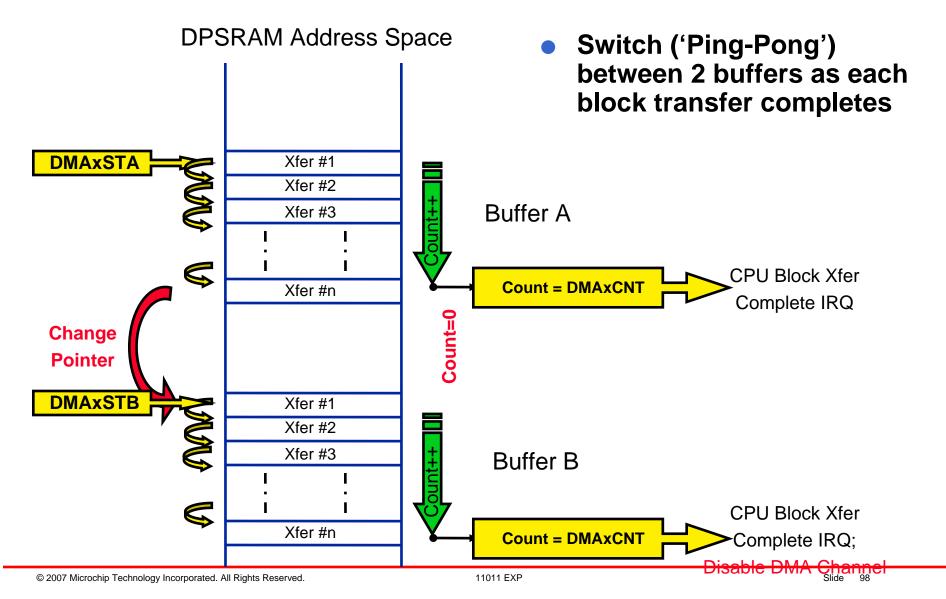

- 'Ping-pong' mode

- Automatic switch between two buffers

- DMA request for each channel can be selected from any supported interrupt sources

- Debug support features

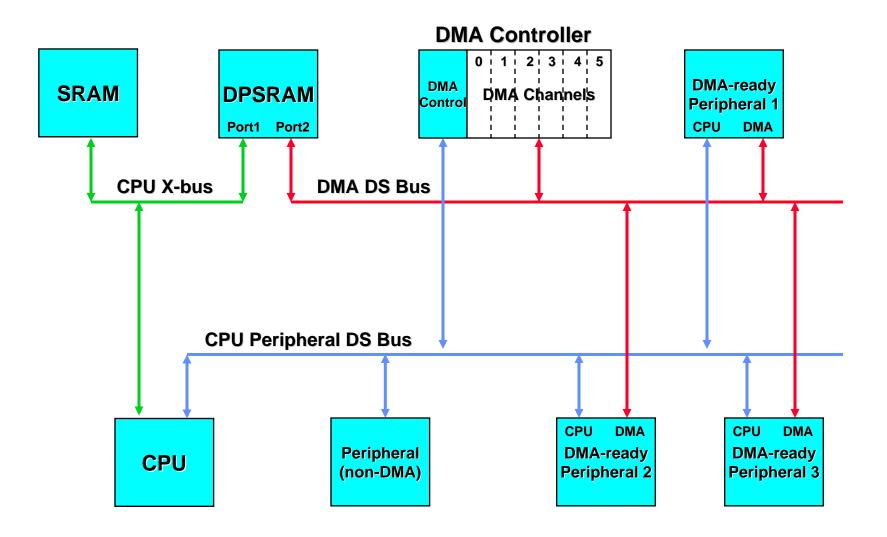

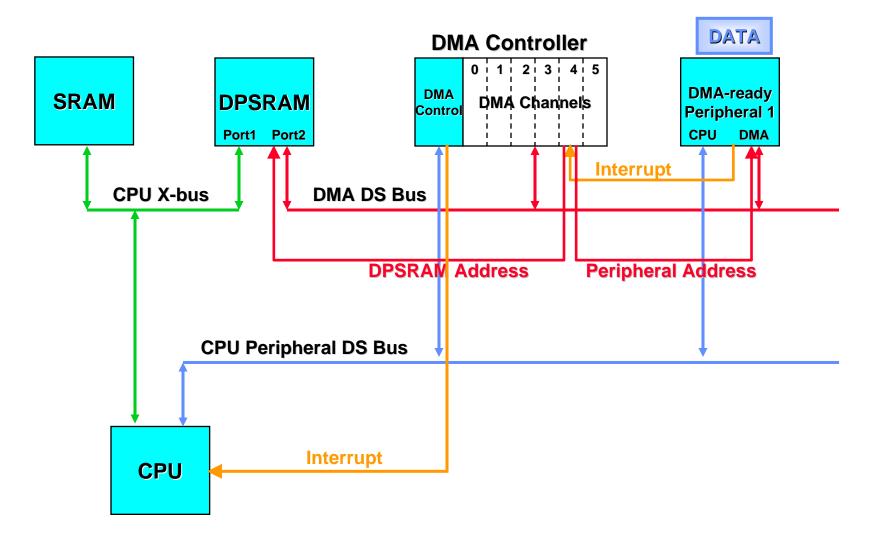

## DMA Controller Block Diagram

## DMA Controller Operation

# **DMA Support**

#### • Supported 16-bit Families

- PIC24H

- dsPIC33F

#### Supported 16-bit Peripherals

- ECAN<sup>™</sup> Module

- Data Converter Interface (DCI)

- 10-bit/12-bit A/D Converter

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

#### • DMA Request Support Only

- Timers

- External Interrupts

# **Enabling DMA Operation**

- **1.** Associate DMA channel with peripheral

- 2. Configure DMA capable peripheral

- **3.** Initialize DPSRAM data start addresses

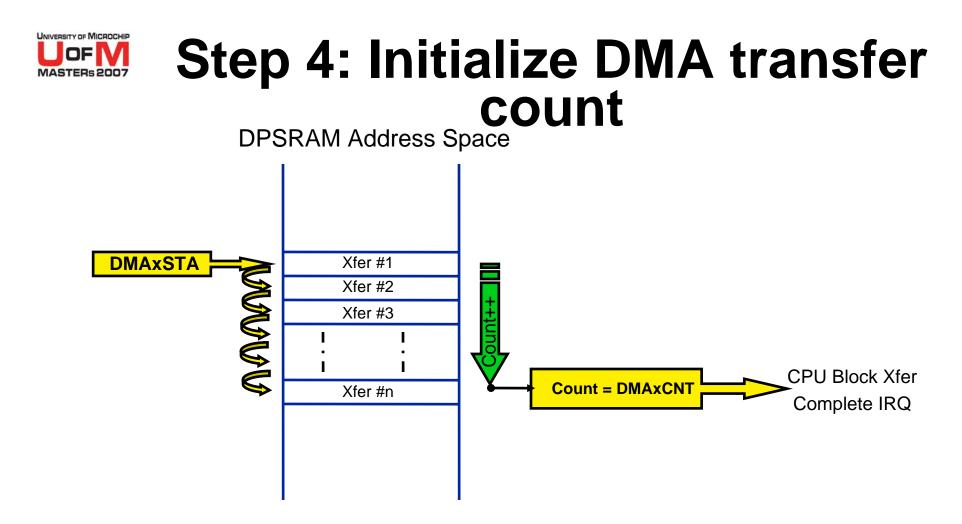

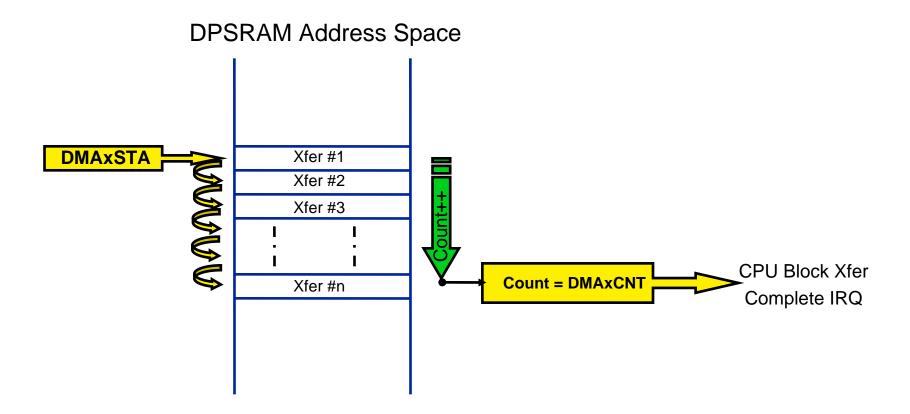

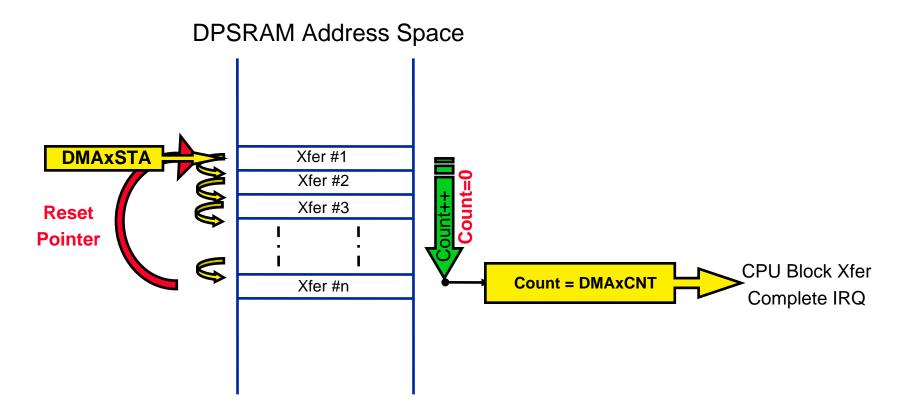

- 4. Initialize DMA transfer count

- 5. Select appropriate addressing and operating modes

# Step 1: Associate DMA and Peripheral

- Associate peripheral IRQ with DMA via DMAxREQ

- Provide peripheral read/write address via DMAxPAD

Example: Associate DMA Channel 0 and 1 with UART2 Transmitter and Receiver respectively

```

DMAOREQbits.IRQSEL = 0x1F;

DMAOPAD = (volatile unsigned int) &U2TXREG;

DMAOREQbits.IRQSEL = 0x1E;

DMAOPAD = (volatile unsigned int) &U2RXREG;

```

$\ensuremath{\textcircled{\sc c}}$  2007 Microchip Technology Incorporated. All Rights Reserved.

## Step 2: Configure DMA-Ready Peripheral

Configure peripherals to generate interrupt for every transfer (if applicable)

Example: Configure UART2 to generate DMA request after each Tx and Rx character

U2STAbits.UTXISEL0 = 0; // Interrupt after one Tx character is transmitted U2STAbits.UTXISEL1 = 0; U2STAbits.URXISEL = 0; // Interrupt after one RX character is received

#### Enable Error interrupts (if applicable)

Example: Enable and process UART2 error interrupts

```

IEC4bits.U2EIE = 0; // Enable UART2 Error Interrupt

void __attribute__((__interrupt__)) _U2ErrInterrupt(void)

{

/* Process UART 2 Error Condition here */

IFS4bits.U2EIF = 0; // Clear the UART2 Error Interrupt Flag

}

```

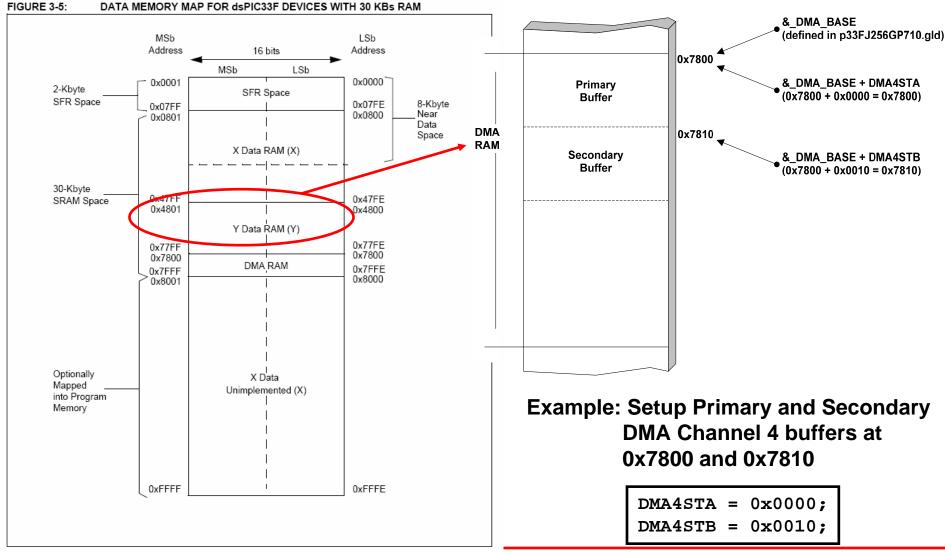

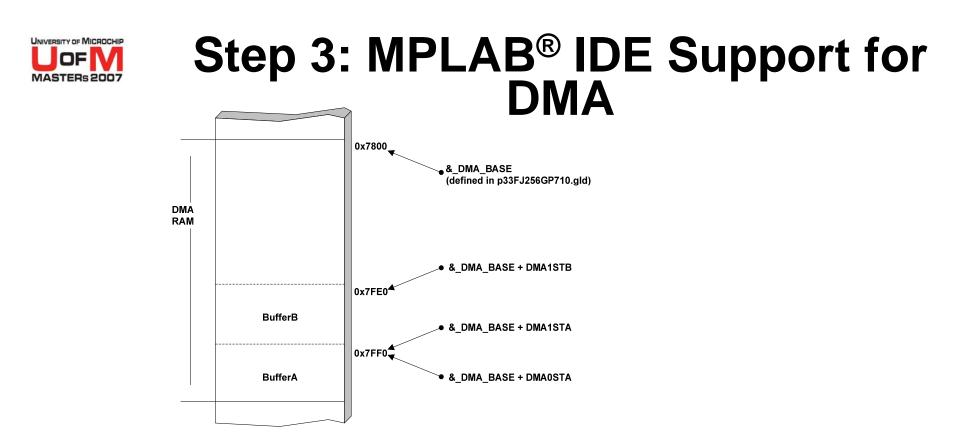

# Step 3: Initialize DPSRAM data start addresses

#### • Use \_\_attribute\_\_(space(dma)) and \_\_builtin\_dmaoffset()

Example: Allocate two buffers 8 words each in DMA memory for DMA Channel 1; Associate DMA Channel 0 with one of the buffers as well

```

unsigned int BufferA[8] __attribute__(space(dma));

unsigned int BufferB[8] __attribute__(space(dma));

DMA1STA = __builtin_dmaoffset(BufferA);

DMA1STB = __builtin_dmaoffset(BufferB);

DMA0STA = __builtin_dmaoffset(BufferA);

```

Example: Setup DMA Channel 0 and 1 to handle 8 DMA requests

DMA0CNT = 7; // 8 DMA Requests DMA1CNT = 7; // 8 DMA Requests

## Step 5: Select appropriate DMA addressing and operating modes

- Word or byte size data transfers

- Peripheral to DPSRAM, or DPSRAM to peripheral transfers

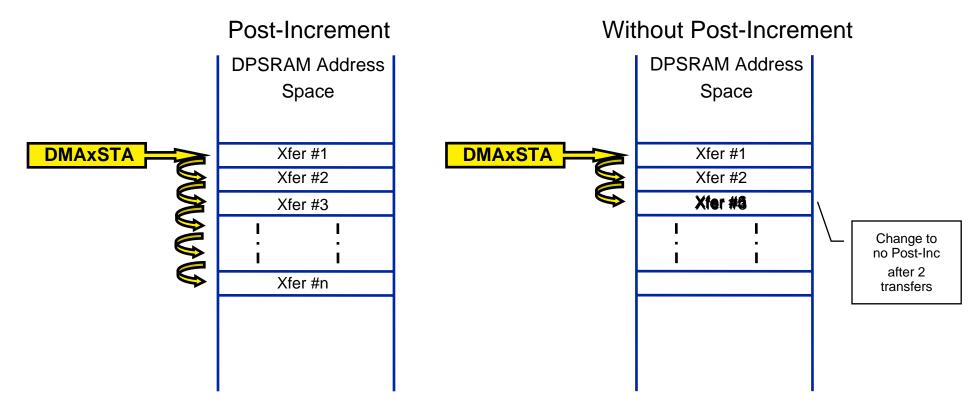

- Post-increment or static DPSRAM addressing

- One-shot or continuous block transfers

- Interrupt the CPU when the transfer is half or fully complete

- Auto switch between two start addresses offsets (DMAxSTA or DMAxSTB) after each transfer complete ('ping-pong' mode)

- Peripheral indirect addressing

- Null data write mode

- Manual Transfer mode

## DMA Modes: Size and Direction

- Word or byte size data transfers

- Peripheral to DPSRAM, or DPSRAM to peripheral transfers

#### Example: Setup DMA Channel 0 and Channel 1 to transfer words to and from peripheral respectively

| = | 0; | //           | Word transfers              |

|---|----|--------------|-----------------------------|

| = | 1; | //           | RAM-to-Peripheral direction |

|   |    |              |                             |

| = | 0; | 11           | Word transfers              |

| = | 0; | 11           | Peripheral-to-RAM direction |

|   | =  | = 1;<br>= 0; | = 1; //<br>= 0; //          |

## DMA Modes: Register Indirect Addressing

## **DMA Modes: One-Shot**

### - Move 1 block of data then disable channel

## **DMA Modes: Continuous**

### Move a block of data then automatically configure channel ready to repeat transfer

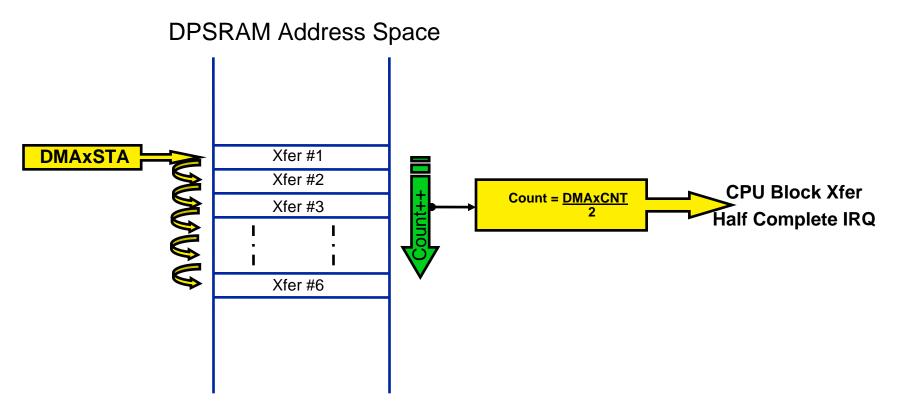

## DMA Modes: Half or Full Transfer

Move ½ block of data then issue interrupt

Continue moving second ½ block of data

# DMA Modes: 'Ping-Pong' and Continuous

## DMA Modes: 'Ping-Pong' and One-Shot

- Least significant bits of address supplied by DMA request peripheral

- Allows 'scatter/gather' addressing schemes to be tailored to the needs of each peripheral

• PIA Mode is also compatible with Auto-Repeat and 'Ping-Pong' modes

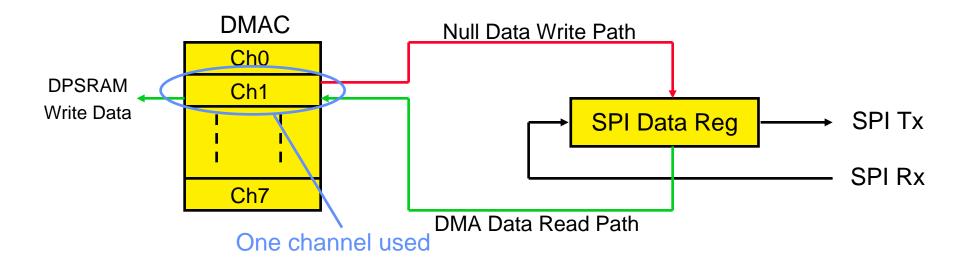

# **DMA Modes: Null Data Write**

#### • SPI has a single peripheral read/write data address

- Requires that data be transmitted (written) in order for external data to be received (read)

- If only data reception required, "null" (zero) write necessary

- "Null write" mode simplifies DMAC operation with SPI

- Automatically writes null (zero) data to peripheral data register after each DMA read

- Avoids wasting another channel for null write

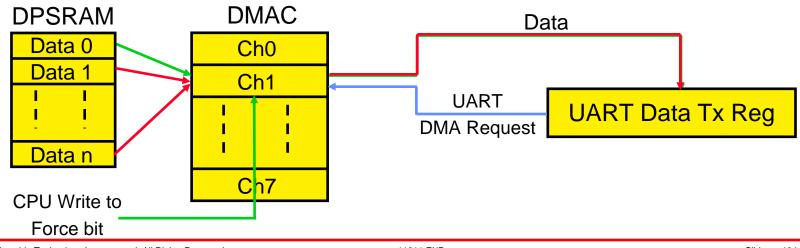

# **DMA Modes: Manual Transfer**

- Provides a means to start a DMA transfer using software

- Setting the FORCE bit in the selected DMA channel mimics a DMA request

- Useful for sending the first element from a block of data to a serial peripheral (e.g. UART)

- Starts the sequence of DMA request to load data into a peripheral

- When peripheral data buffer is empty (data sent), peripheral will issue a DMA request for the next data element

## **DMA Modes: Examples**

#### Example: Configure DMA Channel 0 for: One-Shot, Post-Increment, RAM-to-Peripheral, Single Buffer

| DMA0CONbits.AMODE | = 0 | // Register Indirect with Post-Increment |

|-------------------|-----|------------------------------------------|

| DMA0CONbits.MODE  | = 1 | // One-Shot, Single Buffer               |

| DMA0CONbits.DIR   | = 1 | // RAM-to-Peripheral direction           |

| E | Example: Configure DMA Ch | annel 1 for: Continuous,     |  |  |  |

|---|---------------------------|------------------------------|--|--|--|

|   |                           | Post-Increment,              |  |  |  |

|   |                           | Peripheral-to-RAM            |  |  |  |

|   |                           | Ping-Pong                    |  |  |  |

|   | DMA1CONbits.AMODE = 0;    | // Register Indirect with Po |  |  |  |

| DMA1CONbits.AMODE | = | 0; | // Register Indirect with Post-Increment  |

|-------------------|---|----|-------------------------------------------|

| DMA1CONbits.MODE  | = | 2; | // Continuous, Ping-Pong                  |

| DMA1CONbits.DIR   | = | 0; | <pre>// Peripheral-to-RAM direction</pre> |

# **DMA Interrupts**

- Transfer Complete Interrupt

- Write Collision Interrupt (DMA Trap)

- Should never happen but if they do, handled robustly

- CPU will win; DMAC write ignored

- Cause DMA Fault trap and set channel write collision flag

Example: Enable and process DMA Channel 0 and 1 interrupts

```

IFSObits.DMA0IF

// Clear DMA 0 Interrupt Flag

= 0;

IECObits.DMAOIE = 1;

// Enable DMA 0 interrupt

IFSObits.DMA1IF = 0;

// Clear DMA 1 interrupt

IECObits.DMA1IE = 1;

// Enable DMA 1 interrupt

void attribute ((__interrupt__)) _DMA0Interrupt(void)

ł

/* Process DMA Channel 0 interrupt here */

IFSObits.DMAOIF = 0; // Clear the DMAO Interrupt Flag

}

void __attribute__((__interrupt__)) _DMA1Interrupt(void)

{

/* Process DMA Channel 1 interrupt here */

IFSObits.DMA1IF = 0; // Clear the DMA1 Interrupt Flag

```

## DMA Controller Debug Support

### • 2 DMA debug assist registers included

- DSADR<15:0> : Captures the DPSRAM address of the most recent DMA transfer

- DMACS1 :

- LSTCH<2:0> : Captures the ID of the most recently active DMA channel

- PPSTx : 'Ping-Pong' mode status bits, one per channel. Indicates which buffer is active (A or B)

# Lab 4 DMA

# Lab 4 – Using DMA

Learn DMA module

Lab

- Implement UART loop back utilizing DMA for receiving and transmitting

- Receive and buffer 8 characters one at a time

- Transmit all 8 characters back

$\ensuremath{\mathbb{C}}$  2007 Microchip Technology Incorporated. All Rights Reserved.

# Lab 4 – PIM Swap

## Lab 4 uses the PIC33FJ256GP710

## • To swap the processor:

- Disconnect Explorer 16 power and programmer connections

- Remove PIC24FJ128GA010 PIM

- Place PIC33FJ256GP710 PIM on board, making sure to properly align the notched corner

- Reconnect Power and programmer

# Summary

- We learned how to use some of the new peripherals onboard the 16-bit devices

- We used the Microchip Development Tools Suite for developing with the 16bit PIC<sup>®</sup> MCUs

- We became familiar with some of the PIC24 and dsPIC33 documentation

# **Development Tools Used**

MPLAB<sup>®</sup> REAL ICE<sup>™</sup> Emulator

- DV244005

- Explorer 16 with PIC24FJ128GA010 PIM & dsPIC33FJ256GP710 PIM

- DM240001

- PIC24FJ64GA004 PIM

- DM240002 OR MA240013

## References

## PIC24 & dsPIC33 Datasheet

- Explorer 16 User's Guide

- MPLAB<sup>®</sup> IDE

- C30 Compiler

- ICD2 In Circuit Debugger

## **All Done!** Thank you all for attending Please remember the evaluation sheets

# Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KeeLoq, KeeLoq logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified Iogo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A. All other trademarks mentioned herein are property of their respective companies.