### **11015 MS2** MPLAB® Simulators Advanced Stimulus Additional Examples

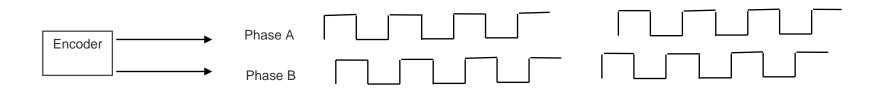

## Using Clock tab for Grey Code Encoder stimulus

• Grey code encoder has 2 pulse trains, one out of phase with the other. When turning in one direction the phase A leads phase B. In the opposite direction phase B will lead phase A.

A goes high when B is low = Clockwise

A goes high when B is high = Anti-Clockwise

# Using Clock tab for Grey Code Encoder stimulus

- Encoder 64 counts/rev. At 300 RPM (5 RPS) we get 320 pulses per second. This is a 3125 us pulse so we will use 3us.

- At 20 MHZ we get 0.2us Instruction cycle

- Pulse width of 6 cycles = 1.2us period for each half of a full wave. (2.4us pulse)

| Label                      | Pin    | Initial | Low Cyc  | High Cyc | Dania                | End       | Comments              |      |

|----------------------------|--------|---------|----------|----------|----------------------|-----------|-----------------------|------|

|                            |        |         | LUW Cyc  |          | -                    |           | Phase A leads Phase B |      |

| PhaseA_up                  |        | High    | 6        |          | -                    | -         | Fhase A leads Fhase b | _    |

| PhaseB_up                  |        | High    | -        |          | 1003 cyc             |           |                       |      |

| PhaseB_dn                  |        | Low     | 6        | 6        |                      |           | Phase B leads Phase A |      |

| PhaseA_dn                  | HE1    | Low     | 6        | 6        | 2003 сус             | 2503 cyc  |                       | _    |

|                            |        |         |          |          |                      |           |                       |      |

| Begin<br>C At Star<br>C PC | `      |         |          |          | End<br>O Nev<br>O PC |           | - l herrill           |      |

| O PC                       | =      |         | 🚬 hex/la | abel     | O PC                 | =         | hex/la                | abei |

| Cycle                      | = 2000 | d       | ecimal   |          | O Cyc                | :le = 250 | 0 decimal             |      |

| O Pin                      | =      | vis 🔻   |          | <b>I</b> | C Pin                | =         | is 📃                  | -    |

## Low power wake up

On startup under the simulator all input pins are at a zero level state. To initialize the low power wakeup pin we need to set this early to a

high state. We will do this by using simple Pin/Register stimulus to set RA0 at 50 ic.

| Pin / Regis | ter Actions | Advanced Pin / Register | Clock Stimulus   | Register Injection Register T | race    |

|-------------|-------------|-------------------------|------------------|-------------------------------|---------|

| Time U      | nits cyc    | •                       |                  | Repeat after 1                | (decima |

| Time        | PORTA       |                         | Click here to Ad | dd Signals                    |         |

| (dec)       | (hex)       |                         |                  |                               |         |

| 50          | ) 01        |                         |                  |                               |         |

|             |             |                         |                  |                               |         |

|             |             |                         |                  |                               |         |

|             |             |                         |                  |                               | _       |

|             |             |                         |                  |                               |         |

|             |             |                         |                  |                               | _       |

|             |             |                         |                  |                               |         |

|             |             |                         |                  |                               |         |

|             |             |                         |                  |                               |         |

|             |             |                         |                  |                               |         |

| 1           |             |                         |                  |                               |         |

## Low power wake up

Now to set the Low power wake up. We need to make RA0 go low as if the level to the pin dropped. Use Clock stimulus to set a clock on RA0. Begin at cycle = 100,000. Initial high, low

for 2 and high for 9,999,998. End set at default Never. Under simulation this will wake the process about every 4 seconds.

| 50 | L Workboo      | ok - C:\\La | ab908.sb  | 5              |          |              |             |              |               | >            |

|----|----------------|-------------|-----------|----------------|----------|--------------|-------------|--------------|---------------|--------------|

| Pi | in / Register. | Actions Ad  | vanced Pi | n / Registe    | er Clock | Stimulus     | Register Ir | njection   R | egister Trace | 1            |

|    | Label          | Pin         | Initial   | Low Cyc        | High Cyc | Begin        | End         | Comments     | :             |              |

| -  | LPWUwaki       | RA0         | High      | 2              | 9999998  | 100000 c     | Never       |              |               |              |

|    |                |             |           |                |          |              |             |              |               |              |

|    |                |             |           |                |          |              |             |              |               | - 11         |

|    |                |             |           |                |          |              |             |              |               |              |

|    |                |             |           |                |          |              |             |              |               | -            |

|    | Begin          |             |           |                |          | ⊢ End—       |             | 1            |               |              |

|    | C At Sta       | art         |           |                |          | • Ne         | wer         |              |               |              |

|    | O PC           |             |           |                |          | O PC         | _           |              |               | abal         |

|    |                | =           |           | i ⊳ hex/       | label    |              | · =         |              |               | apei         |

|    | Cycle          | = 100000    | c         | lecimal        |          | O Cy         | cle =       |              | decimal       |              |

|    | 🔿 Pin          | =           | 🔻 is      |                |          | C Pir        | n = [       | V            | is 🗌          | <b>Y</b>     |

| G  | enerate SCL    | From Workbo | ook       | <u>D</u> eleti | e Row    | <u>S</u> ave | Workbook    | E <u>x</u> i | it <u> </u>   | <u>l</u> elp |

- You can either clock the data in using the firmware (your own code) and driving an output pin. Here we use 1 clock per 8 or 16 bit data

- Or provide a clock as in this example as if it was an external clock. To use your code to clock data eliminate the SPI clock step.

- The data is injected using a file which is attached to the SSPBUF, SFR with trigger on Demand and RAW format.

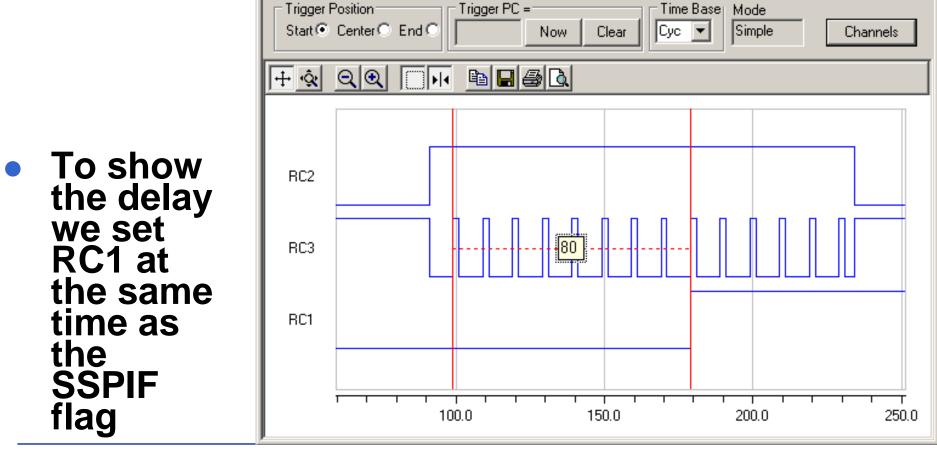

- RC3 is pulsed 20 cycles low 5 cycles high only when RC2 is high.

- RC2 is set high using an Asynchronous pulse for 143 cycles which allows 6 low to high transitions of RC3.

- Each low to high transition of RC3 sets the SSPIF flag. (not quite true SPI which has 1 clock per bit)

- Your program should wait until the IF bit is set then read the SSPBUF (into Wreg)

- Clear the IF flag and loop for the next read.

- When you read the SSPBUF the data from the file will be injected as you read.

© 2007 Microchip Technology Incorporated. All Rights Reserved.

#### • Asynch Pulse to initiate a message

|   |        |               | er - [Untitled]    | -            | _      |                                         | × |

|---|--------|---------------|--------------------|--------------|--------|-----------------------------------------|---|

| [ |        | is (SCL) File |                    |              |        |                                         |   |

|   | C:/DI  | n\tests\T6xx  | x\spi_simulation\; | spi_simulati | on.sci |                                         |   |

|   | Å      | ltach         | Detach             | Import/Me    | rge    |                                         |   |

|   | Asynck | hronous Stimu | ulus —             |              |        |                                         | - |

|   | Fire   | Pin           | Action             | Width        | Units  | Comments                                |   |

|   | >      | RC2           | Pulse High         | 143          | сус    | Pulse long enough to get 6 clock cycles |   |

|   |        |               |                    |              |        |                                         |   |

|   |        |               |                    |              |        |                                         |   |

#### • SPI Clock

| <b></b> S | timulus - C    | :\\SPI_sin | nulation. | sbs         |          |           |      |                  |                |          |

|-----------|----------------|------------|-----------|-------------|----------|-----------|------|------------------|----------------|----------|

| F         | Pin / Register | Actions Ad | vanced Pi | n / Registe | er Clock | Stimulus  | Reg  | gister Injection | Register Trace | Asynch   |

|           | Label          | Pin        | Initial   | Low Cyc     | High Cyc | Begin     |      | End              | Comments       |          |

|           | SPIclock       | RC3        | Low       | 20          | 5        | RC2 is Hi | gh   | RC2 is Low       |                |          |

|           |                |            |           |             |          |           |      |                  |                |          |

|           |                |            |           |             |          |           |      |                  |                |          |

|           |                |            |           |             |          |           |      |                  |                |          |

|           |                |            |           |             |          |           |      |                  |                | <b>_</b> |

|           | •              |            |           |             |          |           |      |                  |                | ▶        |

|           | Begin          |            |           |             |          | nd        |      |                  |                |          |

|           | C At Star      | t          |           |             |          | Never     |      |                  |                |          |

|           | C PC 🔹         | -          | 7         | hex/labe    | 1 0      | O PC      | = [  |                  | hex/label      |          |

|           | C Cycle :      | = 🚺 de     | ec 🗌      |             | <b>.</b> | Cycle     | = [  | dec              |                | <b>_</b> |

|           | ⊙ Pin ⇒        | RC2        | 💌 is 🖡    | ligh 💌      | 0        | Pin       | = [  | RC2 💌            | is Low 💌       |          |

|           | dvanced        | Apply      |           | Delete      | Row      | Save      | e Wi | orkbook          | Exit           | Help     |

#### SPI IRQ Flag set by using a conditional statement

|                     | - C:\\SP)    | I_simula | ation.sbs   |                |                |                            |              |

|---------------------|--------------|----------|-------------|----------------|----------------|----------------------------|--------------|

| in / Regis          | ster Actions | Advanc   | ced Pin / R | legister       | Clock Stimulus | Register Injection Registe | r Trace Asyn |

| Define <sup>-</sup> | Triggers     |          |             |                |                |                            |              |

| Enable              | Condition    | Туре     | Re-Arm [    | Delay          | PIR1.SSPIF     | Click here to Add Sign     | ials 🔺       |

|                     | COND1        | Cont     | 10          | сус            | 1              |                            |              |

|                     |              |          |             |                |                |                            |              |

|                     |              |          |             |                |                |                            |              |

|                     |              |          |             |                |                |                            | -            |

|                     |              |          |             |                | I              |                            |              |

| - Define (          | Conditions - |          |             |                |                |                            |              |

| Condition           | n            | When     | Changed     |                | Wait           | Commente                   |              |

|                     |              | WHEH     | changeu     |                | w ait          | Comments                   |              |

| COND1               |              | RC3      | =           |                | 1              | When RC3 goes high se      | et IF re-arm |

|                     |              |          |             | -              | 1              |                            | et IF re-arm |

|                     |              |          |             | -              | 1              |                            | et IF re-arm |

|                     |              |          |             | -              |                |                            | et IF re-arm |

|                     |              |          |             |                |                |                            | t IF re-arm  |

| COND1               | Pin F        | RC3      |             |                |                | When RC3 goes high se      | ¥            |

|                     | Pin F        |          |             | )<br>Delete Ro |                |                            | et IF re-arm |

- If you wanted to clock bits and have the IF set after 8 bit clocks. You could set the wait time on COND1 to delay the duration of 8 clock cycles.

- You can then set the re-arm delay to avoid a retrigger.

|    | innaias              | - C:\\SPI    | _simula     | ation.sbs    |             |                |      |                    |                    | _ 🗆 🗵      |

|----|----------------------|--------------|-------------|--------------|-------------|----------------|------|--------------------|--------------------|------------|

| Pi | n / Beai             | ster Actions | Advan       | ced Pin / R  | egister   ( | Clock Stimulus | l Br | egister Injection  | Begister Trace     | Asunch     |

|    |                      |              |             |              | - 1         |                | .1   | giotor inteodori I | Theglotter Theorem | Tristion   |

| [  | Define               | Triggers     |             |              |             |                |      |                    |                    |            |

|    | Enable               | Condition    | Туре        | Re-Arm D     | Delay       | PIR1.SSPIF     |      | Click here to /    | Add Signals        |            |

|    | ✓                    | COND1        | Cont        | 100          | сус         | 1              |      |                    |                    |            |

|    |                      |              |             |              |             |                |      |                    |                    |            |

|    |                      |              |             |              |             |                |      |                    |                    |            |

|    |                      |              |             |              |             |                |      |                    |                    | _          |

|    | _                    |              |             |              |             |                |      |                    |                    | <u> </u>   |

|    |                      |              |             |              |             |                |      |                    |                    |            |

|    |                      | Conditions - |             |              |             |                |      |                    |                    |            |

|    | - Define<br>Conditio |              | When        | Changed      |             | Wait           |      | Con                | nments             | -          |

|    |                      | n            | When<br>{C3 | Changed<br>= | 1           |                | сус  |                    |                    | IF         |

|    | Conditio             | n            |             |              |             |                | сус  |                    |                    | IF         |

|    | Conditio             | n            |             |              |             |                | сус  |                    |                    | F          |

|    | Conditio             | n            |             |              | 1           |                | сус  |                    |                    | IF         |

|    | Conditio             | n            |             |              | 1           |                | сус  |                    |                    | IF         |

| A  | Conditio             | n Pin F      |             | =            | )elete Ro   | 80             |      |                    |                    | IF<br>Help |

#### SPI Data file injection

| Label      | Reg / Var | Trigger | PC Value | Width | Data Filename       | Wrap | Format | Comments   |

|------------|-----------|---------|----------|-------|---------------------|------|--------|------------|

| (optional) | SSPBUF    | Demand  |          | 1     | C:\bin\Tests\16xxx\ | Yes  | Raw    | (optional) |

|            |           |         |          |       |                     |      |        |            |

|            |           |         |          |       |                     |      |        |            |

|            |           |         |          |       |                     |      |        |            |

|            |           |         |          |       |                     |      |        |            |

|            |           |         |          |       |                     |      |        |            |

|            |           |         |          |       |                     |      |        |            |

|            |           |         |          |       |                     |      |        |            |

|            |           |         |          |       |                     |      |        |            |

|            |           |         |          |       |                     |      |        |            |

|            |           |         |          |       |                     |      |        |            |

|            |           |         |          |       |                     |      |        |            |

# SSPBUF Data 1 character is read on each IRQIF The string is 5 characters plus CRLF

| C:\\SP | I_Data.txt |

|--------|------------|

| 1      | \$МТО@     |

| 2      | \$MT10     |

| 3      | \$MT20     |

| 4      | \$MT30     |

| 5      |            |

|        |            |

#### SPI Clock as seen within the Logic Display

| Trigger Position<br>Start I Center C End C | Trigger PC = Time Base Mode Now Clear Cyc  Simple Channel: | 5 |

|--------------------------------------------|------------------------------------------------------------|---|

|                                            |                                                            |   |

| RC2                                        |                                                            |   |

#### SPI Clock as seen within the Logic Display when using 8 clock pulses per IRQ

\_ 🗆 ×