### 11038 PSA

# I<sup>2</sup>C<sup>TM</sup> Development using the PICkit<sup>TM</sup> Serial Analyzer

### **Class Objective**

#### When you finish this class you will:

- Explain the I<sup>2</sup>C<sup>™</sup> protocol

- Use the PICkit<sup>™</sup> Serial Analyzer to exchange

I<sup>2</sup>C messages to a target device

- Configure the MSSP peripheral for I<sup>2</sup>C slave mode

- Program the MSSP peripheral for I<sup>2</sup>C slave mode

### **Agenda**

- I<sup>2</sup>C<sup>TM</sup> Protocol Overview

- PICkit™ Serial Analyzer

- Configuring the MSSP peripheral for I<sup>2</sup>C slave mode

- Programming the MSSP peripheral as an I2C slave

### I<sup>2</sup>C<sup>TM</sup> Protocol Overview

#### I<sup>2</sup>C<sup>TM</sup> Protocol Overview

- Introduction

- Hardware Overview

- Communication Elements

- Message Formatting

#### I<sup>2</sup>C<sup>TM</sup> Introduction

NXP (formerly Philips Seminconductor)

Inter-Integrated Circuit (I<sup>2</sup>C) Specification

Specification: www.standardics.nxp.com/literature/books/i2c/pdf/i2c.bus.specification.pdf

- Synchronous,

- Master-Slave Protocol,

- Bidirectional,

- Half Duplex Serial Interface

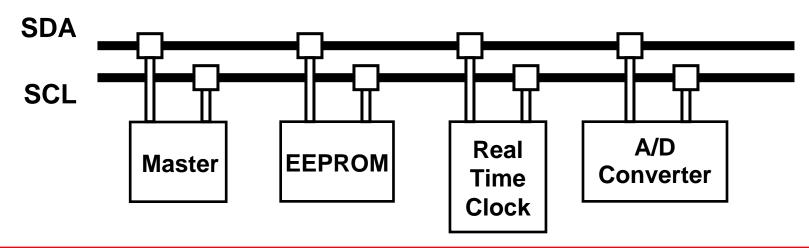

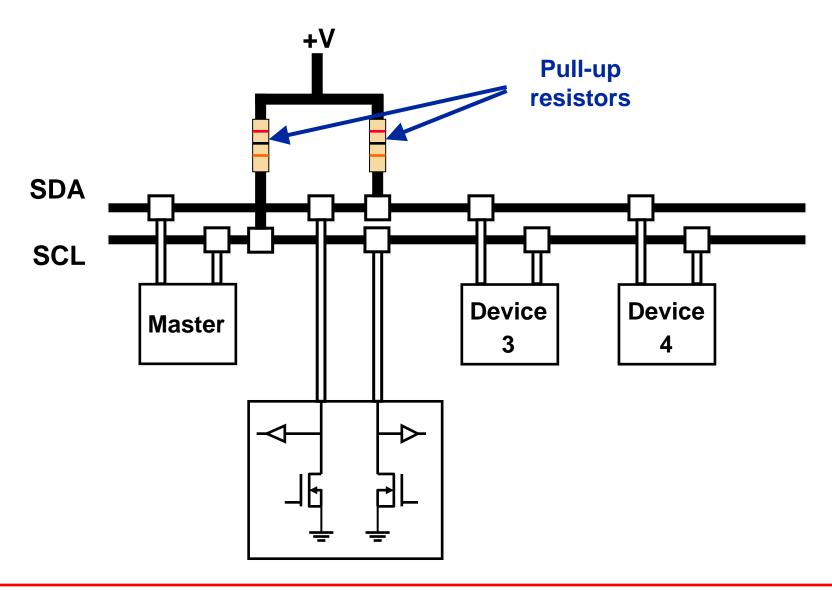

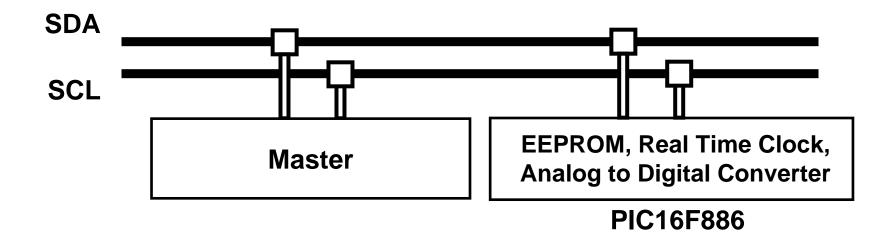

### I<sup>2</sup>C<sup>TM</sup> Hardware Overview

- Start and Stop Condition:

- Generated by Master

- After Start Condition: Bus is Busy

- After Stop Condition: Bus is Free

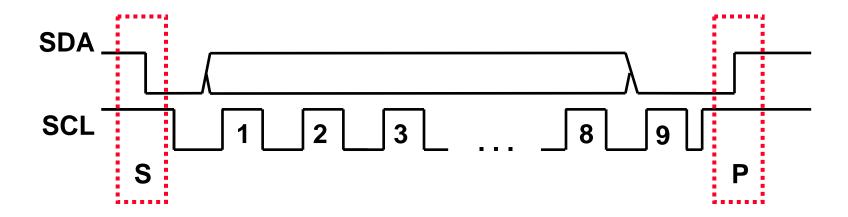

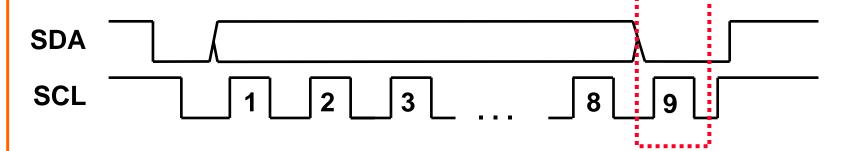

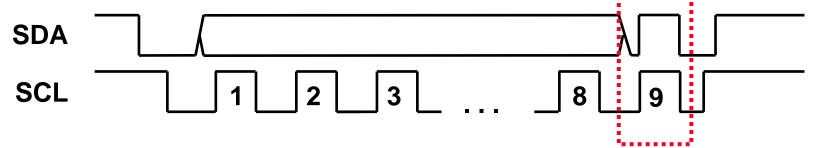

#### Data Transfer

- 8 bits of data are sent on the bus

- Data is valid when SCL is high

- Types of Data: Address Byte, Data Byte

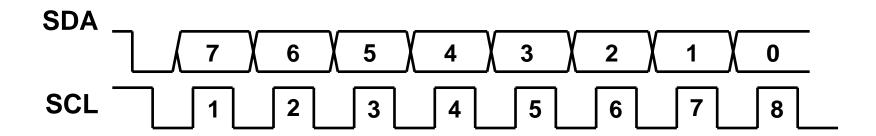

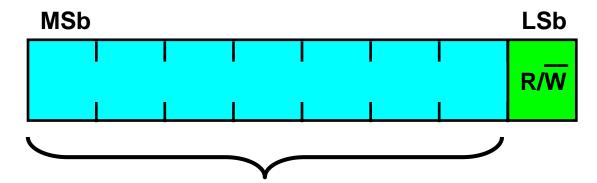

#### Slave Address

- 7 bits (10 bits also exists)

- First byte following the start condition

- Read/Write Bit

7-bit Slave Address

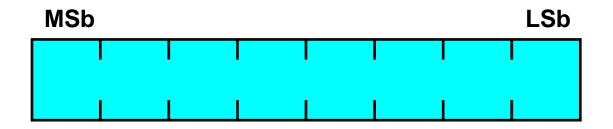

#### Data Byte

- 8 bits

- Data can be read or written to/from I<sup>2</sup>C device

**Data Byte**

# Acknowledge

Generated by master or slave by holding the SDA low on the 9th clock pulse

### I<sup>2</sup>C<sup>TM</sup> Message Formatting

Master Write to Slave

(Word Address)

| 101 Diavo Madiodo IVI IMI Data IMI Data IMI | S | Slave Address [W] | Α | Data | Α | Data | Α | Р |

|---------------------------------------------|---|-------------------|---|------|---|------|---|---|

|---------------------------------------------|---|-------------------|---|------|---|------|---|---|

#### Legend:

S =Start Condition A =Acknowledge

P =Stop Condition A =No Acknowledge

= Master to Slave = Slave to Master

# I<sup>2</sup>C<sup>™</sup> Message Formatting

**Master Read from Slave**

| S | Slave Address [R] | Α | Data | Α | Data | Ā | Р |

|---|-------------------|---|------|---|------|---|---|

|---|-------------------|---|------|---|------|---|---|

#### Legend:

S = **Start** Condition A = Acknowledge

P = **Stop** Condition A = No Acknowledge

= Master to Slave = Slave to Master

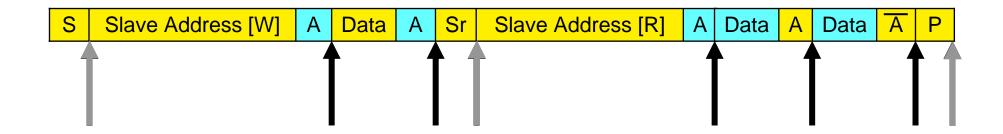

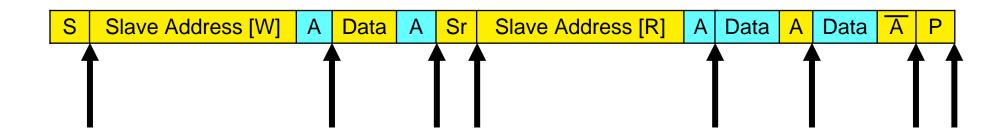

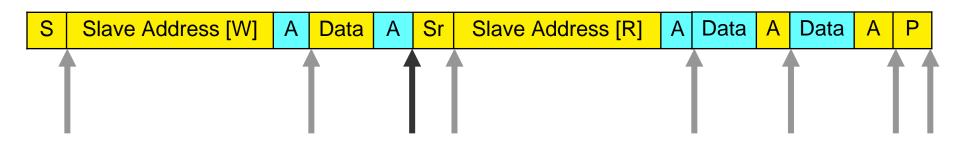

### I<sup>2</sup>C<sup>TM</sup> Message Formatting

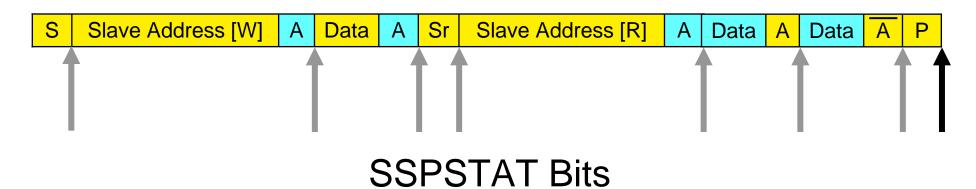

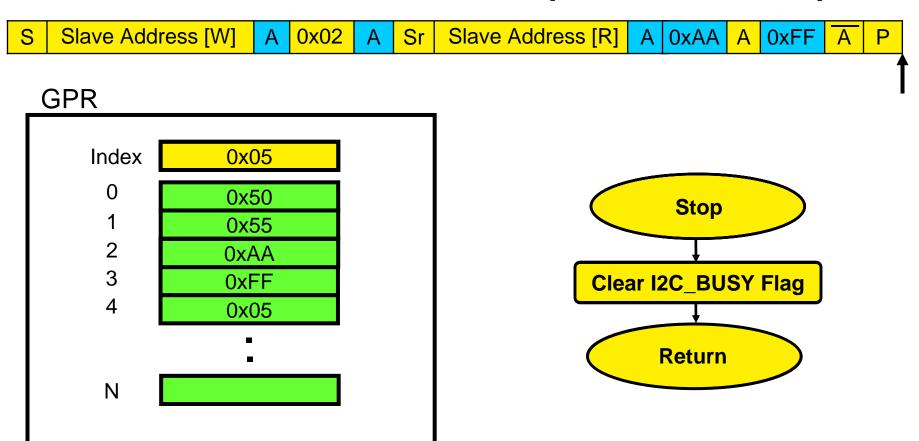

Master Write then Read from Slave (Combination) **Master Write** (Word Address) Slave Address [W] Data Α **Master Read** Slave Address [R] Data Α Data **Restart Condition** Legend: S = **Start** Condition A = Acknowledge A = No Acknowledge P = **Stop** Condition = Master to Slave = Slave to Master

### I<sup>2</sup>C<sup>TM</sup> Protocol Overview

### Summary

- Introduction

- Hardware Overview

- Communication Elements

- Message Formatting

- PICkit Serial Analyzer

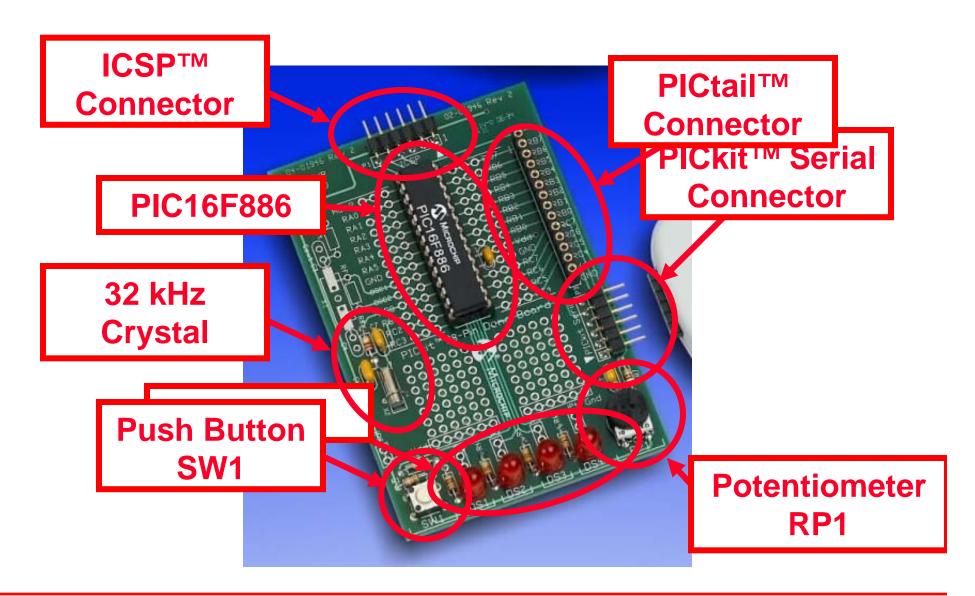

- 28-Pin Demo Board

- PC Program

- 28-Pin Demo Board Demonstration

- I<sup>2</sup>C<sup>™</sup> Basic Operations

- Hands On Lab #1

- PICkit Serial Analyzer Operation

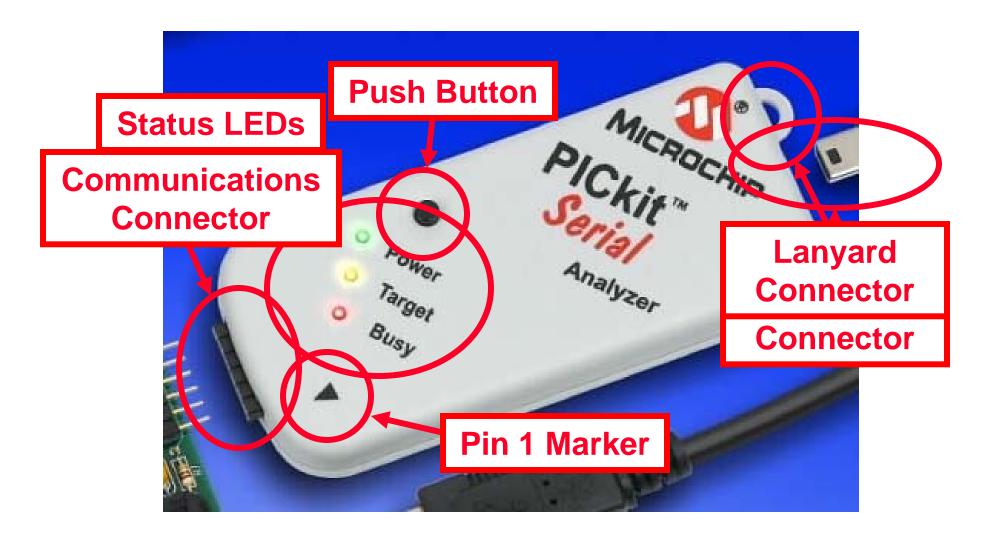

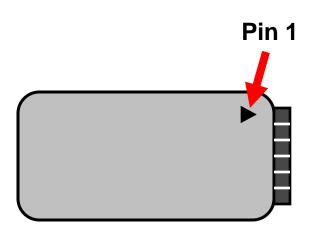

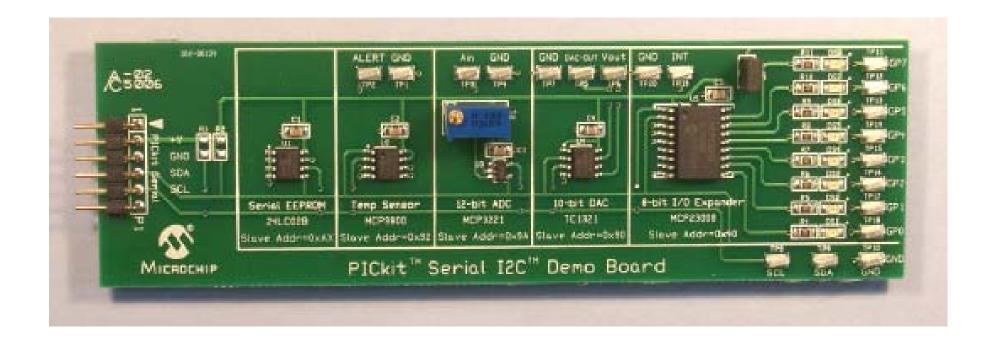

### PICkit<sup>™</sup> Serial Analyzer DV164122

### PICkit<sup>™</sup> Serial Analyzer

### Pin Assignments

| Pin | I <sup>2</sup> C <sup>TM</sup> | SPI | USART |

|-----|--------------------------------|-----|-------|

| 1   | -                              | CS  | TX    |

| 2   | +V                             | +V  | +V    |

| 3   | GND                            | GND | GND   |

| 4   | SDA                            | SDI |       |

| 5   | SCL                            | SCK |       |

| 6   |                                | SDO | RX    |

#### Board Connection

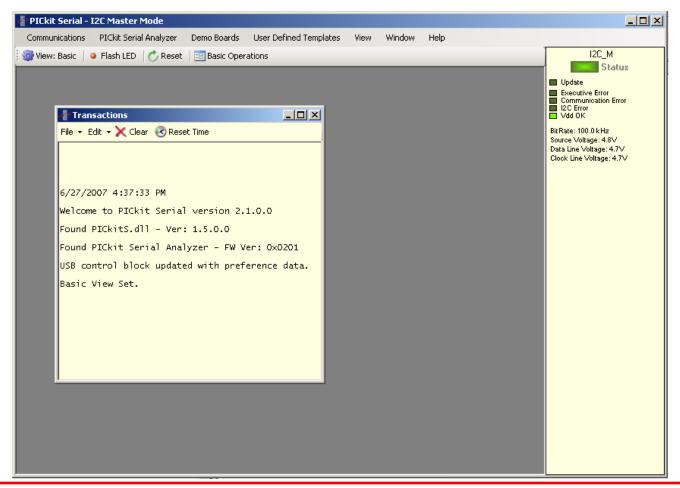

### PC Program

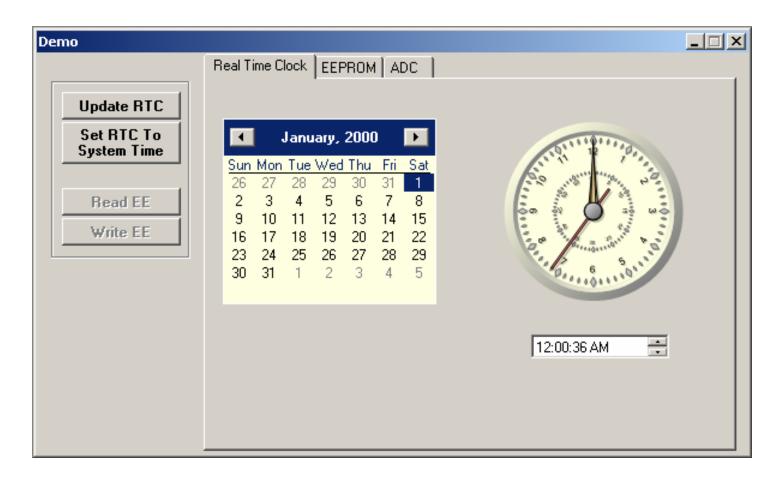

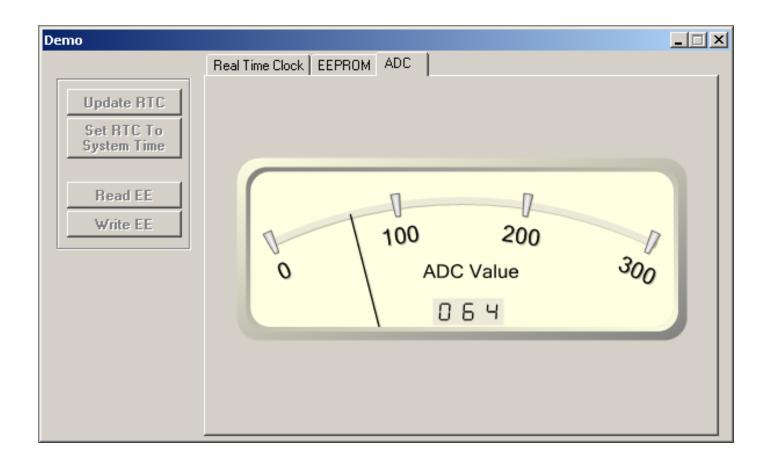

#### RTC Demonstration

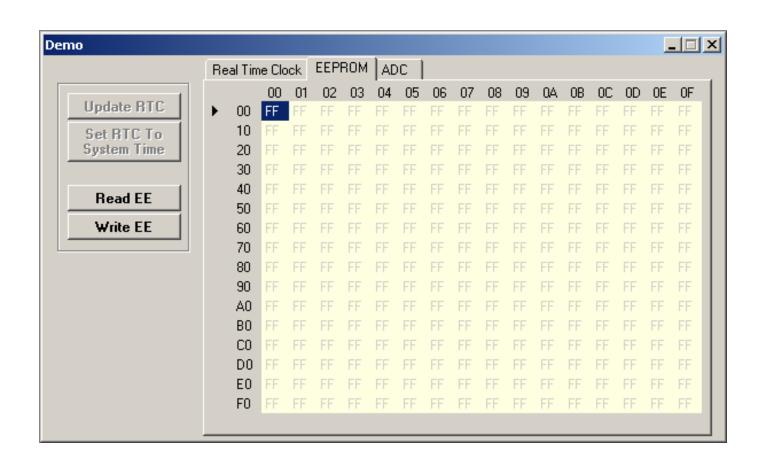

#### Serial EEPROM Demonstration

27

#### ADC Demonstration

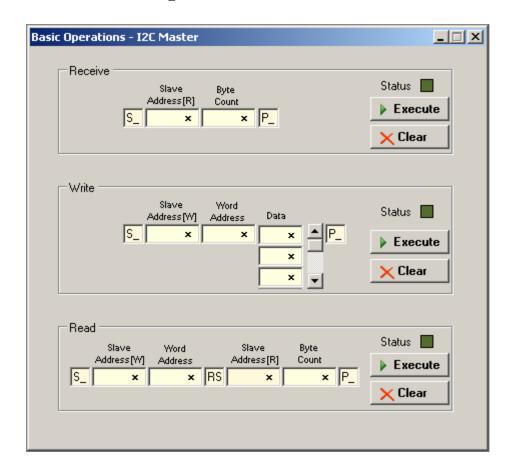

### I<sup>2</sup>C<sup>™</sup> Basic Operations

#### Hands On Lab #1

# PICkit™ Serial Analyzer **Operation**

- Summary

- PICkit Serial Analyzer

- 28-Pin Demo Board

- PC Program

- 28-Pin Demo Board Demonstration

- I<sup>2</sup>C<sup>™</sup> Basic Operations

- Hands On Lab #1

- PICkit Serial Analyzer Operation

# Configuring the **MSSP Peripheral** for I<sup>2</sup>C<sup>TM</sup> Slave Mode

### **MSSP Peripheral**

- MSSP I<sup>2</sup>C<sup>TM</sup> Modes

- Registers

- Block Diagram

- Address Masking Feature

- Interrupts

### MSSP I<sup>2</sup>C<sup>TM</sup> Modes

#### Supports:

- Master/Multi-Master Mode

- Slave Mode

- 7 or 10-bit Addressing

#### Configurations:

- I<sup>2</sup>C Master Mode

- I<sup>2</sup>C Slave Mode

- I<sup>2</sup>C Slave Mode with Start and Stop bit interrupts enabled

- I<sup>2</sup>C firmware controlled master, slave is idle

### **SSPCON** Register

#### SSPCON Register

**WCOL** SSPOV SSPEN CKP SSPM3 | SSPM2 | SSPM1 SSPM<sub>0</sub>

**SSPEN: Synchronous Serial Port Enable Bit** 1 = Configures SDA and SCL as serial port pins.

SSPM<3:0>: Synchronous Serial Port Mode Select Bits 1110 = I<sup>2</sup>C Slave Mode, 7-Bit Address with Start/Stop bit interrupts enabled

WCOL = Write Collision Detect Bit

SSPOV = Receive Overflow Indicator

= Clock Polarity Bit CKP

### **SSPSTAT** Register

#### **SSPSTAT** Register

SMP CKE D/A P S R/W UA BF

$D/\overline{A}$  = Data / Not Address Bit

P = Stop Bit

S = Start Bit

R / W = Read / Not Write Bit

BF = Buffer Full Bit

**SMP** = Slew Rate Control for High Speed Enable

CKE = SPI Clock Edge Select

**UA** = Update Address Bit (for 10-bit address mode)

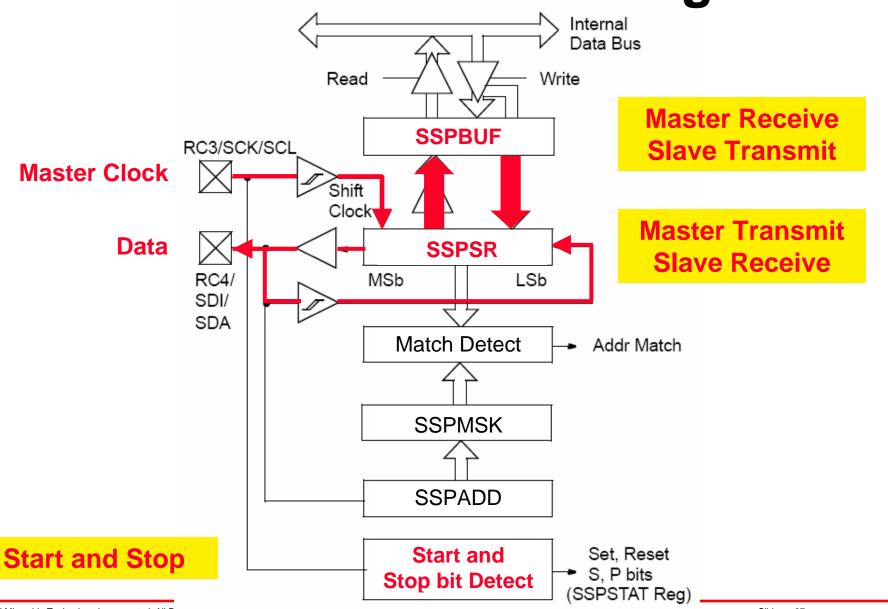

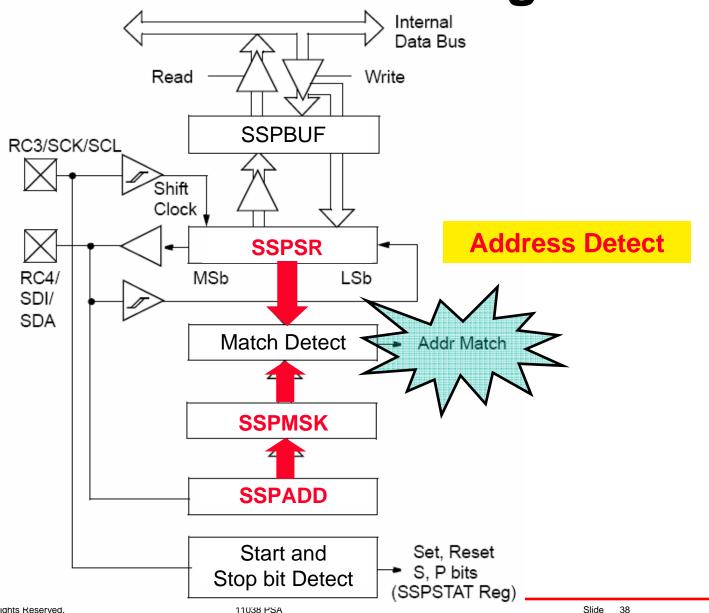

## MSSP I<sup>2</sup>C™ Block Diagram

## MSSP I<sup>2</sup>C™ Block Diagram

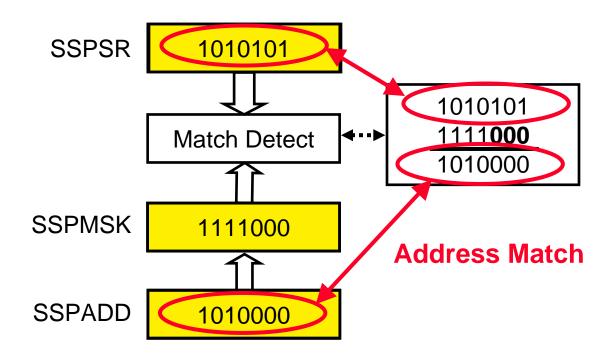

## **Address Masking Feature**

- What is it?

- It allows a PIC® MCU to ACK more than one address.

- What is it good for?

- Integrating multiple I<sup>2</sup>C<sup>™</sup> devices in one PIC MCU

## **How Address Masking Works**

- Allows device to acknowledge multiple addresses

- Turns masked bits into don't cares

## Configuring SSPMSK Register

#### SSPCON Register

| WCOL   SSPOV   SSPEN   CKP   SSPM3   SSPM2   SSPM1   SSPM0 | WCOL | SSPOV | SSPEN | СКР | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

|------------------------------------------------------------|------|-------|-------|-----|-------|-------|-------|-------|

|------------------------------------------------------------|------|-------|-------|-----|-------|-------|-------|-------|

SSPM<3:0>: Synchronous Serial Port Mode Select Bits 1001 = Load SSPMSK register at SSPADD SFR Address

#### SSPMSK Register

| MSK7 MSK6 MSK5 | SK4 MSK3 | MSK2 | MSK1 | MSK0 |

|----------------|----------|------|------|------|

|----------------|----------|------|------|------|

### Two Step Process

- 1. **SSPCON**, **SSPM<3:0>** = 1001

- 2. Accessed through **SSPADD** register

## **Configuring SSPADD Register**

#### **SSPCON** Register

| WCOL S | SPOV SSPEN | CKP | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

|--------|------------|-----|-------|-------|-------|-------|

|--------|------------|-----|-------|-------|-------|-------|

SSPM<3:0>: Synchronous Serial Port Mode Select Bits 1110 = I<sup>2</sup>C Slave Mode, 7-Bit Address with Start/Stop bit interrupts enabled

#### **SSPADD** Register

| ADD <sup>*</sup> | ADD6 | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0 |

|------------------|------|------|------|------|------|------|------|

|                  |      |      |      |      |      |      |      |

#### **Reserve Addresses**

B'0000 000' - General Call Address

B'0000 001' - CBUS address

B'0000 010' - Reserved for different bus format

**B'0000 011' – Future Purposes**

B'0000 1XX' - Hs-mode master code

B'1111 1XX' – Future Purposes

B'1111 0XX' - 10-bit Slave Address

## I<sup>2</sup>C<sup>™</sup> Interrupt Events

#### **PIR1** Register

- Start and Stop Conditions

- Data Transmit and Receive

## Interrupt Status and Enable

#### **PIE1 Register**

|--|

#### **PIR1** Register

|  | ADIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

|--|------|------|------|-------|--------|--------|--------|

|--|------|------|------|-------|--------|--------|--------|

#### **INTCON** Register

| GIE | PEIE | TOIE | INTE | RABIE | TOIF | INTF | RABIF |

|-----|------|------|------|-------|------|------|-------|

|-----|------|------|------|-------|------|------|-------|

## **MSSP Peripheral**

## Summary

- Introduction

- Registers

- Block Diagram

- Address Masking Feature

- Interrupts

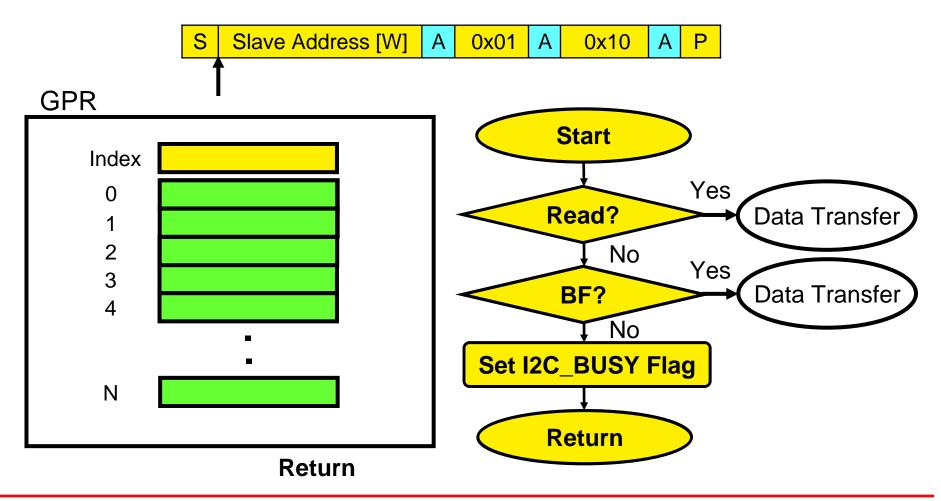

# **Programming the MSSP** peripheral as an I<sup>2</sup>C<sup>TM</sup> slave

## **Programming the MSSP**

- Firmware Overview

- Events

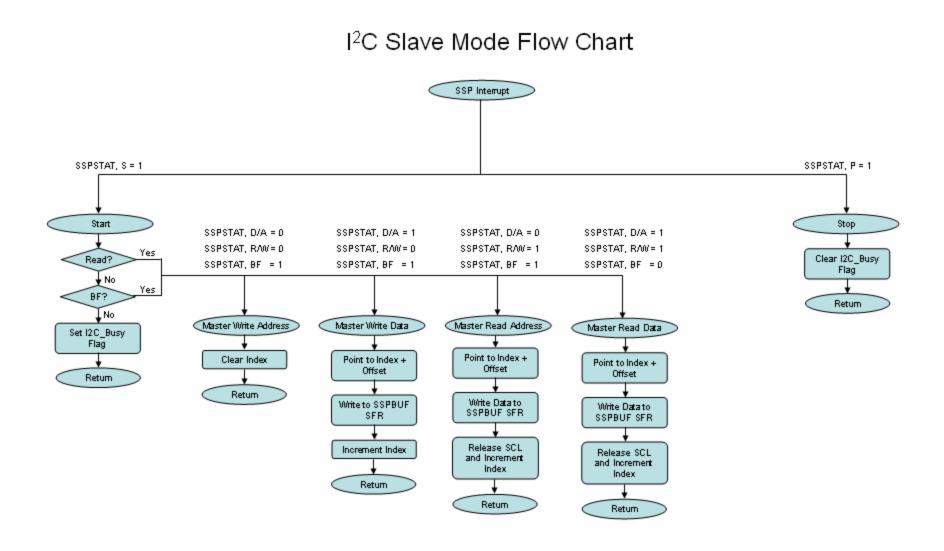

- I<sup>2</sup>C<sup>TM</sup> Slave State Machine

- Master Write

- Master Write then Read (Combination)

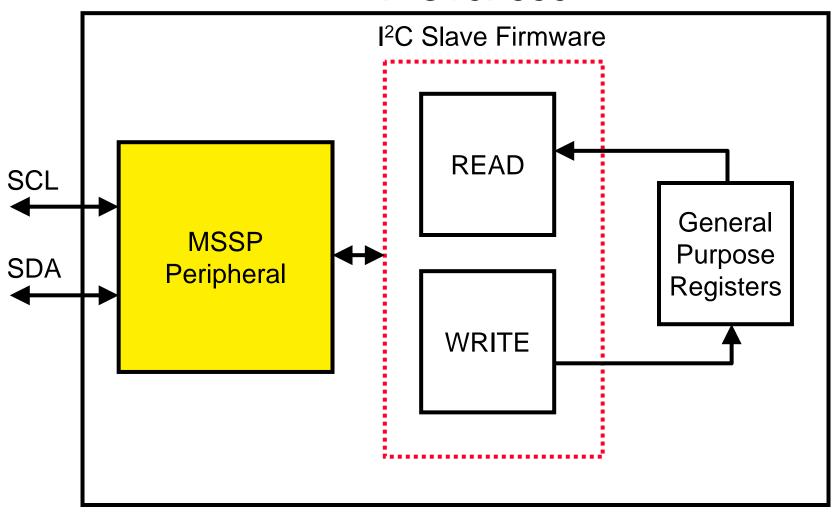

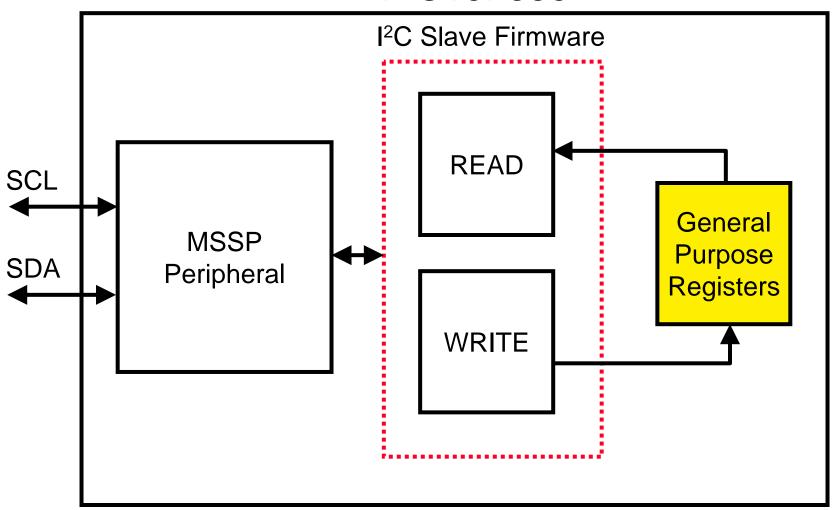

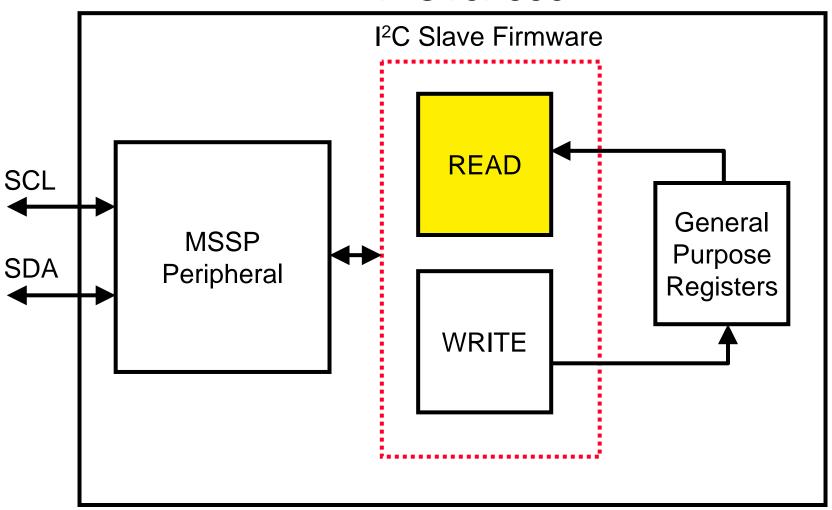

### I<sup>2</sup>C<sup>TM</sup> Slave Mode Firmware Overview

#### PIC16F886

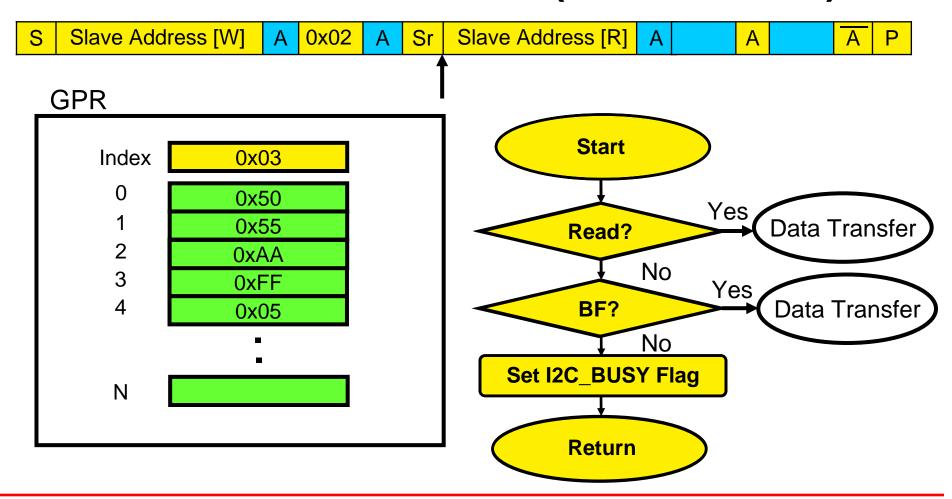

### An Event is a:

- 1. Start or Restart Condition

- Master Write Address

- 3. Master Write Data

- 4. Master Read Address

- Master Read Data

- 6. Stop Condition

SSPIF bit indicates when an event has occurred

#### **PIR1 Register**

Events will be identified by bits in the SSPSTAT register

```

D/A

S

R/W

SMP

CKE

P

UA

BF

D/\overline{A}

= Data / Not Address Bit

= Stop Bit

= Start Bit

R/W

= Read / Not Write Bit

= Buffer Full Bit

BF

SMP

= Slew Rate Control for High Speed Enable

CKE

= SPI Clock Edge Select

= Update Address Bit (for 10-bit address mode)

UA

```

- Start Condition

- Bus is busy

**SSPSTAT Bits**

• S = 1

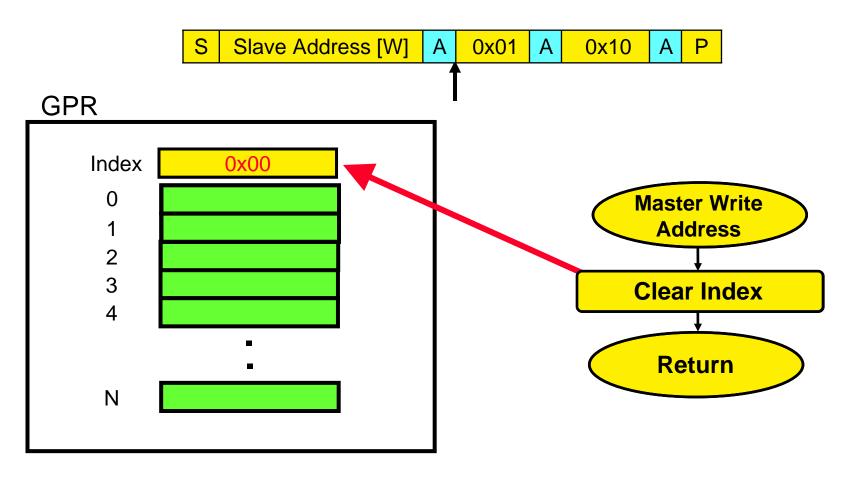

#### Master Write Address

Master has sent a <u>write request</u> with a matching <u>slave address</u>

### **SSPSTAT Bits**

- $D/\overline{A} = 0$

- $R/\overline{W} = 0$

- BF = 1

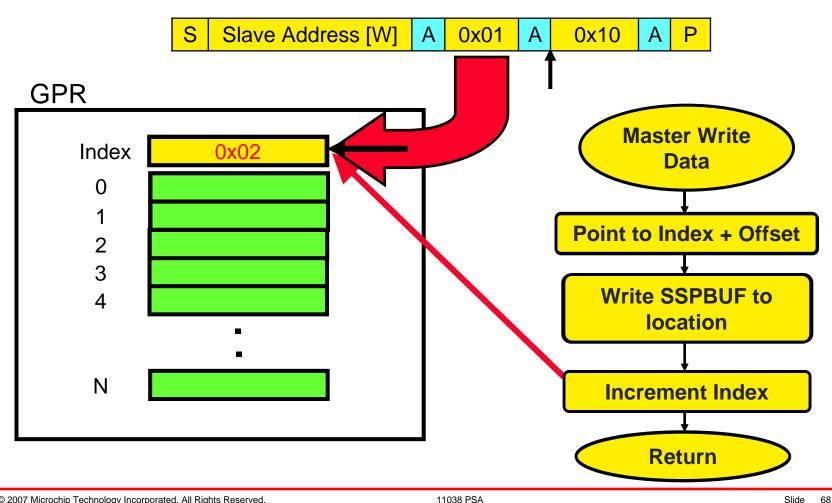

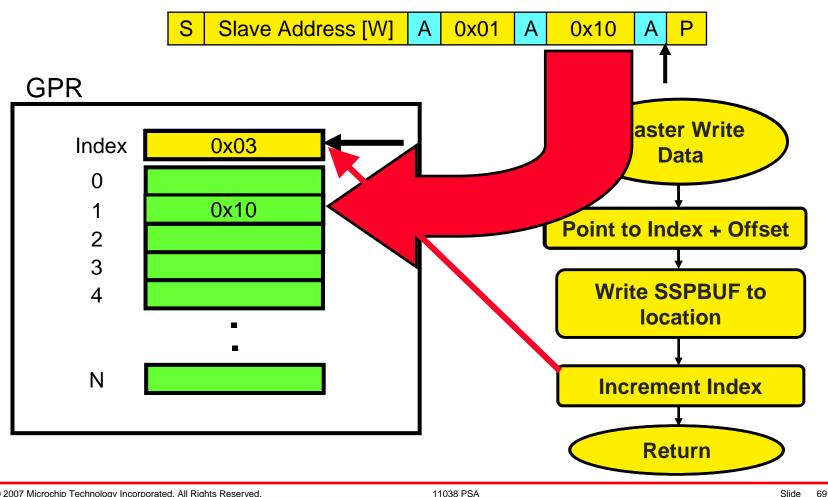

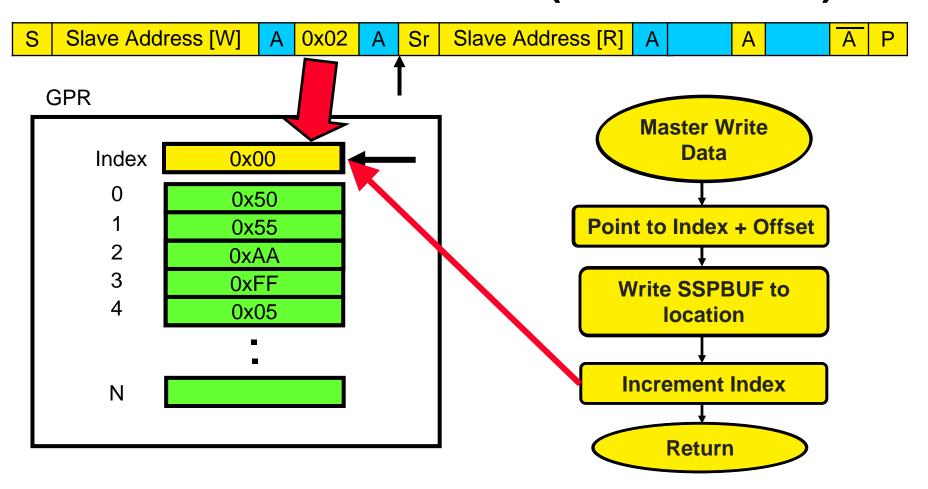

#### Master Write Data

Master has sent a <u>data byte</u> following a <u>write request</u>

### **SSPSTAT Bits**

- $\overline{D/A} = 1$

- $R/\overline{W} = 0$

- BF = 1

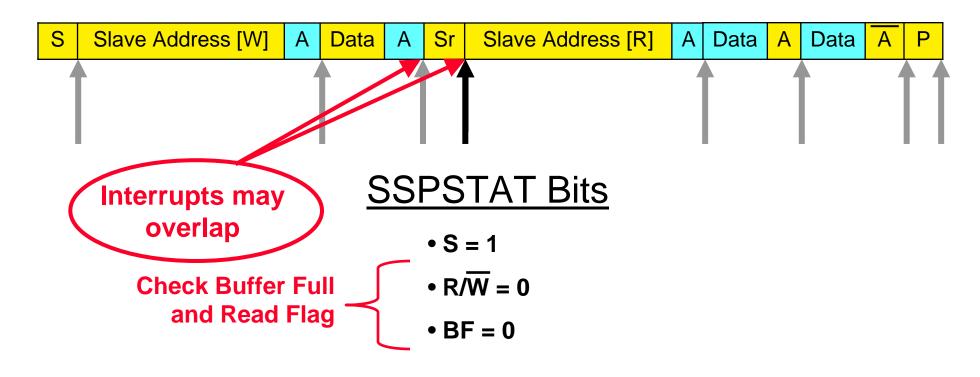

#### Restart Condition

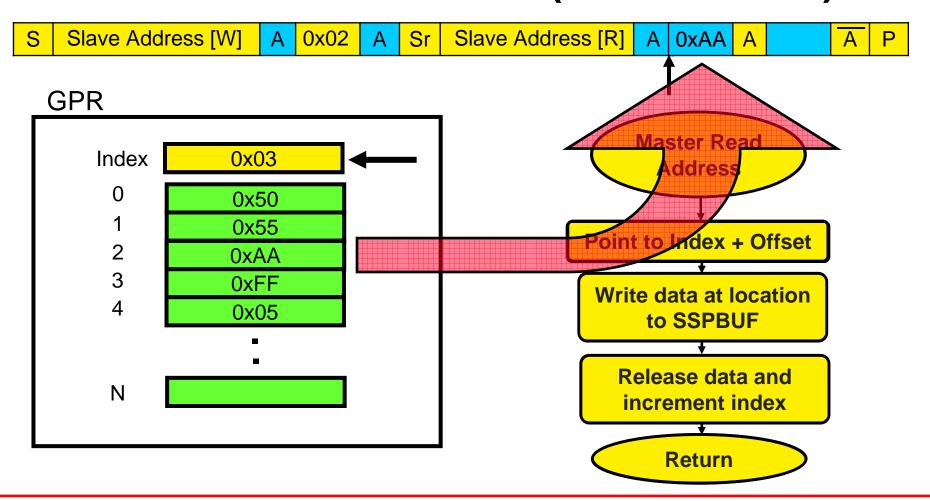

#### Master Read Address

Master has sent a <u>read request</u> with a matching <u>slave address</u>

### **SSPSTAT Bits**

- $D/\overline{A} = 0$

- R/W = 1

- BF = 1

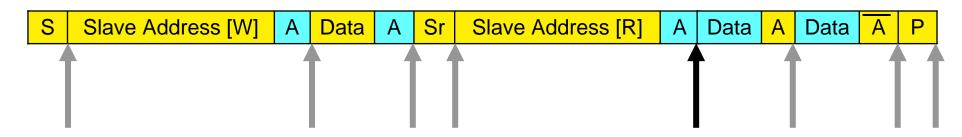

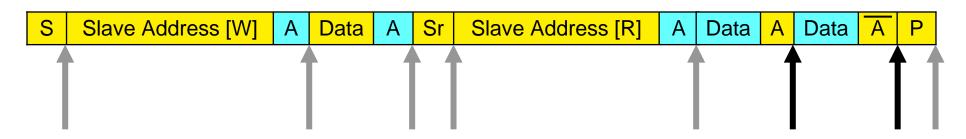

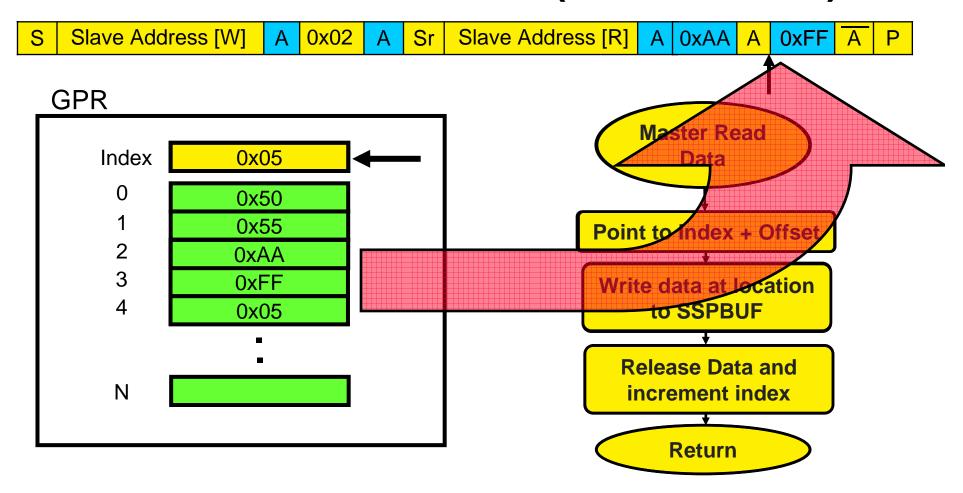

#### Master Read Data

Master has read a <u>data byte</u> after a matching slave address and <u>read request</u> has been sent

### **SSPSTAT Bits**

- $D/\overline{A} = 1$

- $R/\overline{W} = 1$

- BF = 0

## Stop Condition

- The end of communication

- The bus is free

• P = 1

## **Events Summary**

- We now know:

- How to decode each event:

- Write Events

- Read Events

- Start/Stop Conditions

- Two types of message formats:

- Read, Write

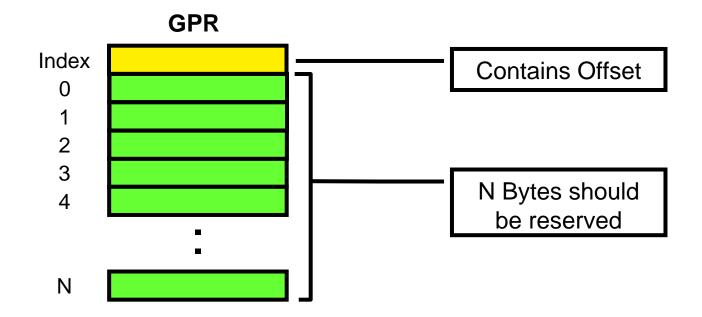

### I<sup>2</sup>C<sup>TM</sup> Slave Mode Firmware Overview

#### PIC16F886

- General Purpose Registers

- Data must be sequential

## **Assembly Code Example**

```

#define DEVICE RAM LENGTH .9 ; Device RAM Length

#define BYTEO

(DEVICE RAM + 0 \times 01)

#define BYTE1

(DEVICE RAM + 0 \times 0 2)

#define BYTE2

(DEVICE RAM + 0 \times 03)

#define BYTE3

(DEVICE RAM + 0 \times 04)

#define BYTE4

(DEVICE RAM + 0 \times 05)

#define BYTE5

(DEVICE RAM + 0 \times 06)

#define BYTE6

(DEVICE RAM + 0x07)

#define BYTE7

(DEVICE RAM + 0x08)

#define BYTE8

(DEVICE RAM + 0x09)

udata

```

res

DEVICE RAM

DEVICE RAM LENGTH

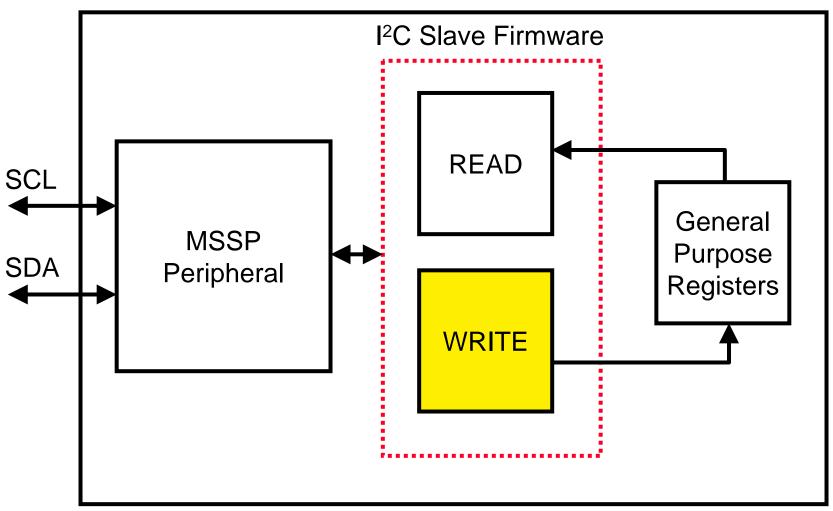

### I<sup>2</sup>C<sup>TM</sup> Slave Mode Firmware Overview

#### PIC16F886

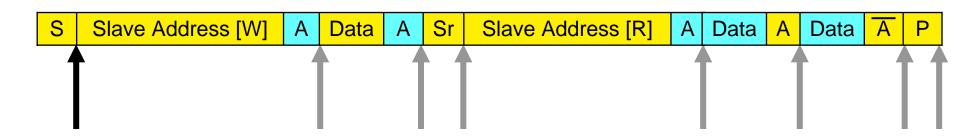

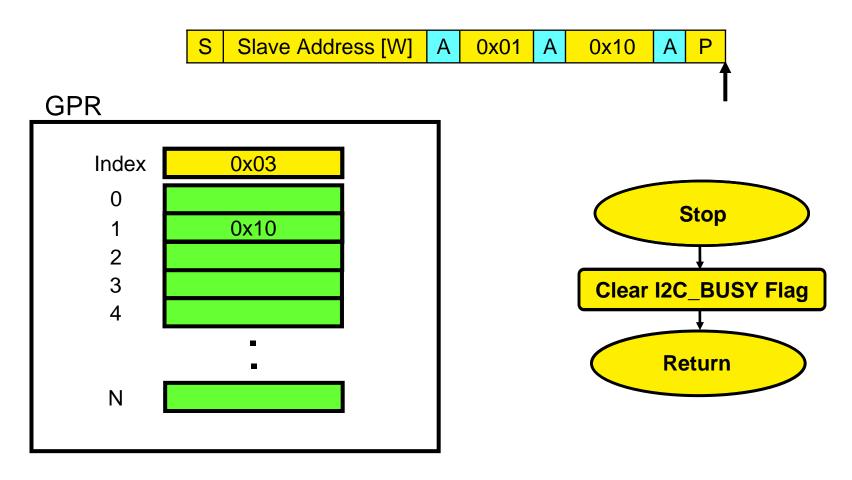

**Master Write**

Write data byte (0x10) to word address (0x01)

### I<sup>2</sup>C<sup>TM</sup> Slave Mode Firmware Overview

#### PIC16F886

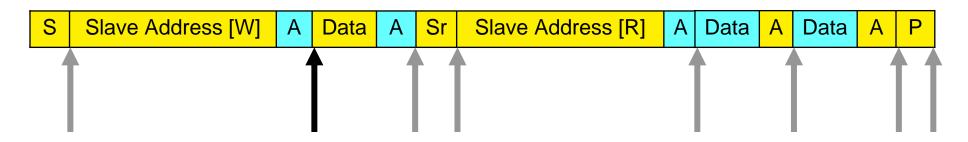

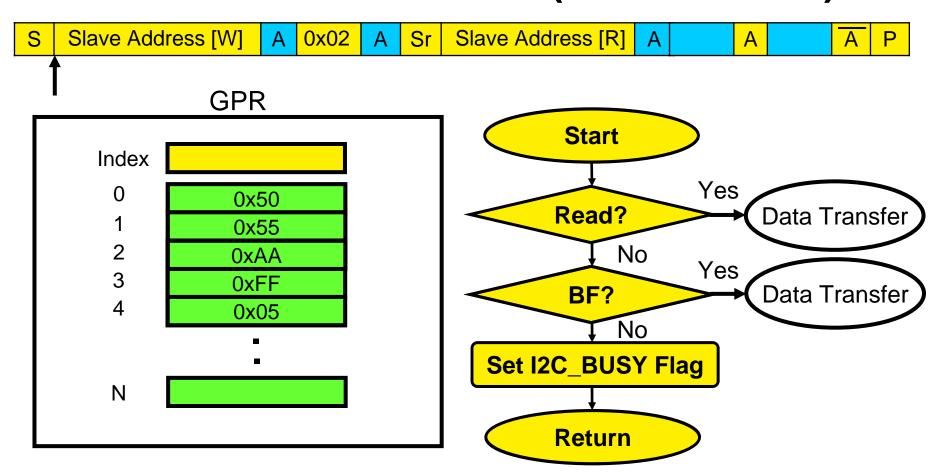

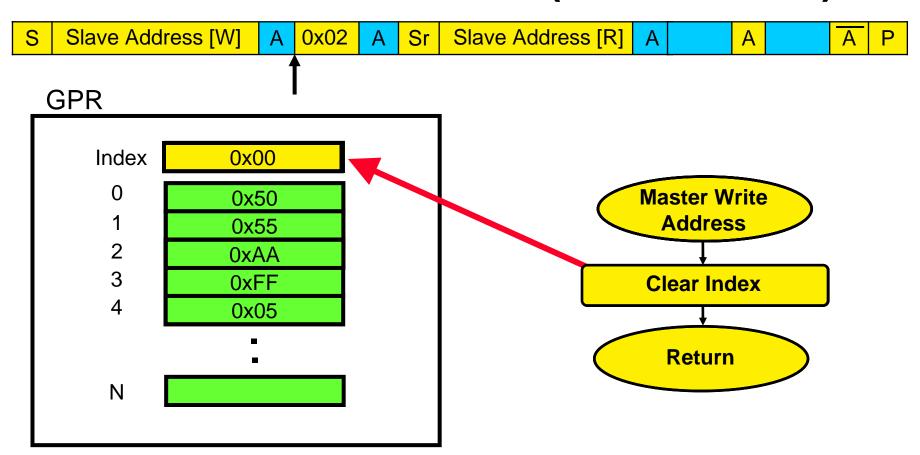

Master Write then Read (Combination)

Read two data bytes starting from word address (0x02)

### Summary

- Performs operations to GPRs

- Write Operation

- Read Operation

- MUST specify the word address

#### – Gotchas:

- SSPSTAT is updated during each interrupt event

- Interrupt events may occur before an event is serviced

# **Programming the MSSP**

### Summary

- Firmware Overview

- Events

- I<sup>2</sup>C<sup>™</sup> Slave State Machine

- **Master Write**

- Master Write then Read (Combination)

# Summary

- I<sup>2</sup>C<sup>TM</sup> Protocol Overview

- PICkit™ Serial Analyzer

- Configuring the MSSP peripheral for I<sup>2</sup>C slave mode

- Programming the MSSP peripheral as an I<sup>2</sup>C slave

# **Bonus Material**

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KeeLoq, KeeLoq logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A. All other trademarks mentioned herein are property of their respective companies.