### 11091 PS6

# Advanced SMPS Applications using the dsPIC® DSC SMPS Family

## **Class Objective**

#### When you finish this class you will:

- Understand design considerations for a High Power Converter

- Know how to implement digital control loops using the dsPIC<sup>®</sup> DSC

- Understand the benefits of Digital Power Conversion

- View a demonstration of the AC/DC Reference Design

### **Agenda**

- Overview of AC/DC Reference Design

- AC/DC Reference Design Architecture

- Power Factor Correction

- PFC Control Software

- Zero Voltage Transition

- ZVT Control Software

- Multi-phase Buck Converters

- Multi-phase Buck Control Software

- Enhanced Features

### **Agenda**

- Overview of AC/DC Reference Design

- AC/DC Reference Design Architecture

- Power Factor Correction

- PFC Control Software

- Zero Voltage Transition

- ZVT Control Software

- Multi-phase Buck Converters

- Multi-phase Buck Control Software

- Enhanced Features

## Overview of the **AC/DC** Reference Design

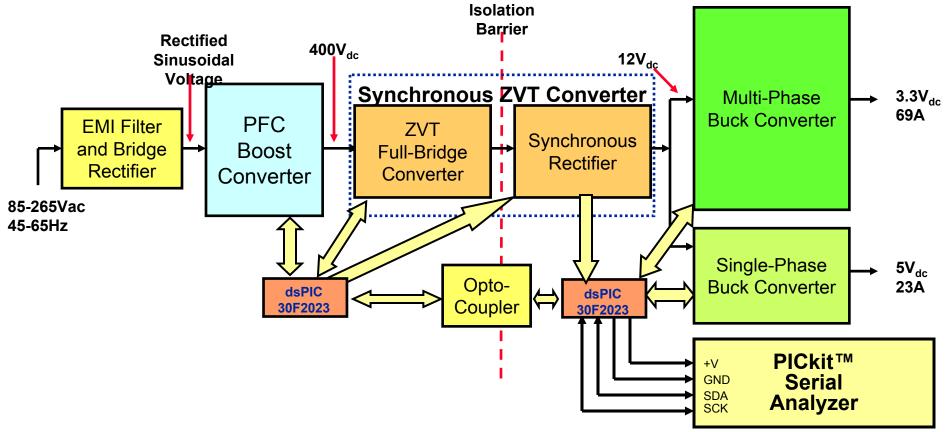

# Overview of AC/DC Reference Design

- Total Output Power Rating of 350 W

- Multiple DC Outputs:

- 3.3V, 69A (max)

- 5V, 23A (max)

- 12V, 28A (max)

- Universal Operating Voltage

- 85V 265V AC, 45-65 Hz

- Digital PFC Implementation

- PF > 0.98

#### Overview of AC/DC Reference Design

- Automatic Fault Handling

- Flexible Start-up Capability

- Remote Power Management Capability

- Full Digital Control

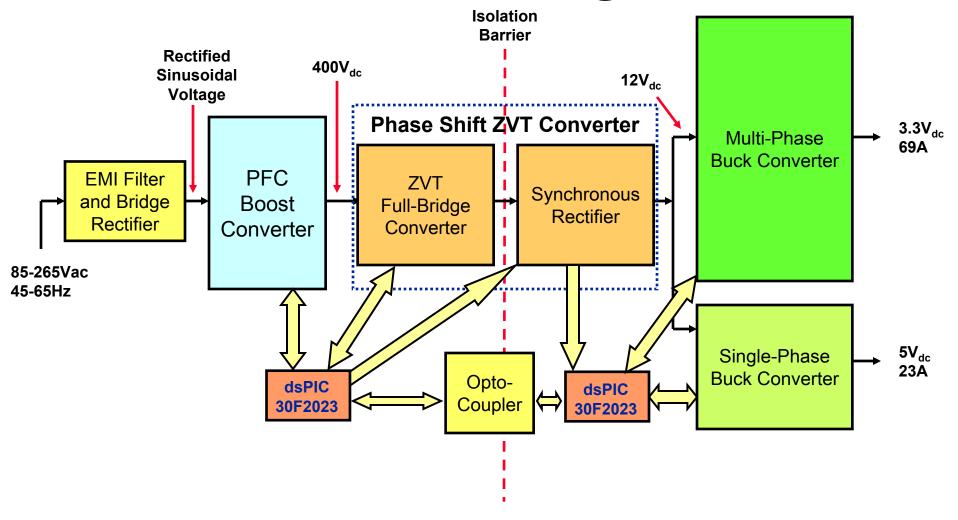

#### **AC/DC** Reference Design **Block Diagram**

#### dsPIC® DSC SMPS Features

- 30 MIPS MCU + DSP core

- Intelligent Power Peripherals

- High Speed A/D: 10-bit, 2 MSPS

- High Resolution PWM 1.05ns

- High Speed Analog Comparators

- Internal Fast RC oscillator + PLL

- Small footprint package 6 x 6 mm

- Flash-based controller

- CodeGuard™ Security Enabled

- Extended Temp (125°C) Operation

- Additional Information in 11089\_PS4

### **Agenda**

- Overview of AC/DC Reference Design

- AC/DC Reference Design Architecture

- Power Factor Correction

- PFC Control Software

- Zero Voltage Transition

- ZVT Control Software

- Multi-phase Buck Converters

- Multi-phase Buck Control Software

- Enhanced Features

## **AC/DC** Reference Design Architecture

# Considerations for Choice of Architecture

- Number of Stages

- Choice of PFC Topology

- Switching Methodology

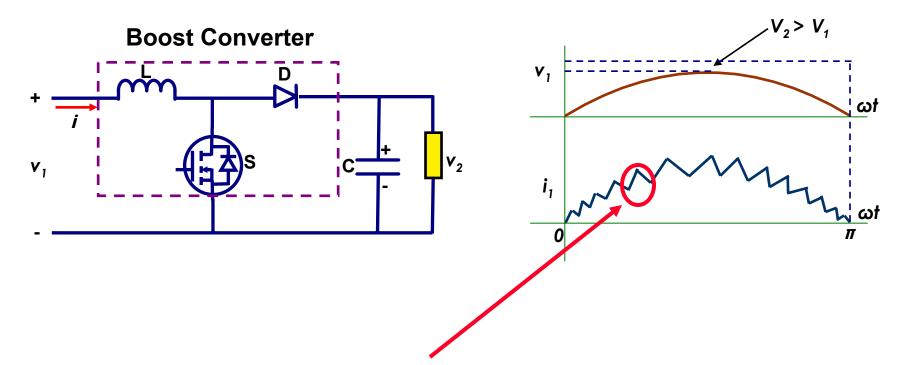

- Output Isolation requirements

- Requirements of Output Stage

# Considerations for Choice of Architecture

- Number of Stages

- Choice of PFC Topology

- Switching Methodology

- Output Isolation requirements

- Requirements of Output Stage

#### Multi-Stage Architecture

Multi-stage design simplifies design of each stage

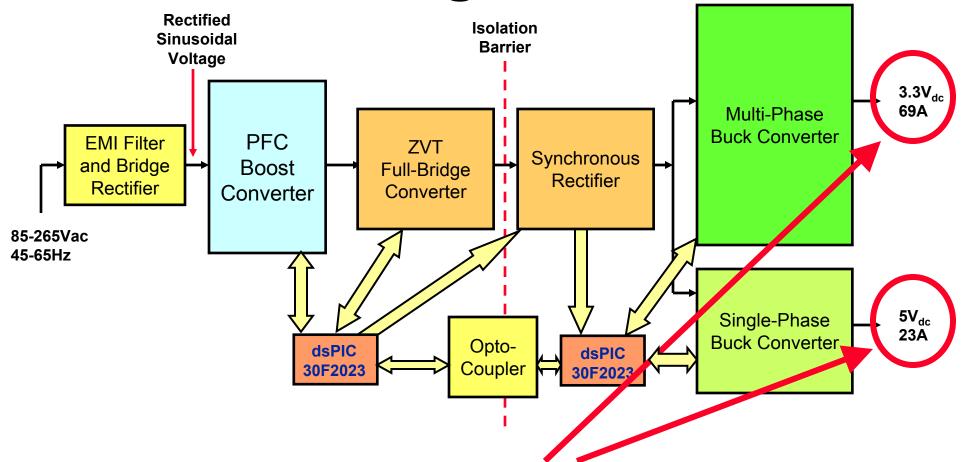

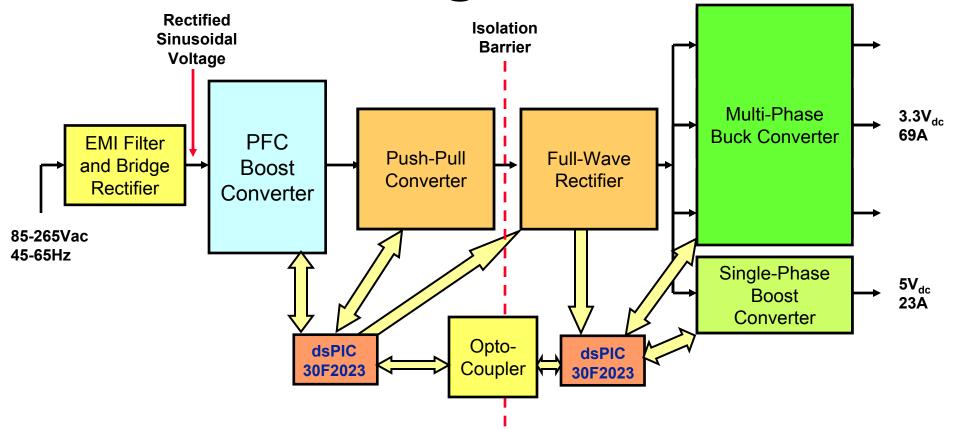

#### Multi-Stage Architecture

Multiple Outputs and multiple loads can be controlled Independently

#### **Multi-Stage Architecture**

Modular Architecture enables swapping of stages with dropin topologies

#### Considerations for Choice of **Architecture**

- Number of Stages

- Choice of PFC Topology

- Switching Methodology

- Output Isolation requirements

- Requirements of Output Stage

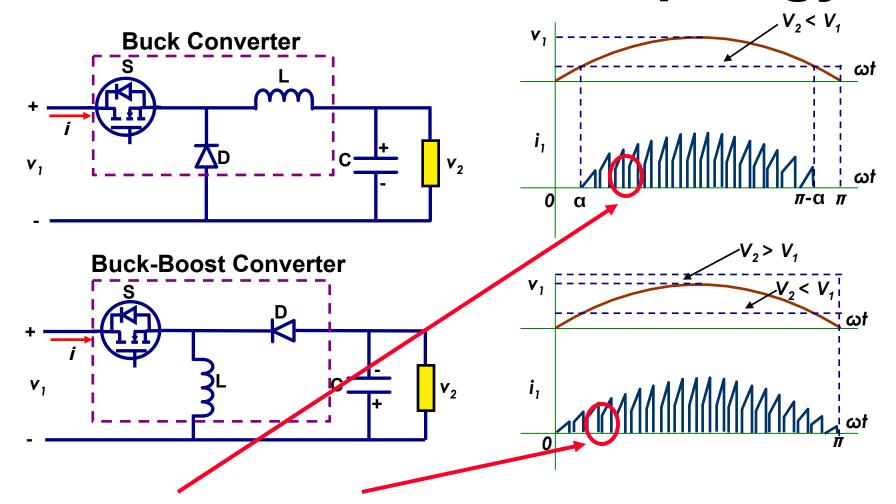

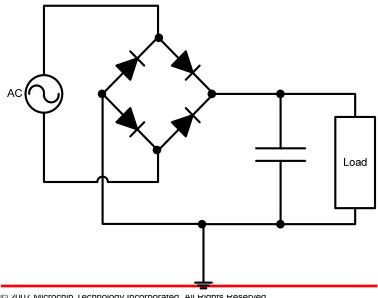

### Choice of PFC Topology

**Buck and Buck-Boost Topologies operate with discontinuous Current**

## Why PFC Boost Converter?

Boost Converter operates with continuous input current at high loads

# Considerations for Choice of Architecture

- Number of Stages

- Choice of PFC Topology

- Switching Methodology

- Output Isolation requirements

- Requirements of Output Stage

# Choice of Switching Methodology

| Hard Switching                                                        | Soft Switching                                                          |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------|

| Fixed Frequency Operation                                             | Variable/Fixed Frequency Operation                                      |

| Fewer Components Required                                             | More Components Required                                                |

| Simpler Control                                                       | Complex Control                                                         |

| High Switching Losses                                                 | Low Switching Losses                                                    |

| Used in Designs with Low<br>Power and Low Performance<br>Requirements | Used in Designs with High<br>Power and High Performance<br>Requirements |

# Considerations for Choice of Architecture

- Number of Stages

- Choice of PFC Topology

- Switching Methodology

- Output Isolation requirements

- Requirements of Output Stage

# Output Isolation and Safety Requirements

# Considerations for Choice of Architecture

- Number of Stages

- Choice of PFC Topology

- Switching Methodology

- Output Isolation requirements

- Requirements of Output Stage

#### **Output Stage Requirements**

Output Design Specifications determine Choice of Converter Topology

#### Summary

- Overview of AC/DC Reference Design

- Design Specifications

- Features of dsPIC® DSC SMPS Family

- AC/DC Reference Design Architecture

- Block Diagram

- Rationale Behind Chosen Architecture

### **Agenda**

- Overview of AC/DC Reference Design

- AC/DC Reference Design Architecture

- Power Factor Correction

- PFC Control Software

- Zero Voltage Transition

- ZVT Control Software

- Multi-phase Buck Converters

- Multi-phase Buck Control Software

- Enhanced Features

## **Power Factor** Correction

Additional Information Available in 11092\_PFC

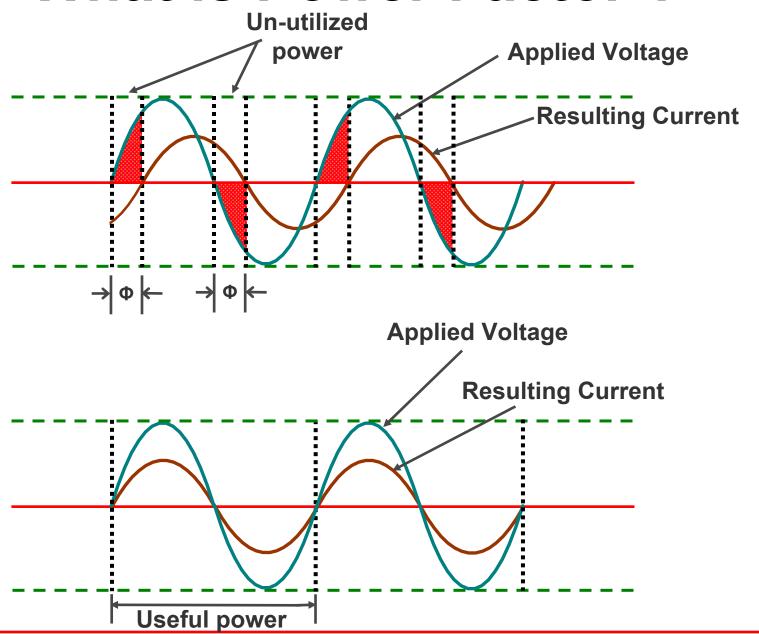

#### What is Power Factor?

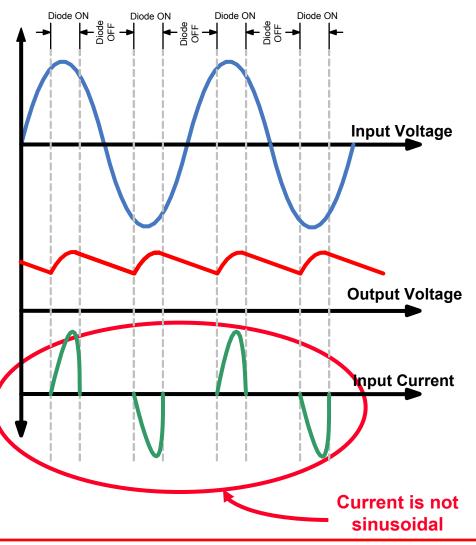

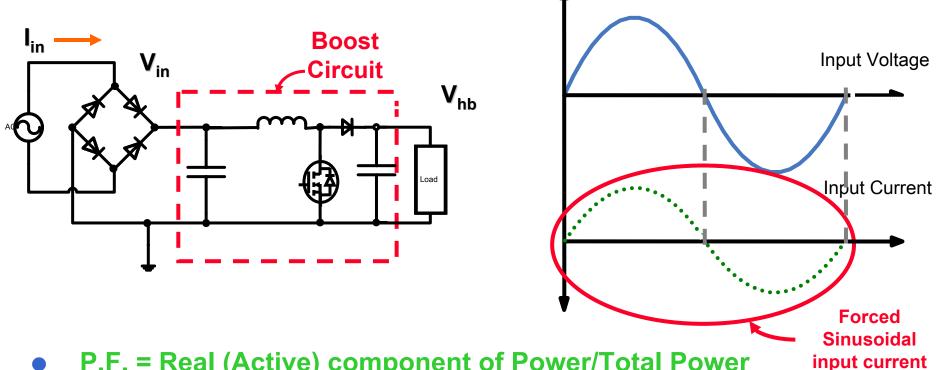

#### **Power Factor Correction**

- With no Power Factor **Correction, the input** current is highly distorted

- **Induces Noise in the Power Grid**

- **Higher current rating** device is required

#### **Power Factor Correction**

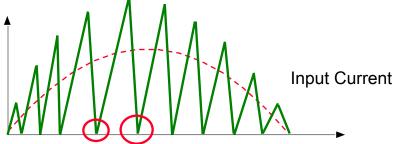

- P.F. = Real (Active) component of Power/Total Power

- Need to sense Vin, Inductor Current and V<sub>hb</sub>

- Maintains a Noise-free power grid

- Reduce rms and peak current required by the system

### Why is PFC needed?

- Reduce Peak Current Ratings

- Reduce Component Overheating

- Efficiently utilize available Power

- Comply with Regulations

- Avoid Penalties from Utility Company

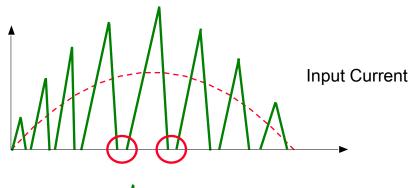

#### **Common PFC Methods**

Continuous Current Mode Input Current

Discontinuous Current Mode

Critical Conduction

Current Mode

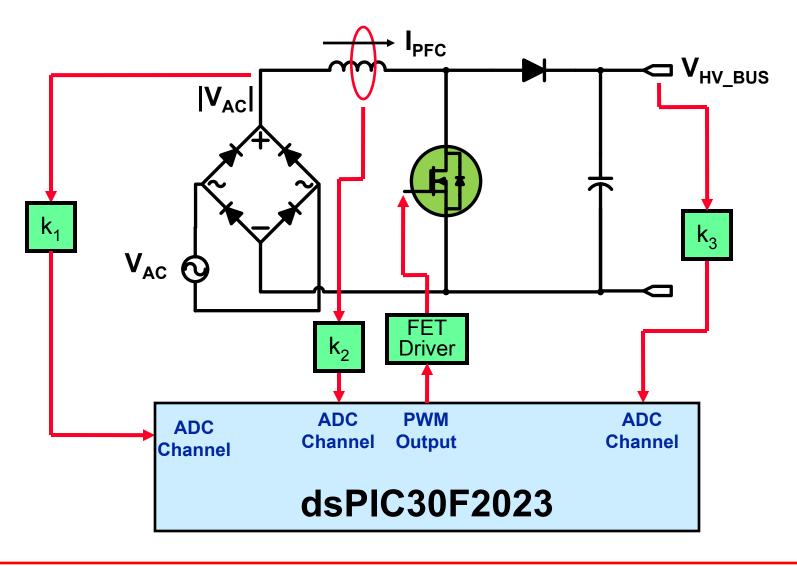

#### **PFC Boost Converter**

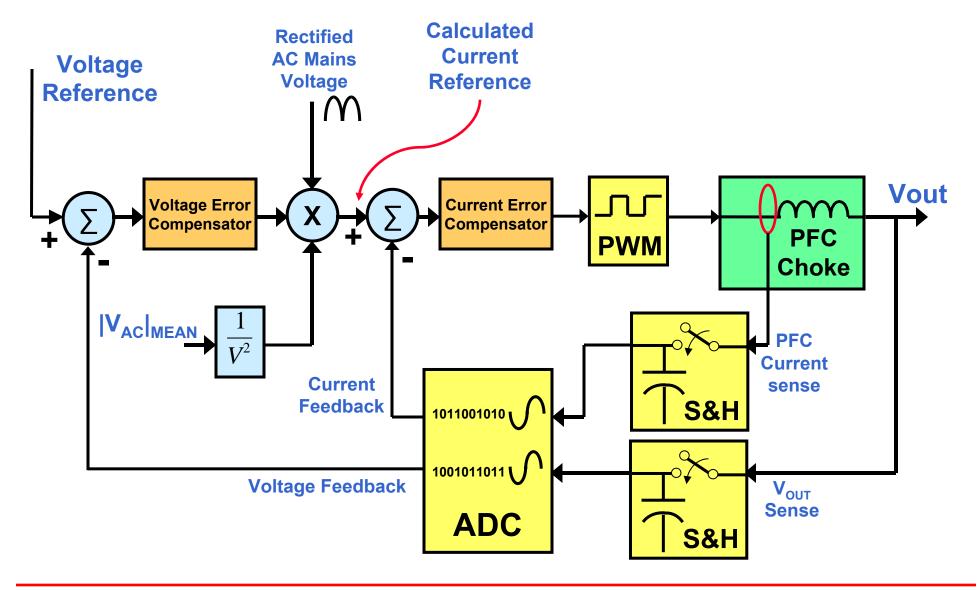

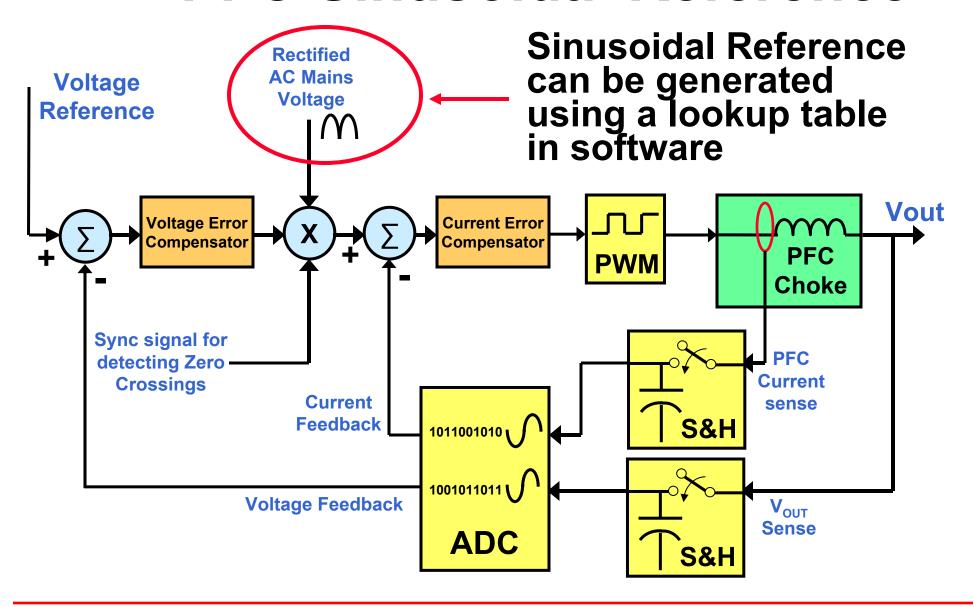

#### **PFC Control Scheme**

# Resources Required for Digital PFC

# **PFC Resource Allocation**

| Signal Name             | Type of Signal                | dsPIC® DSC<br>Resource Used        |

|-------------------------|-------------------------------|------------------------------------|

| V <sub>OUT</sub>        | Analog Input                  | AN5                                |

| I <sub>PFC</sub>        | Analog Input                  | AN4                                |

| V <sub>AC</sub>         | Analog Input                  | AN6                                |

| MOSFET Gate<br>Drive    | Drive Output                  | PWM4L                              |

| Current Loop<br>Trigger | dsPIC® DSC<br>Internal Signal | PWM4 Trigger to Sample PFC Current |

| Voltage Loop<br>Trigger | dsPIC® DSC<br>Internal Signal | Timer2                             |

# Agenda

- Overview of AC/DC Reference Design

- AC/DC Reference Design Architecture

- Power Factor Correction

- PFC Control Software

- Zero Voltage Transition

- ZVT Control Software

- Multi-phase Buck Converters

- Multi-phase Buck Control Software

- Enhanced Features

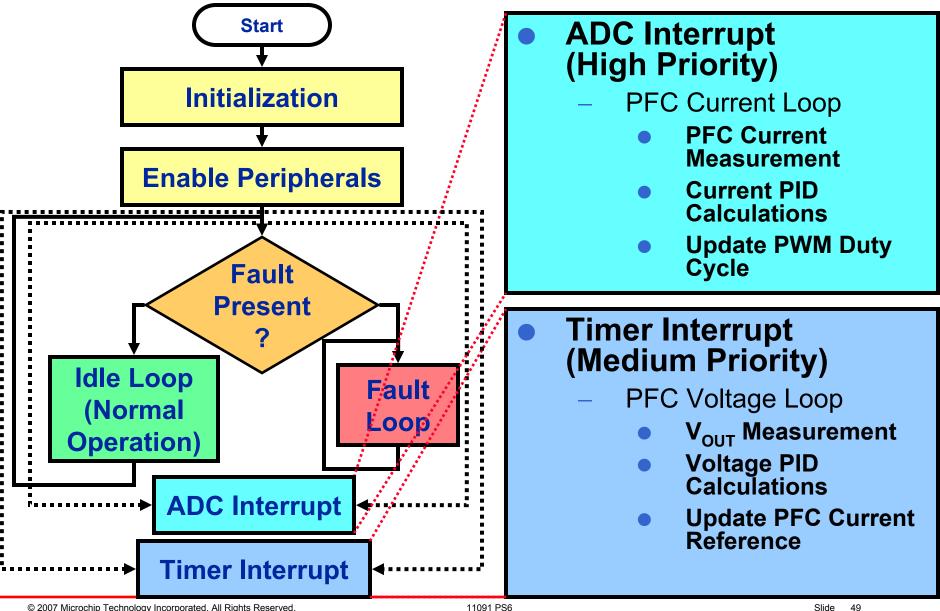

# **PFC Control Software**

### **PFC Software Overview**

- ADC Conversions are initiated by the PWM Trigger Feature

- The Current Control Loop is Executed in the ADC Interrupt Routine

- The Voltage Loop is Executed in a Timer Interrupt

- Faults are handled by the PWM Module using the on-chip Analog Comparators

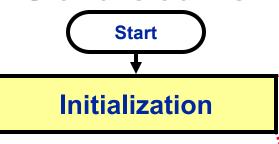

- Initialize PWM

- Initialize ADC

- **Setup Timer**

- Configure Interrupts

- **Initialize Control Loop Variables**

#### Initialize PWM

- Configure PWM Mode,

Output Polarity, Period,

initial Duty Cycle

- Setup PWM Faults and Fault Thresholds

- Setup PWM Triggers

**Initialization**

#### **Initialize ADC**

- Setup ADC Speed

- Configure desired ADC channels as analog inputs

- Choose ADC Trigger Sources

- Configure ADC Data **Format**

- **Choose Simultaneous** or Sequential Sampling

#### **Configure Timer**

Use Timer to trigger Voltage Control Loop

#### **Setup Interrupts**

- PWM Interrupt for **Fault Handling**

- ADC Interrupt to trigger Current **Control Loop**

- Timer Interrupt to trigger Voltage **Control Loop**

**Initialization**

- **Initialize Control Loop Variables**

- Initialize PID Gain Terms in X-memory

- Initialize Measured signals in Y-memory

- Initialize pointers to **Control Loop Inputs** and Outputs

# **Demonstration #1**

# **Digital Power Factor** Correction

# Agenda

- Overview of AC/DC Reference Design

- AC/DC Reference Design Architecture

- Power Factor Correction

- PFC Control Software

- Zero Voltage Transition

- ZVT Control Software

- Multi-phase Buck Converters

- Multi-phase Buck Control Software

- Enhanced Features

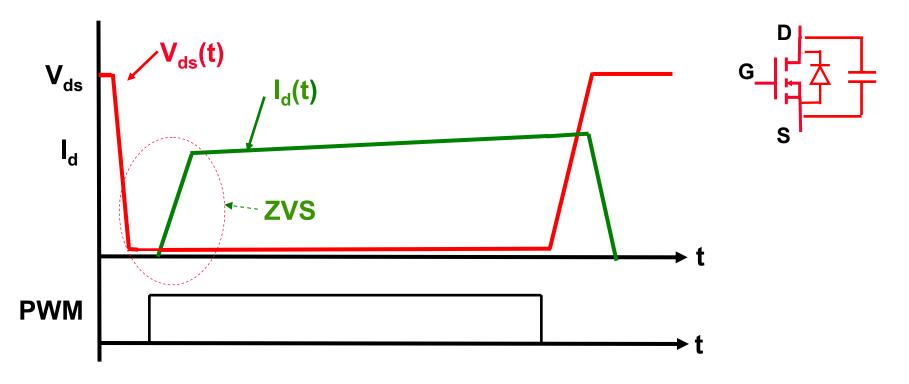

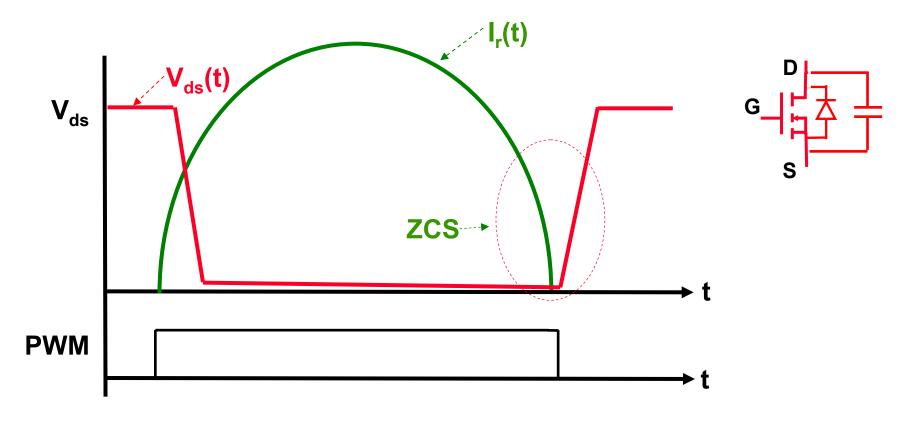

# Zero Voltage and Zero Current Switching

# Zero Voltage Switching

At transition period from one state to another state of the switch, the voltage is zero, hence no losses

# **Zero Current Switching**

At transition period from one state to another state of the switch, current is zero, hence no losses

# Switching Methodology

## Zero Current Switching:

- Eliminates V\*I losses in switching device during transitions

- Reduces Noise in the system hence better EMI performance

- Can be implemented at switch Turn ON as well as Turn OFF

- RMS Current through switch increases and therefore higher conduction losses

# Switching Methodology

## Zero Voltage Switching :

- Eliminates V\*I losses in switching device during transitions

- Reduces Noise in the system hence better EMI performance

- Eliminates MOSFET output capacitor (C<sub>oss</sub>) loss during switch Turn-ON

- Preferred in high voltage high power system

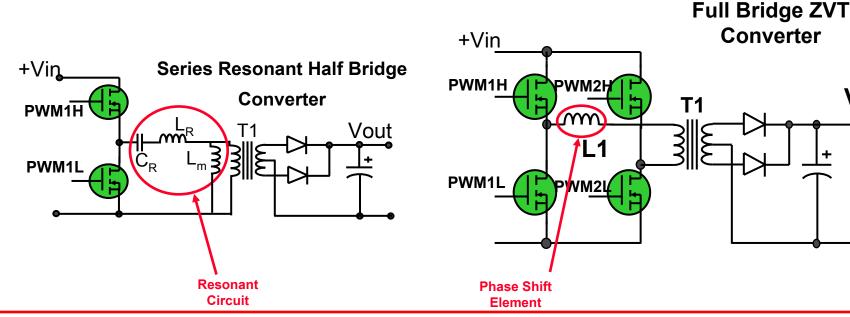

# Soft Switching Topologies

#### **Resonant Mode**

- SRC Series Resonant

- PRC Parallel Resonant

- LLC Resonant

#### **Zero Transition**

ZVT – Zero Voltage **Transition**

Vout

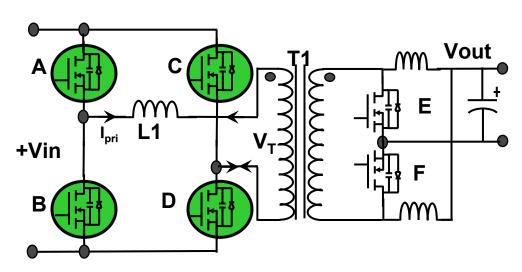

# Full-Bridge ZVT Converter

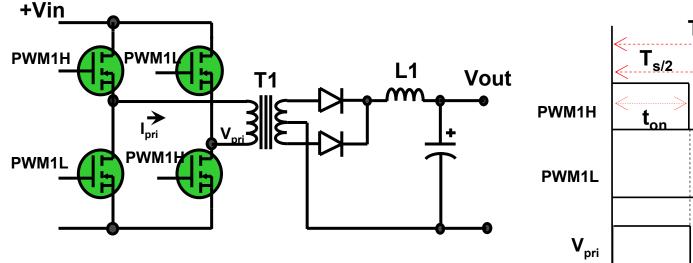

# **Full-Bridge Converter**

#### Full bridge converter

- Buck derived isolated converter

- Push Pull mode of PWM gate pulses

- Each half-bridge produces square wave voltage

- Duty cycle ratio controls the power flow

- Turn ON as well as Turn OFF losses in the MOSFET

- Popular for high power application

# Flux Walking

- Flux Walking small DC magnetic offsets add up over time to create magnetic saturation

- Flux Walking can be prevented by monitoring the current in both directions and making corrections if necessary

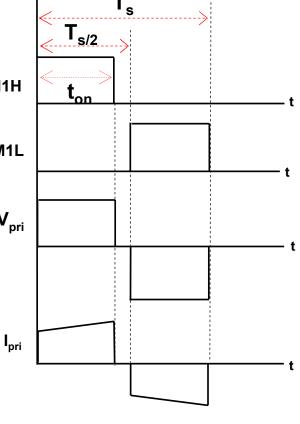

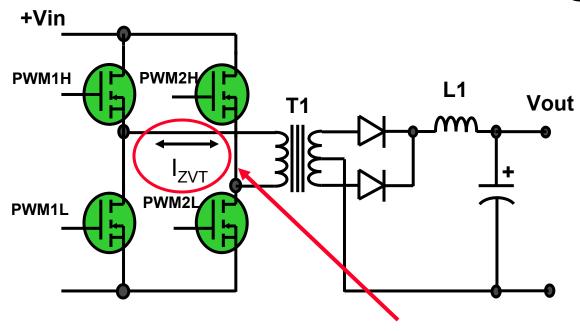

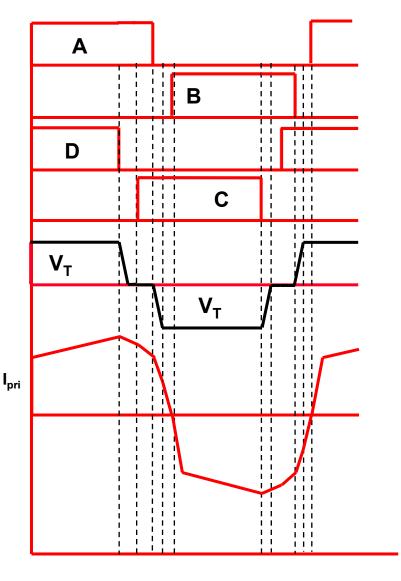

# Full-Bridge Phase Shift ZVT Converter

#### Full-bridge Phase Shift ZVT converter

- Complementary, fixed duty cycle PWM gate pulses

- Phase shift in gate pulse of two legs control the power flow

- Zero Voltage Switching, hence Turn ON losses in the MOSFET eliminates

- Parasitic of MOSFET and Transformer used to achieved ZVT

- A popular converter for very high power application

# Full-Bridge Phase Shift ZVT Converter

#### Right leg transition

- Terminates the power delivery interval

- Reflected load current is driving ZVS

- Transition is linear

- End of this period transformer primary is short circuited

#### Left leg transition

- Begins after freewheeling state to initiate the power delivery

- Energy stored in the inductor drives the ZVS

- Transition is resonant and non linear

# Full-Bridge Phase Shift ZVT Converter

- The right leg transition period is given by:

- Time required to charge and discharge the output capacitor of MOSFET C and MOSFET D

$$dt = C_r \cdot \frac{dv}{I_p}$$

- The left leg transition period is given by:

- Resonant time between L1 and output capacitor of MOSFET (A+B)

$$dt = \frac{\pi}{2} \cdot \sqrt{L1 \cdot C_r}$$

Where, dt = transition time

$I_p$  = primary current when the MOSFET D turns OFF

L1 = Leakage inductance of transformer

$C_r$  = equivalent capacitor of MOSFET two MOSFET and transformer parasitic capacitor ( $C_{xfmr}$ )

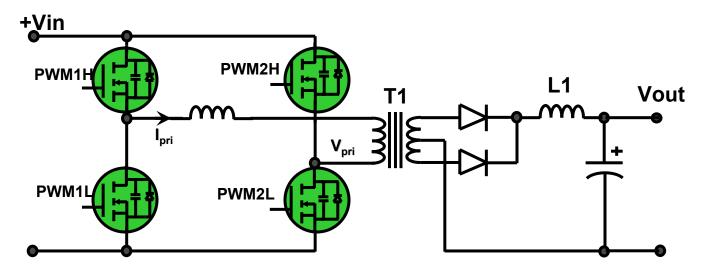

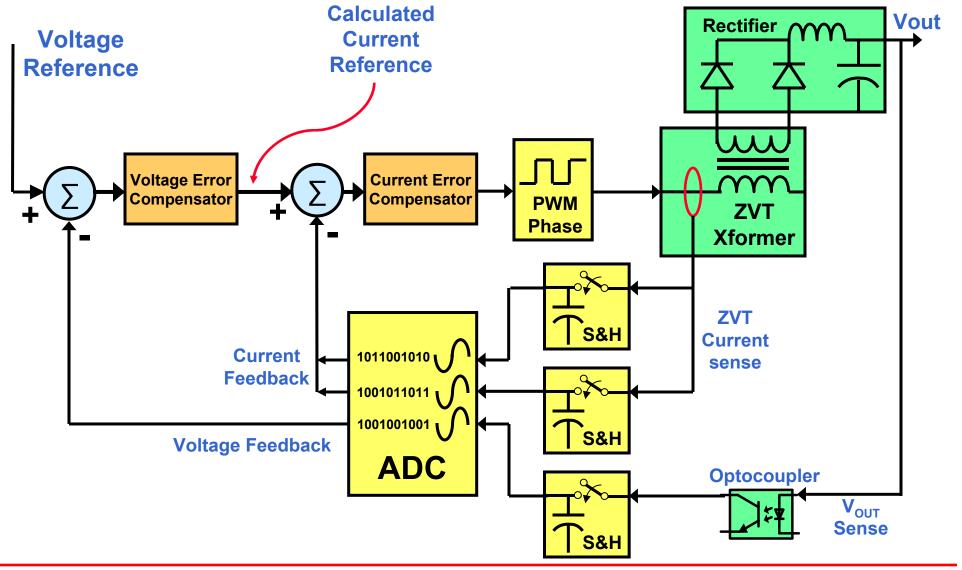

## **ZVT Control Scheme**

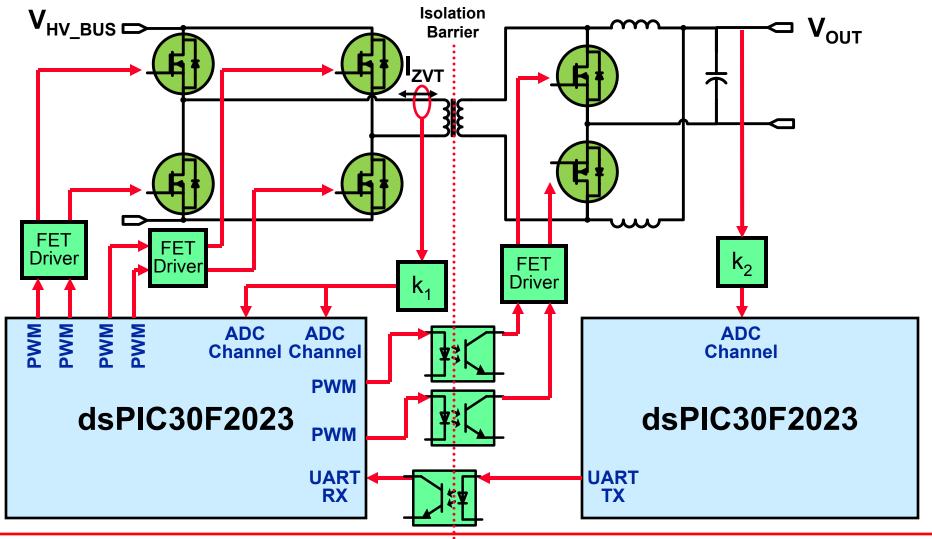

# Resources Required for Digital ZVT Converter

## **ZVT Resource Allocation**

| Signal Name                   | Type of Signal                            | dsPIC® DSC<br>Resource Used               |

|-------------------------------|-------------------------------------------|-------------------------------------------|

| l <sub>zvt1</sub>             | Analog Input                              | AN0                                       |

| l <sub>ZVT2</sub>             | Analog Input                              | AN2                                       |

| V <sub>out</sub>              | UART Input                                | U1RX                                      |

| ZVT Gate Drive                | Drive Outputs                             | PWM1H, PWM1L<br>PWM2H, PWM2L              |

| Sync. Rectifier<br>Gate Drive | Drive Outputs                             | PWM3H, PWM3L                              |

| Current Loop<br>Trigger       | dsPIC <sup>®</sup> DSC<br>Internal Signal | PWM1, PWM2 Triggers to Sample ZVT Current |

| Voltage Loop<br>Trigger       | dsPIC <sup>®</sup> DSC<br>Internal Signal | UART1                                     |

# Agenda

- Overview of AC/DC Reference Design

- AC/DC Reference Design Architecture

- Power Factor Correction

- PFC Control Software

- Zero Voltage Transition

- ZVT Control Software

- Multi-phase Buck Converters

- Multi-phase Buck Control Software

- Enhanced Features

# **ZVT Control Software**

## **ZVT Software Overview**

- ADC Conversions are initiated by the **PWM Trigger Feature**

- The Current Control Loop is Executed in the ADC Interrupt Routine

- Additional Check for Transformer Primary Current Balance to prevent Flux Walking

- The Voltage Loop is Executed from a **UART Receive Interrupt**

- Faults are handled by the PWM Module using the on-chip Analog Comparators

### Structure of the ZVT Software

- Initialize PWM

- Initialize ADC

- Setup Timers

- Setup UART

- Configure Interrupts

- Initialize Control Loop Variables

### Structure of the ZVT Software

**Initialization**

#### **Initialize PWM**

- Configure PWM Mode, Output Polarity, Period, **Duty Cycle and** Phase Shift

- Setup PWM Faults and Fault **Thresholds**

- Setup PWM **Triggers**

### Structure of the ZVT Software

**Initialization**

#### Initialize ADC

- Setup ADC Speed

- Configure desired ADC channels as analog inputs

- Choose ADC Trigger

Sources

- Configure ADC Data Format

- Choose Simultaneous or Sequential Sampling

**Initialization**

### Configure Timers

Use Timer to trigger Voltage Control Loop

### Configure UART

Use UART to receive V<sub>OUT</sub> feedback signal

### Setup Interrupts

- PWM Interrupt for Fault Handling

- Timer Interrupt to trigger Voltage Control Loop

- ADC Interrupt to trigger Current Control Loop

- UART Receive Interrupt to Execute the Voltage Loop

**Initialization**

- **Initialize Control Loop Variables**

- Initialize PID Gain Terms in X-memory

- Initialize Measured signals in Y-memory

- Initialize pointers to **Control Loop Inputs** and Outputs

# **Additional Guidelines** for Primary side dsPIC® DSC Software

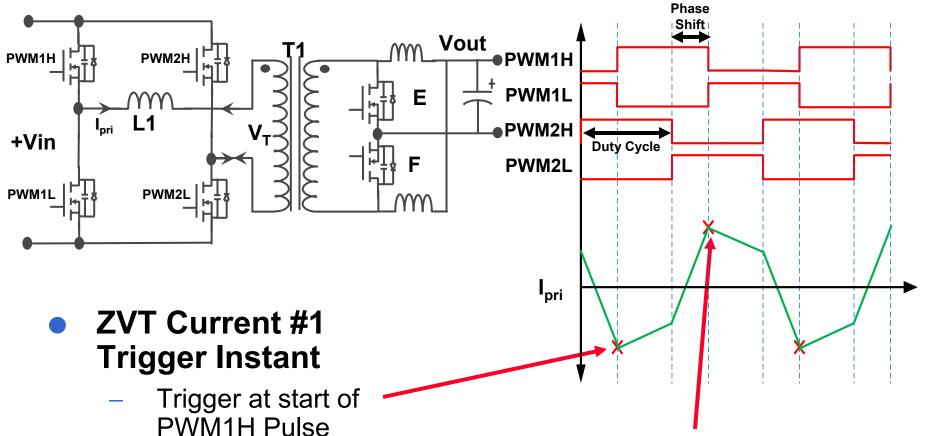

## Full-Bridge Phase Shift ZVT Converter

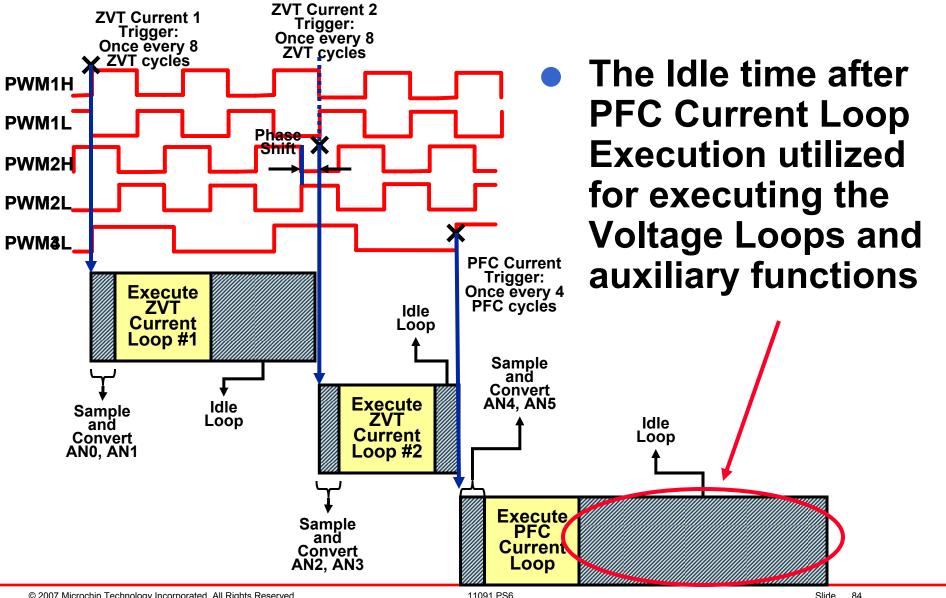

- **ZVT Current #2 Trigger Instant**

- Trigger on PWM2H at (Duty Cycle + Phase Shift)

**Sequence of Current Loop Triggers**

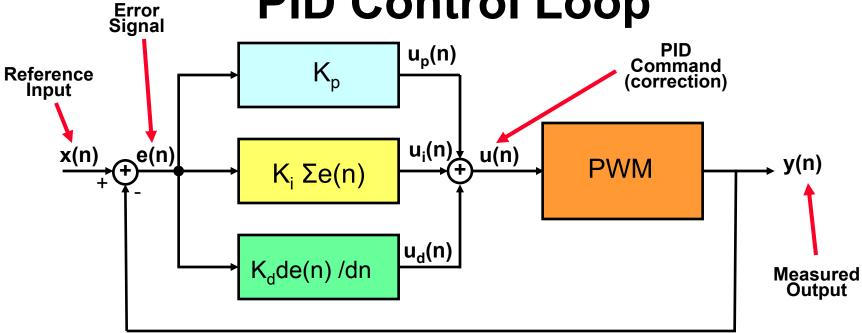

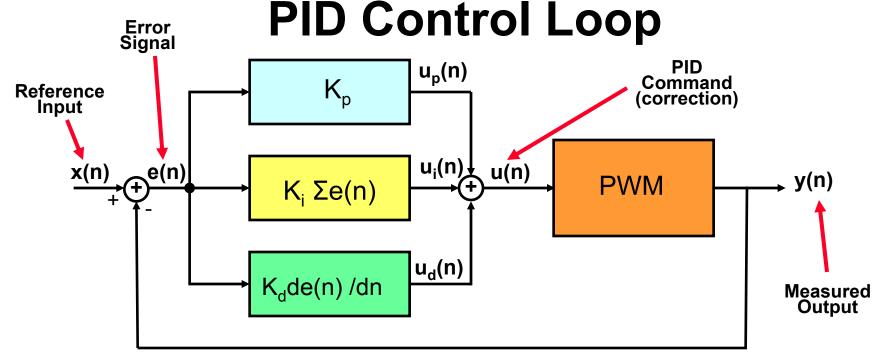

# Control Loop Execution PID Control Loop

$$u(n) = u_p(n) + u_i(n) + u_d(n)$$

where,

$u_p(n) = K_p^*e(n)$

$u_i(n) = K_i^*[e(n) + e(n-1)]$

$u_d(n) = K_d^*[e(n) - e(n-1)]$

85

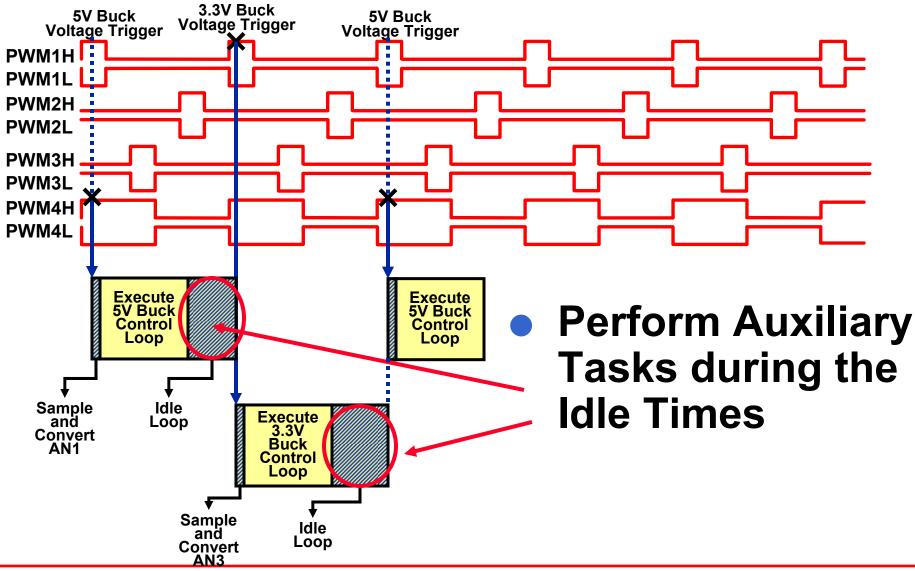

## **Auxillary Tasks**

- AC Input Voltage Measurement

- Check if Soft Start is required

- Temperature Measurement

- Communication Routines

## **Demonstration #2**

**ZVT** Operation

## **Summary**

### Power Factor Correction

- Overview of PFC

- Control Scheme for Digital PFC

- Structure of Control Software

## Zero Voltage Transition

- ZVS and ZCS and Full-Bridge Converter

- ZVT Phase Shift Converter

- Control Scheme for ZVT Converter

- Structure of Control Software

### Additional Guidelines for Primary Side dsPIC® DSC Control Software

## Agenda

- Overview of AC/DC Reference Design

- AC/DC Reference Design Architecture

- Power Factor Correction

- PFC Control Software

- Zero Voltage Transition

- ZVT Control Software

- Multi-phase Buck Converters

- Multi-phase Buck Control Software

- Enhanced Features

## **Multi-Phase Buck** Converter

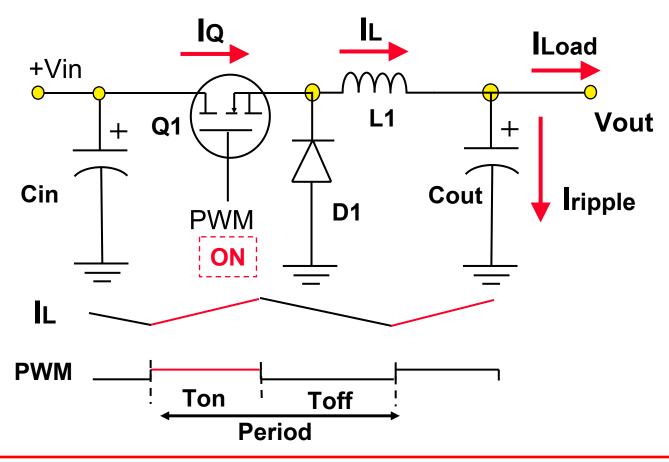

# Basic Theory of a Buck Converter

### Step down converter

**Charging inductor**

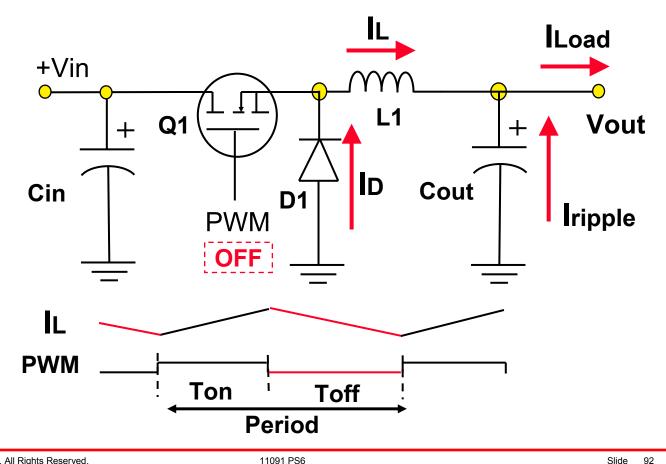

# Basic Theory of a Buck Converter

### Step down converter

### **Discharging inductor**

## PWM Pulse Width vs. **Buck Output Voltage**

Vout = Vin • D

### Where:

D = PWM dutycycle = Ton / (Ton +Toff)

Note: range of duty cycle = 0 to 1

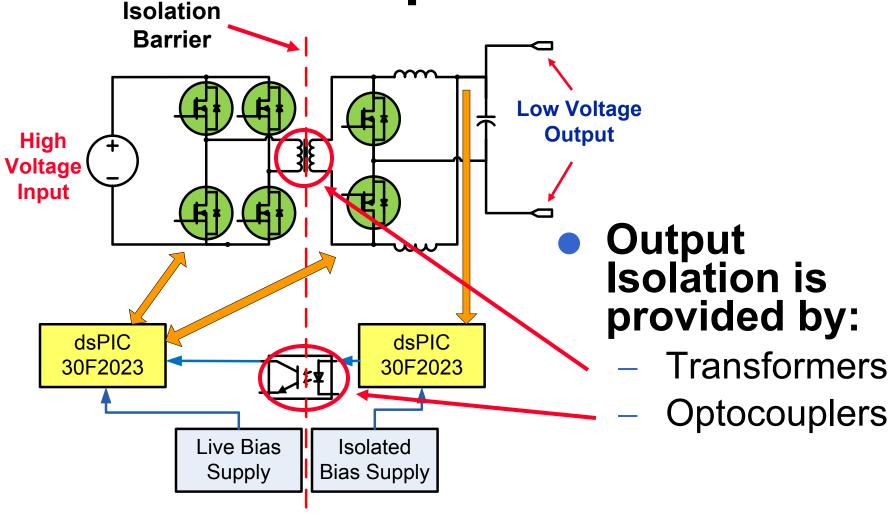

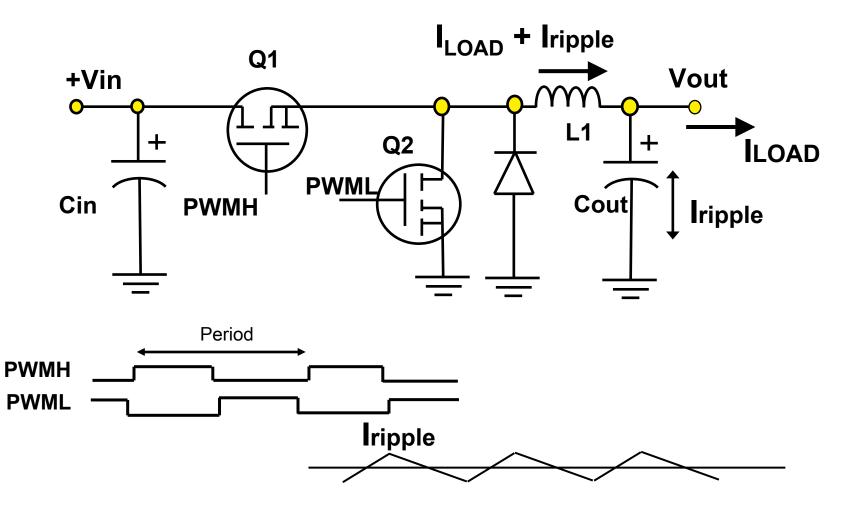

# Synchronous Buck Converter

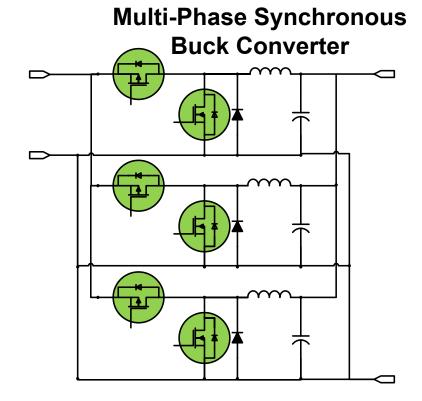

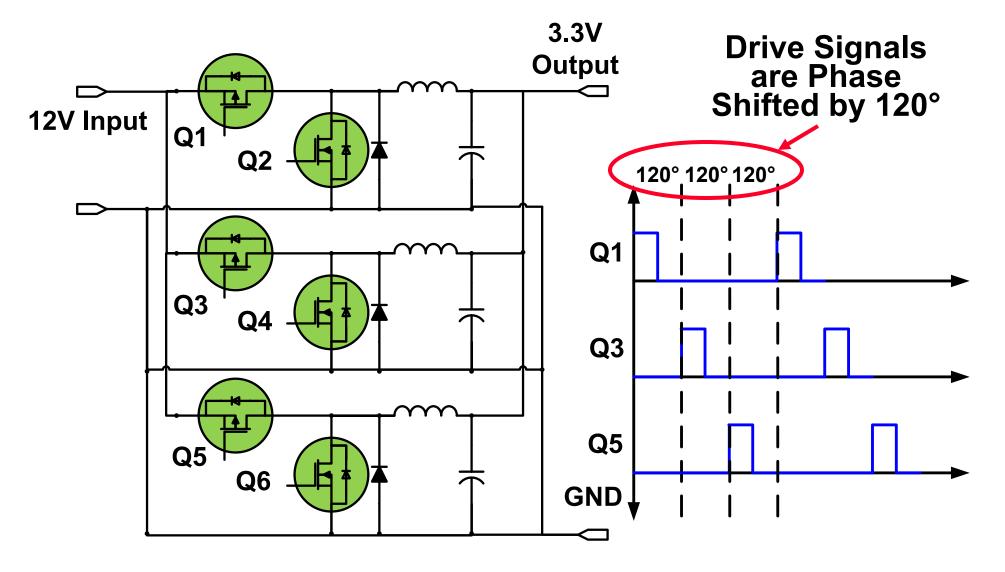

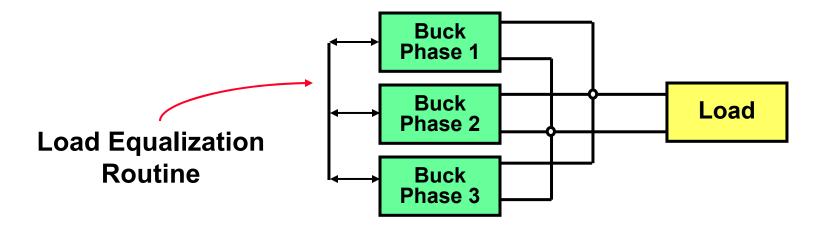

## Multi-Phase Buck Converter

# Why the Multi-phase Buck Converter?

- Each Phase is rated for less Power

- Semiconductor Devices have lower current rating

- Smaller MOSFETs usually mean better switching speed

- Higher Output Ripple Frequency decreases size of output filter

- Ripple magnitude is reduced

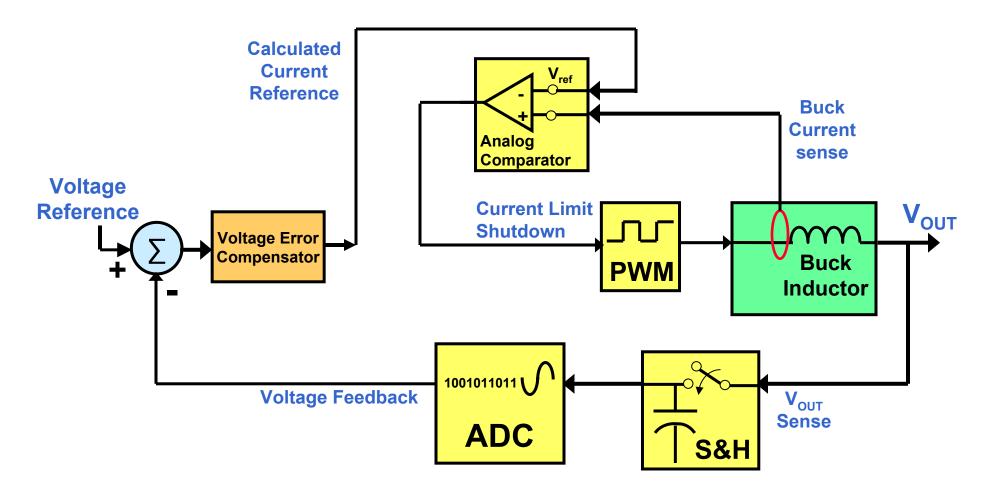

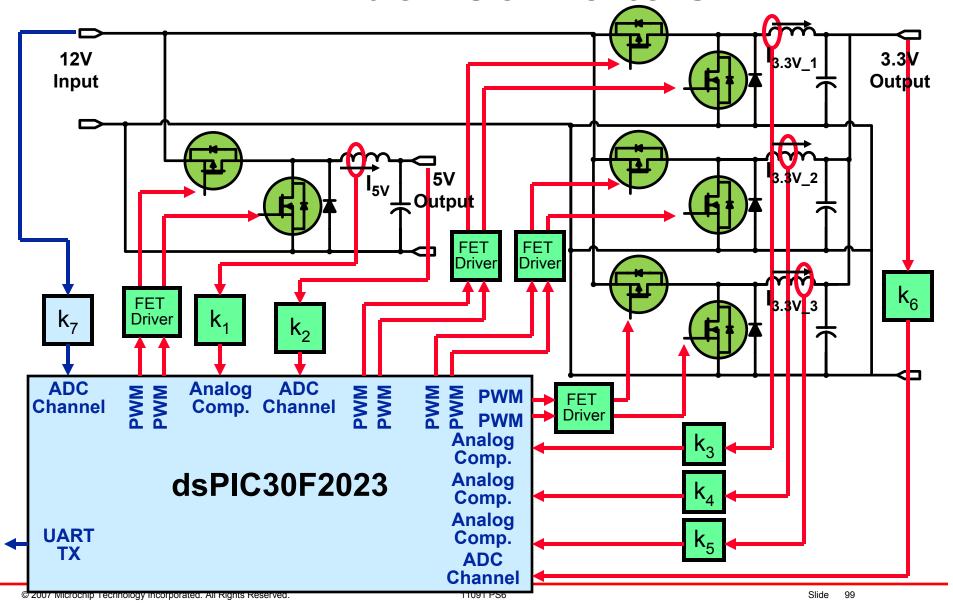

## 5V Buck Converter Control Scheme

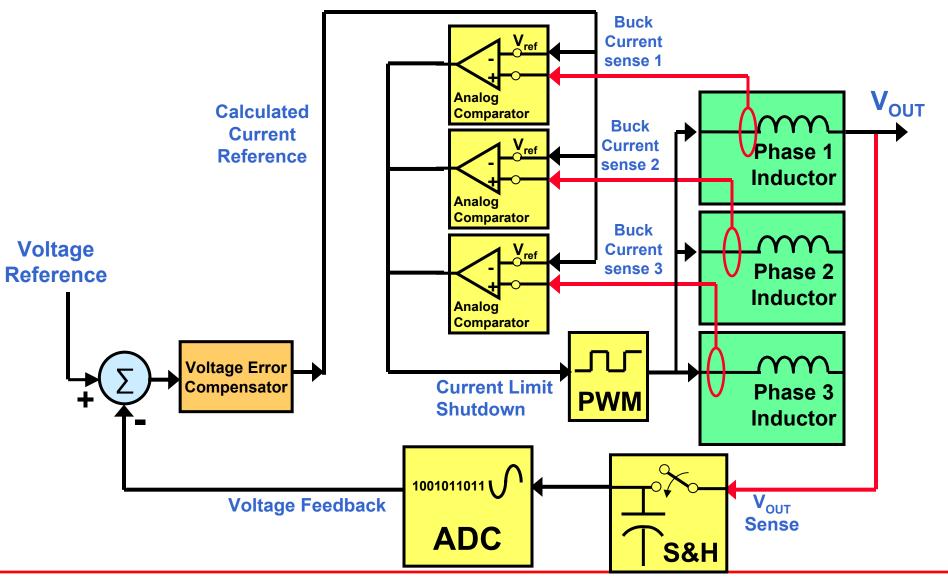

## 3.3V Buck Converter Control Scheme

# Resources Required for Digital Buck Converters

## **Buck Converters Resource Allocation**

| Signal Name           | Type of Signal | dsPIC® DSC<br>Resource Used |

|-----------------------|----------------|-----------------------------|

| l <sub>5V</sub>       | Analog Input   | CMP1A                       |

| 5V Output             | Analog Input   | AN1                         |

| I <sub>3.3V_1</sub>   | Analog Input   | CMP2A                       |

| I <sub>3.3V_2</sub>   | Analog Input   | CMP3A                       |

| I <sub>3.3V_3</sub>   | Analog Input   | CMP4A                       |

| 3.3V Output           | Analog Input   | AN3                         |

| 5V Buck Gate<br>Drive | Drive Outputs  | PWM4H, PWM4L                |

# **Buck Converters Resource Allocation**

| Signal Name                  | Type of Signal                | dsPIC® DSC<br>Resource Used                  |

|------------------------------|-------------------------------|----------------------------------------------|

| 3.3V Buck Gate<br>Drive      | Drive Outputs                 | PWM1H, PWM1L<br>PWM2H, PWM2L<br>PWM3H, PWM3L |

| 5V Current Loop<br>Trigger   | dsPIC® DSC<br>Internal Signal | PWM4 Trigger to Sample<br>5V Buck Voltage    |

| 3.3V Current Loop<br>Trigger | dsPIC® DSC<br>Internal Signal | PWM1 Trigger to Sample 3.3V Buck Voltage     |

| 12V Bus Sense                | Analog Input                  | AN5                                          |

| 12V Digital<br>Feedback      | UART<br>Transmission          | U1TX                                         |

| Temperature<br>Sense         | Analog Input                  | AN8                                          |

## **Agenda**

- Overview of AC/DC Reference Design

- AC/DC Reference Design Architecture

- Power Factor Correction

- PFC Control Software

- Zero Voltage Transition

- ZVT Control Software

- Multi-phase Buck Converters

- Multi-phase Buck Control Software

- Enhanced Features

# Multi-Phase Buck Converter Control Software

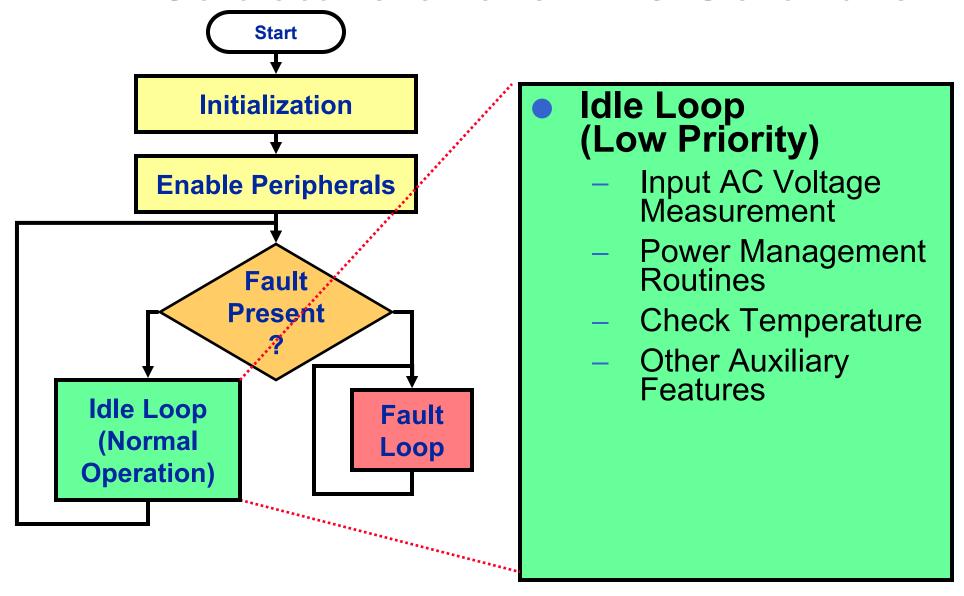

# Multi-Phase Buck Converter Software Overview

- ADC Conversions are initiated by the PWM Trigger Feature

- Peak Current Control is implemented using the Analog Comparators

- Additional Check Desired for Current Imbalance between the three phases

- The Voltage and Current Loops are executed at the same speed

- The UART Transmission for 12V digital feedback is executed from a Timer Interrupt

**Initialization**

- Initialize PWM

- Initialize ADC

- Initialize Analog Comparators

- Setup Timers

- Configure UART

- Configure Interrupts

- Initialize Control Loop Variables

**Initialization**

### Initialize PWM

- Configure PWM Mode,

Output Polarity, Period,

Duty Cycle and Phase

Shift

- Setup PWM Current Limit Sources

- Setup PWM Triggers

Initialization

### Initialize ADC

- Setup ADC Speed

- Configure desired ADC channels as analog inputs

- Choose ADC Trigger

Sources

- Configure ADC Data Format

- Choose Simultaneous or Sequential Sampling

**Initialization**

### Initialize Analog Comparators

- Configure Correct

Analog Comparator

Inputs

- Choose Voltage

Reference Source

- Setup Initial DAC Reference

- Choose Comparator Output Polarity

**Initialization**

#### **Configure UART**

Use UART to transmit 12V Bus Data to Primary Side dsPIC® DSC

#### Setup Interrupts

- PWM Interrupt for Fault Handling

- Timer Interrupt to trigger

Voltage Control Loop

- ADC Interrupt to trigger Current Control Loop

**Initialization**

- Initialize Control Loop Variables

- Initialize PID Gain

Terms in X-memory

- Initialize Measured signals in Y-memory

- Initialize pointers to Control Loop Inputs and Outputs

Initialization

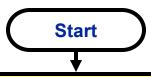

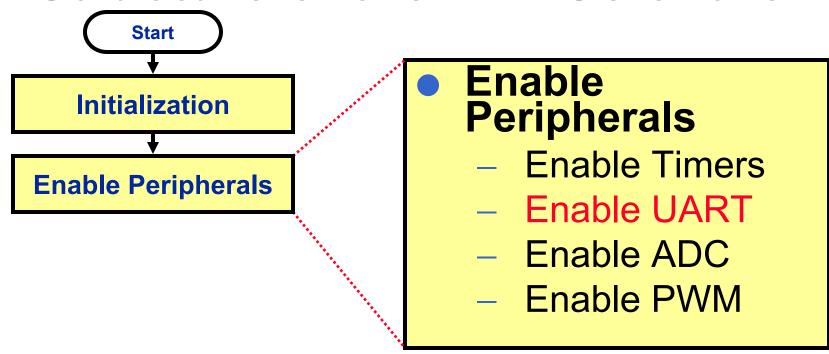

Enable Peripherals

Enable Peripherals

- Enable Analog

Comparators

- Enable ADC

- Enable PWM

- Enable UART

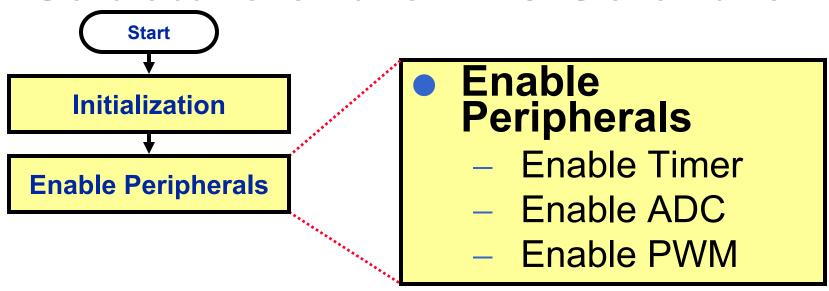

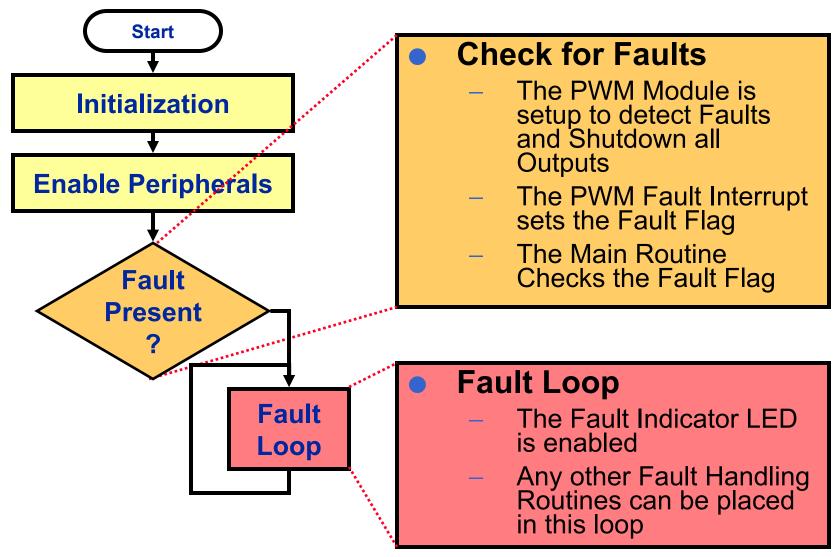

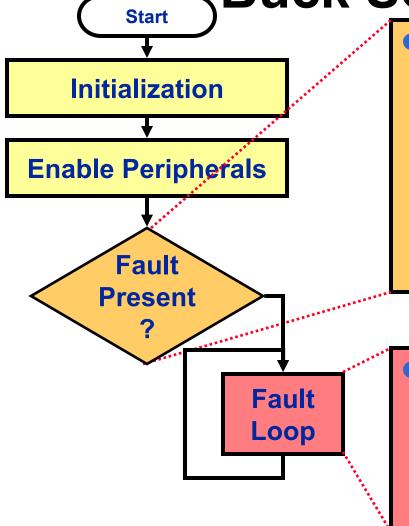

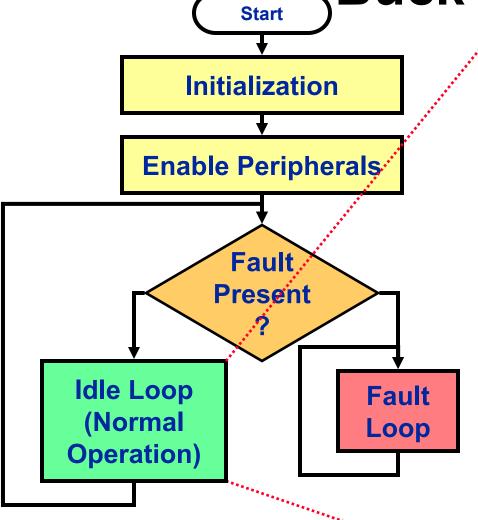

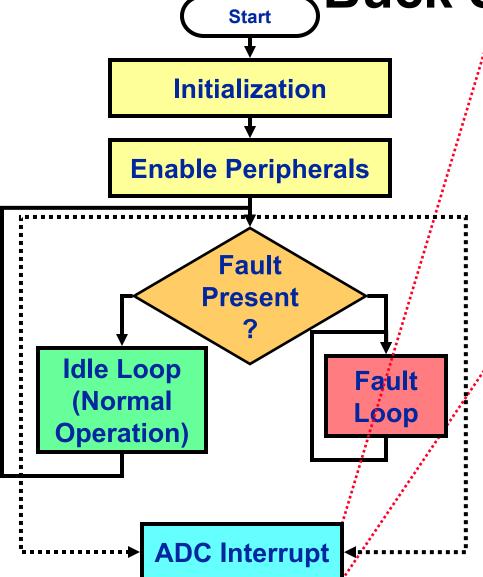

Check for Faults

- The PWM Module is setup to detect Faults and Shutdown all Outputs

- The PWM Fault Interrupt sets the Fault Flag

- The Main Routine Checks the Fault Flag

#### Fault Loop

- The Fault Indicator LED is enabled

- Any other Fault Handling Routines can be placed in this loop

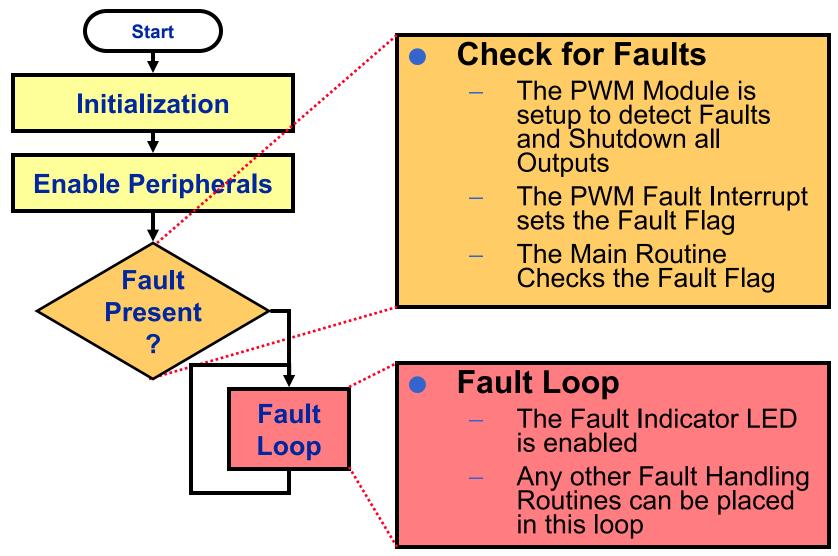

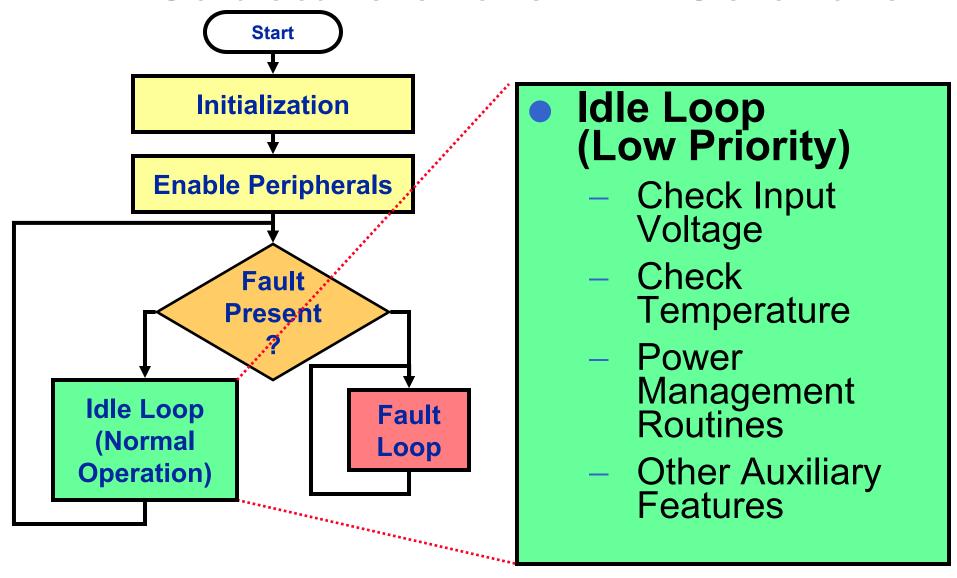

- Idle Loop (Low Priority)

- Transmit 12V Bus Data

- PowerManagementRoutines

- CheckTemperature

- Other AuxiliaryFeatures

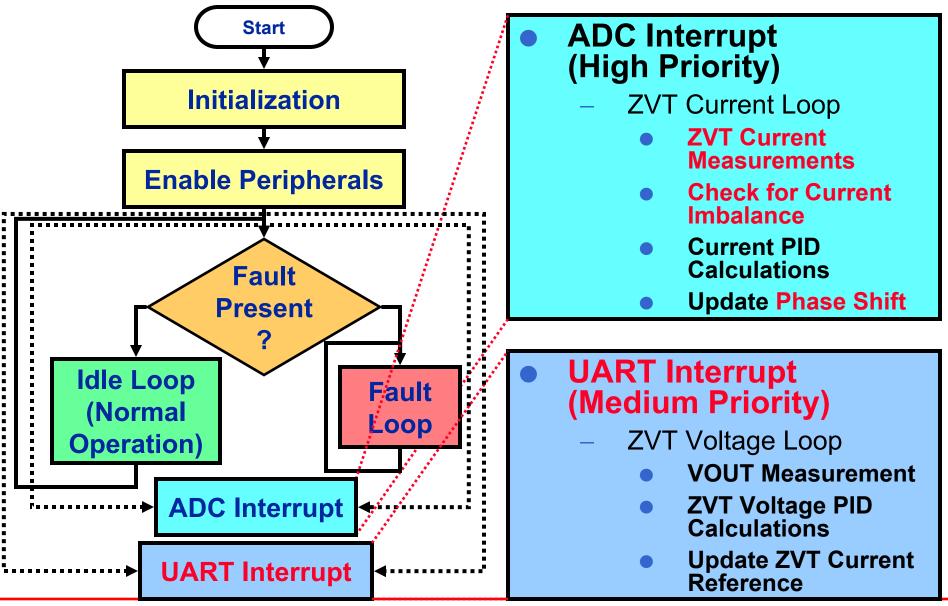

- ADC Interrupt (High Priority)

- Buck Current Loop

- V<sub>OUT</sub> Measurement

- Calculate Current Reference

- Update Analog

Comparator DAC

References

**Start** Initialization **Enable Peripherals Fault Present Idle Loop** Fault (Normal Loop **Operation**) **ADC Interrupt** Timer Interrupt

- ADC Interrupt (High Priority)

- Buck Current Loop

- **V<sub>OUT</sub> Measurement**

- Calculate Current Reference

- Update Analog

Comparator DAC

References

- Timer Interrupt (Medium Priority)

- Buck Voltage Loop

- Transmit 12V Digital Feedback Signal

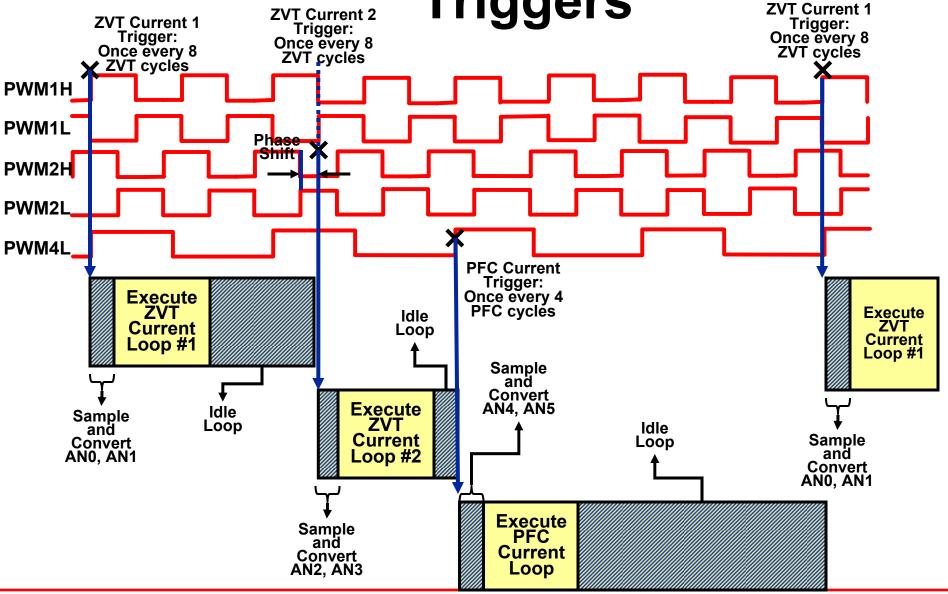

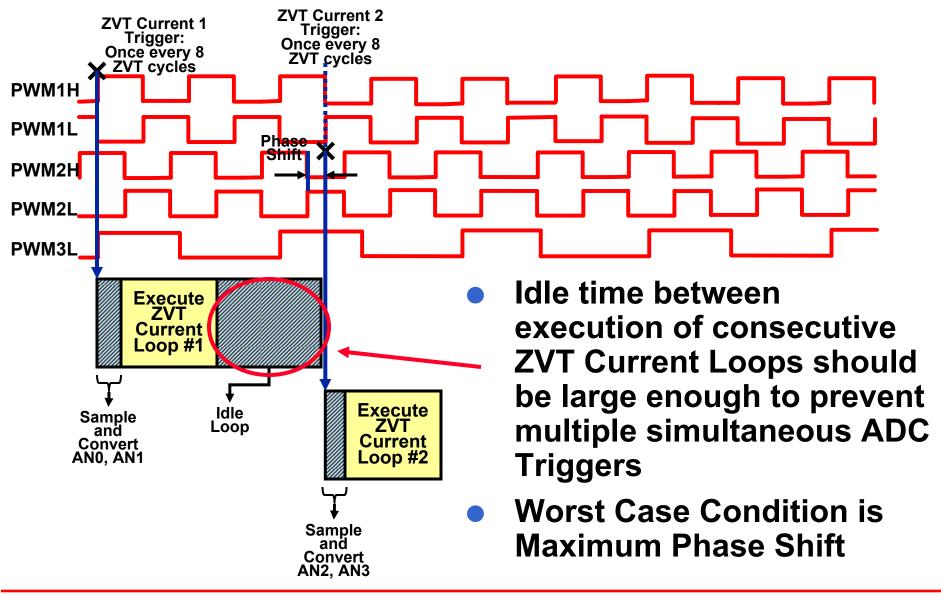

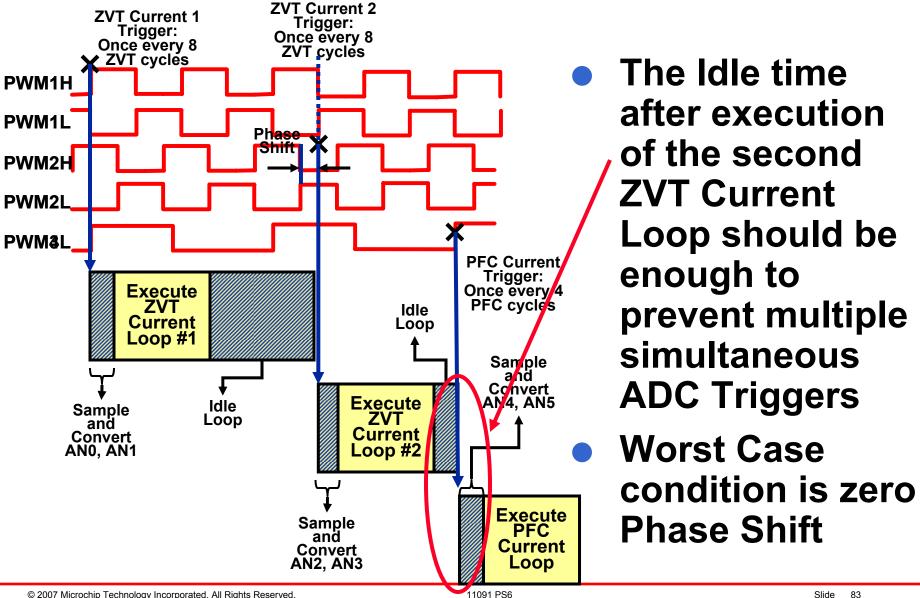

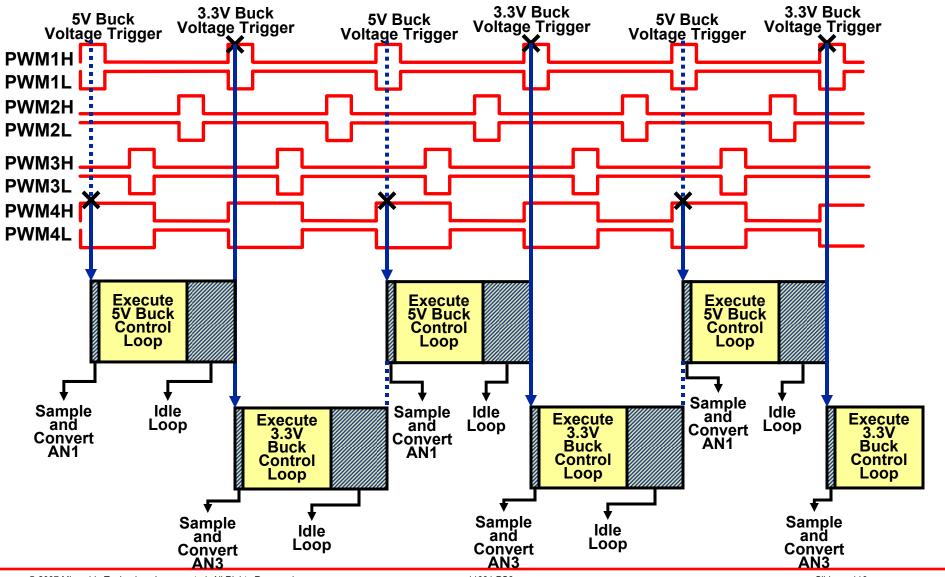

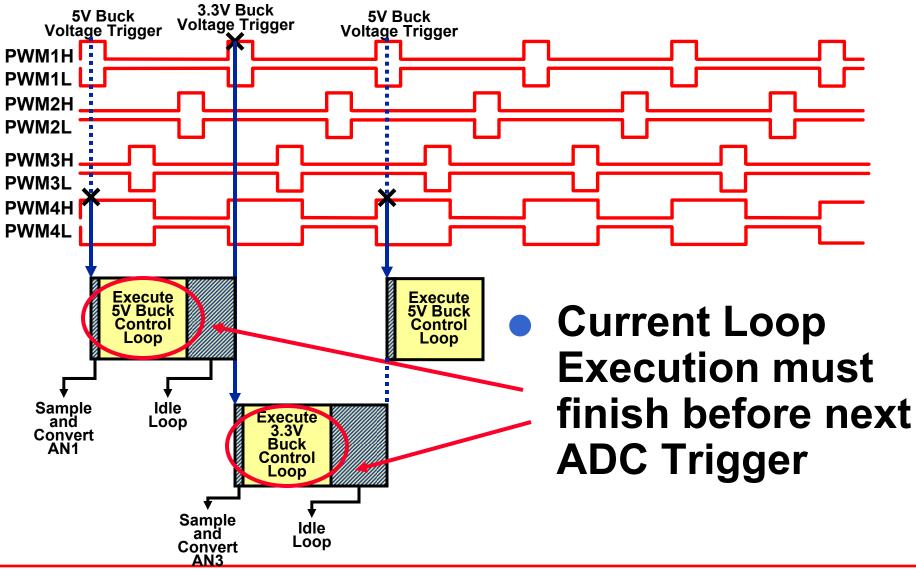

#### Sequence of Current Loop Triggers

#### Sequence of Current Loop Triggers

#### Sequence of Current Loop Triggers

# Control Loop Execution

$$u(n) = u_p(n) + u_i(n) + u_d(n)$$

where,

$u_p(n) = K_p^*e(n)$

$u_i(n) = K_i^*[e(n) + e(n-1)]$

$u_d(n) = K_d^*[e(n) - e(n-1)]$

### **Auxillary Tasks**

- 12V Bus Voltage Measurement

- Communication Routines

- Load Sharing Routines

- Temperature Measurement

- Power Management Routines

### **Demonstration #3**

**High Power Operation**

## **Enhanced Features**

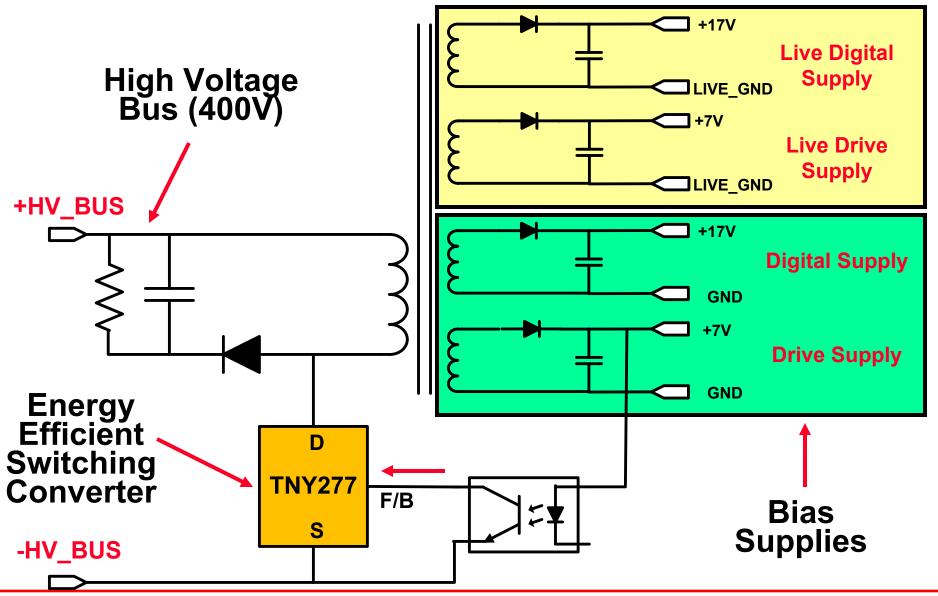

#### **PFC Sinusoidal Reference**

### **HV Bias Supply**

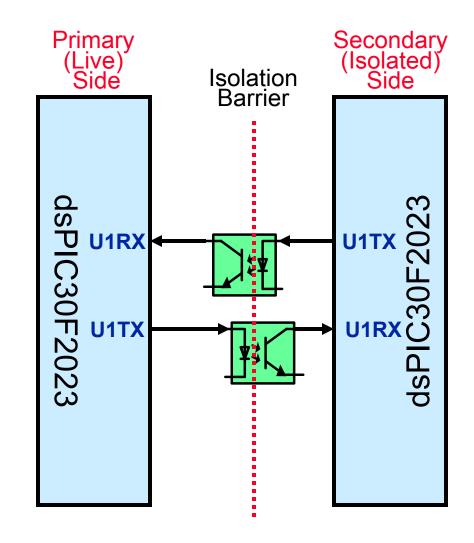

#### **DSC to DSC Communication**

- Perform status checks

- Report Fault Conditions to protect Hardware

- Implement Data Logging and Remote Monitoring

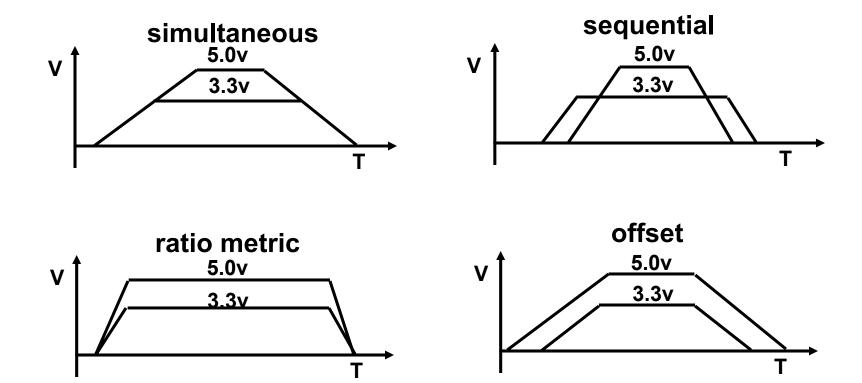

#### **Power Supply Sequencing**

Choose method that meets system requirements

#### **Output Protection Schemes**

- A number of protection schemes can be implemented

- Constant Current Limiting

- Constant Power Limiting

- Output Over-voltage Shutdown

- Input Under-voltage Shutdown

- All shutdown schemes can be configured for immediate or delayed shutdown

## Remote Monitoring Capability

Power monitoring can be implemented using a Serial I<sup>2</sup>C™ interface provided on the Secondary (Isolated) side

# Load Sharing Issues

- Multiple power modules share load

- Component and wiring differences cause some modules to work harder than others

- The heavily loaded modules get hotter and reliability drops causing failures – Domino Effect

#### **Benefits of Digital Control**

- Reduce Component Count

- Flexibility of Design

- Flexibility of Control

- Protect Intellectual Property

- Implement non-linear and adaptive control

- Control Multiple Stages

- Error logging capability

- Flexible Fault handling

#### Summary

- Overview of AC/DC Reference Design

- AC/DC Reference Design Architecture

- Power Factor Correction

- PFC Control Software

- Zero Voltage Transition

- ZVT Control Software

- Multi-phase Buck Converters

- Multi-phase Buck Control Software

- Enhanced Features

#### AC/DC Reference Design

- Availability

- Q4 2007

- Contact Local Sales office for more information

- Visit Microchip's Intelligent Power Supply Design Center for our full product offering

- www.microchip.com/smps

#### References

- C.K. Tse, "Circuit Theory of Power Factor Correction in switching converters"

- A. Hofmann, A.Baumuller, T. Gerhardt, M. Marz, E. Schimanek, "A robust digital PFC control method suitable for low-cost microcontroller"

- L. Rossetto, G.Spiazzi, P. Tenti, "Control Techniques for Power Factor Correction Converters"

- L.Rossetto, G.Spiazzi, "Design Considerations on Current-Mode and Voltage-Mode control methods for Half-Bridge Converters"

- W.Gu, J.Abu-Qahouq, S.Luo, I.Batarseh, "A ZVT-PWM single stage PFC converter with an active snubber"

- M. Brown, "Power Supply Cookbook"

- M. Kazimierczuk, D. Czarkowski, "Resonant Power Converters"

# Development Tools Used in this Class

#### Hardware Tools

- AC/DC Reference Design (not released)

- MPLAB® REAL ICE™ Emulator (DV244005)

- MPLAB ICD2 (DV164005)

#### Software Tools

- MPLAB IDE 7.61 (SW007002)

- MPLAB C30 v3.01 (SW006012)

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KeeLoq, KeeLoq logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A. All other trademarks mentioned herein are property of their respective companies.